#### THREAD VULNERABILITY FOR MULTICORE ARCHITECTURES

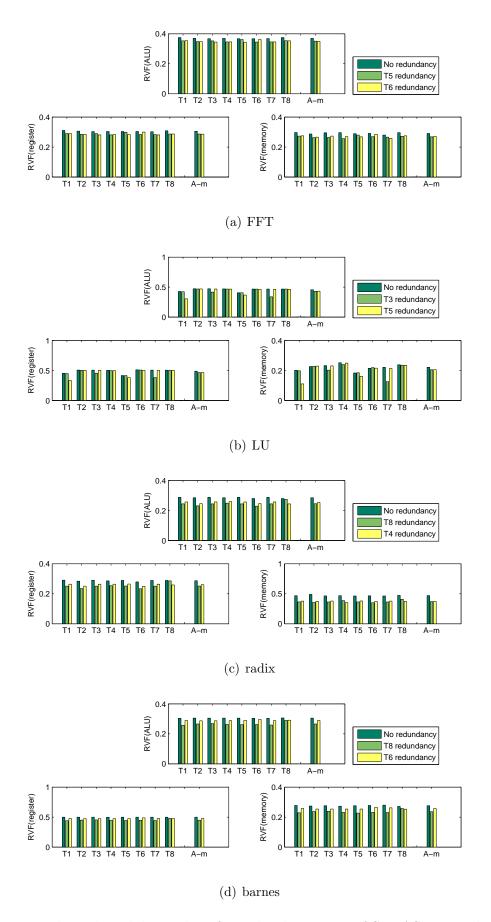

## by

## Işıl Öz

B.S., Computer Engineering, Marmara University, 2004M.S., Computer Engineering, Marmara University, 2008

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Graduate Program in Computer Engineering

Boğaziçi University

2013

## THREAD VULNERABILITY FOR MULTICORE ARCHITECTURES

## APPROVED BY:

| Prof. Oğuz Tosun          |     |

|---------------------------|-----|

| (Thesis Supervisor)       |     |

|                           |     |

| Prof. Haluk Rahmi Topçuoğ | ğlu |

| (Thesis Co-supervisor)    |     |

|                           |     |

| Prof. Can Özturan         |     |

|                           |     |

| Assoc. Prof. Alper Şen    |     |

|                           |     |

| Assist. Prof. Zeki Bozkuş |     |

DATE OF APPROVAL: 08.05.2013

## ACKNOWLEDGEMENTS

I would like to thank my advisors, Prof. Oğuz Tosun and Prof. Haluk Topçuoğlu for their academic support, guidance, and encouragement throughout my graduate study and the completion of this thesis. I would like to thank Prof. Mahmut Kandemir from Pennsylvania State University for his valuable feedback and guidance during my dissertation. I would also like to thank Prof. Can Özturan, Assoc. Prof. Alper Şen, and Assist. Prof. Zeki Bozkuş for serving my thesis committee.

I gratefully acknowledge the financial support of The Scientific and Technological Research Council of Turkey (TUBITAK) with a research grant (Project Number: 108E035). Additionally a partial fund is provided by The Marmara University Scientific Research Committee with a research grant (Project Number: FEN-A-200611-0210, 2011) and the Boğaziçi University Foundation (BUVAK).

I would like to thank my colleagues from the department of Computer Engineering at Marmara University for their support and friendship. In particular, I would like to thank Sanem Arslan Yılmaz, Berna Kiraz, Betül Demiröz Boz, Fatma Çorut Ergin, and Emel Küpçü, for their invaluable support throughout the years. I would also like to thank Fuat Geleri for his academic and technical support as well as his friendship.

I am grateful to my unique family; my mother Vahide Hasırcıoğlu, my father Ayhan Hasırcıoğlu for their endless love and great support during my dissertation like as during my whole life. Finally, I would like to thank my husband Dindar Öz for his patience, support, motivation, and everything that I cannot express with words.

## ABSTRACT

# THREAD VULNERABILITY FOR MULTICORE ARCHITECTURES

Continuously reducing transistor sizes and aggressive low power operating modes employed by modern architectures tend to increase transient error rates. A metric of reliability is required in order to evaluate approaches that address soft errors. This thesis explores a soft error vulnerability analysis of parallel applications running on multicore architectures. We propose and evaluate a novel metric, Thread Vulnerability Factor, in order to quantify thread vulnerability and to qualify the relative vulnerability of parallel applications to soft errors. We present the analytical definition of our metric, and develop a framework to calculate the metric value by gathering application data. To demonstrate the validity of the metric, fault injection based experiments are conducted for multithreaded applications. This thesis also presents the performancevulnerability analysis of parallel applications for a variety of applications and discusses the effects of design choices on system performance and reliability. By considering tradeoff between these two concerns, we observe that design choice becomes clear for some of the applications which provide different vulnerability values with almost equal performance. Additionally, we propose and evaluate reliability-aware core partitioning schemes for multicore architectures. A simulation study with various workloads consisting of multiple multithreaded applications is performed in order to evaluate the proposed partitioning schemes. We also present a thread-level vulnerability assessment tool by considering user preferences; and we propose a novel critical thread identification algorithm to determine critical thread and critical thread region in a multithreaded application. We utilize our algorithm to determine the thread for redundant execution in a partial fault tolerance system and demonstrate the efficiency of the method by providing vulnerability values for executions with different redundancy levels.

## ÖZET

# ÇOK ÇEKİRDEKLİ MİMARİLERDE İŞ PARÇACIĞI GÜVENİLİRLİĞİ

Modern işlemci teknolojisinde transistör boyutlarının gittikçe küçülmesi ve transistörlerin çok daha hızlı frekanslarda çalışması nedenleri ile, yonga bileşenlerinin geçici hata oranları artmaktadır. Geçici hatalar için sunulan çözümlerin değerlendirilmesi için bir güvenilirlik metriğine ihtiyaç duyulmaktadır. Bu tez, çok çekirdekli mimarilerde çalışan paralel uygulamaların geçici hata hassasiyetlerini incelemektedir. İlk olarak, iş parçacıklarının hata hassasiyetlerini ölçen ve paralel uygulamaların göreceli hata hassasiyetlerini belirleyen, İş Parçacığı Hasar Görebilirlik Faktörü olarak isimlendirdiğimiz bir metrik önerilmektedir. Çalışmamız kapsamında, metriğin analitik tanımı verilerek uygulama verisinden metrik değerini hesaplayacak bir yapı oluşturulmuştur. Metriğin doğrulanmasına yönelik olarak, paralel uygulamalar için hata enjeksiyon deneyleri uygulanmıştır. Bu tezde ayrıca, farklı problemlerin paralel uygulamaları için performanshata hassasiyeti analizi yapılarak farklı tasarım seçeneklerinin sistem performansı ve güvenilirliği üzerindeki etkileri incelenmiştir. Bu iki özelliği hesaba katarak yaptığımız analizler sonucunda, birbirine yakın performans değerlerine sahip ancak farklı hata hassasiyeti gösteren iki seçenek için tercih belirgin bir şekilde ortaya çıkmaktadır. Bu tez ayrıca, çok çekirdekli sistemler için güvenilirlik tabanlı çekirdek paylaştırma stratejileri önermektedir. Çekirdek paylaştırma stratejilerimizi değerlendirmek için, çok iş parçacıklı birden fazla uygulamadan oluşan iş yükleriyle deneysel çalışmalar vapılmıştır. Bu tezde ayrıca, iş parçacığı seviyesinde hassasiyet analizi yapılarak uygulamadaki kritik iş parçacığı ve iş parçacığı bölgesi tespiti için bir kritik iş parçacığı belirleme algoritması önerilmiştir. Bu algoritma, güvenilirliği arttırmak için kullanılan kısmi çoklama yönteminde en önemli kod parçacıklarının tespitinde kullanılmış, farklı çoklama seviyeleriyle ölçülen hassasiyet değerleriyle tekniğin etkinliği gösterilmiştir.

# TABLE OF CONTENTS

| AC  | CKNC  | WLED   | GEMENTS i                                                     |

|-----|-------|--------|---------------------------------------------------------------|

| ΑF  | BSTR  | ACT    |                                                               |

| ÖZ  | ZET . |        |                                                               |

| LIS | ST O  | F FIGU | JRES i                                                        |

| LIS | ST O  | F TAB  | LES                                                           |

| LIS | ST O  | F SYM  | BOLS                                                          |

| LIS | ST O  | F ACR  | ONYMS/ABBREVIATIONS xvi                                       |

| 1.  | INT   | RODU   | CTION                                                         |

|     | 1.1.  | Soft E | rror Resilience                                               |

|     | 1.2.  | Thesis | Contributions                                                 |

|     | 1.3.  | Outlin | e of the Thesis                                               |

| 2.  | THR   | READ V | ULNERABILITY FACTOR                                           |

|     | 2.1.  | Vulner | ability Metrics in the Literature                             |

|     |       | 2.1.1. | Architectural Vulnerability Factor (AVF)                      |

|     |       | 2.1.2. | Register Vulnerability Factor (RVF) 1                         |

|     |       | 2.1.3. | Instruction Vulnerability Factor (IVF)                        |

|     |       | 2.1.4. | Program Vulnerability Factor (PVF)                            |

|     | 2.2.  | Thread | d Vulnerability Factor (TVF)                                  |

|     |       | 2.2.1. | Formal Definition of Thread Vulnerability Factor              |

|     |       |        | 2.2.1.1. Local Vulnerability Factor (LVF)                     |

|     |       |        | 2.2.1.2. Remote Vulnerability Factor (RVF)                    |

|     |       | 2.2.2. | An Example for Calculating TVF Values of Multiple Threads . 2 |

|     | 2.3.  | Experi | mental Setup                                                  |

|     |       | 2.3.1. | Simulation Platform                                           |

|     |       | 2.3.2. | Benchmarks                                                    |

|     | 2.4.  | Experi | mental Results                                                |

|     |       | 2.4.1. | TVF Results                                                   |

|     |       | 2.4.2. | Weight Analysis                                               |

|     |       | 2.4.3. | Cache Size Variation                                          |

| 3. | VAL  | IDATII | NG THREAD VULNERABILITY FACTOR                     | 49 |

|----|------|--------|----------------------------------------------------|----|

|    | 3.1. | An Ov  | verview on Fault Injection                         | 49 |

|    | 3.2. | TVF V  | Validation by Using Simics Environment             | 50 |

|    |      | 3.2.1. | Fault Injection Framework                          | 51 |

|    |      | 3.2.2. | Experiments on the Simics Environment              | 53 |

|    | 3.3. | TVF V  | Validation on a Multicore Architecture             | 56 |

|    |      | 3.3.1. | Pin Overview                                       | 56 |

|    |      | 3.3.2. | Experiments on the Multicore Architecture          | 57 |

| 4. | PER  | FORM   | ANCE-RELIABILITY ANALYSIS OF MULTITHREADED AP-     |    |

|    | PLIC | CATIO  | NS                                                 | 61 |

|    | 4.1. | Multit | chreaded Applications                              | 61 |

|    |      | 4.1.1. | Fast Fourier Transform                             | 61 |

|    |      | 4.1.2. | Jacobi Kernel                                      | 65 |

|    |      | 4.1.3. | Water Simulation                                   | 66 |

|    | 4.2. | Experi | imental Results                                    | 69 |

| 5. | REL  | IABILI | ITY-AWARE CORE PARTITIONING FOR MULTICORE ARCHI-   |    |

|    | TEC  | TURE   | S                                                  | 77 |

|    | 5.1. | An Ov  | verview on Core Partitioning                       | 77 |

|    | 5.2. | Reliab | oility-Aware Core Partitioning                     | 80 |

|    |      | 5.2.1. | Equal Partitioning                                 | 82 |

|    |      | 5.2.2. | Reliability-Oriented Partitioning                  | 82 |

|    |      | 5.2.3. | Performance-Oriented Partitioning                  | 83 |

|    |      | 5.2.4. | Partitioning Based on a Combined Metric            | 84 |

|    | 5.3. | Experi | imental Evaluation                                 | 86 |

|    |      | 5.3.1. | Workload Construction                              | 87 |

|    |      | 5.3.2. | Performance and Reliability Metrics                | 91 |

|    |      | 5.3.3. | Evaluating Partitioning Schemes                    | 92 |

|    |      |        | 5.3.3.1. Performance-Reliability Tradeoff Analysis | 92 |

|    |      |        | 5.3.3.2. Detailed Workload Analysis                | 96 |

|    |      | 5.3.4. | Sensitivity Analysis                               | 98 |

|    |      |        | 5.3.4.1. Initial Core Assignment                   | 98 |

|    |      |        | 5.3.4.2.    | The Number of Applications in the Workload $\dots$ . | 101 |

|----|------|--------|-------------|------------------------------------------------------|-----|

|    |      |        | 5.3.4.3.    | The Number of Cores in the System                    | 103 |

| 6. | PAR  | TIAL 1 | FAULT T     | OLERANCE BASED ON THREAD-LEVEL VULNERA               | _   |

|    | BIL  | ITY AS | SESSME      | NT                                                   | 106 |

|    | 6.1. | An Ov  | verview o   | n Fault Tolerance Techniques                         | 106 |

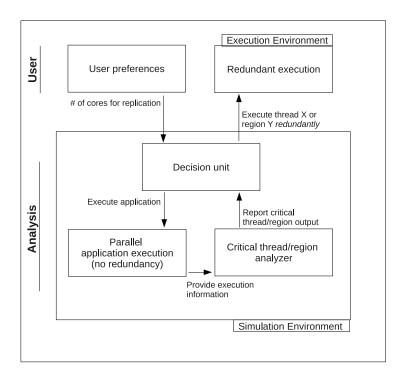

|    | 6.2. | Motiv  | ation       |                                                      | 109 |

|    | 6.3. | Threa  | d-Level R   | eliability Assessment                                | 112 |

|    |      | 6.3.1. | System      | Design and Overview                                  | 112 |

|    |      | 6.3.2. | Critical    | Thread Replication                                   | 113 |

|    |      |        | 6.3.2.1.    | Thread Vulnerability                                 | 113 |

|    |      |        | 6.3.2.2.    | Thread Interactions                                  | 114 |

|    |      |        | 6.3.2.3.    | Critical Thread Identification Algorithm             | 117 |

|    |      |        | 6.3.2.4.    | An Example Execution                                 | 119 |

|    |      | 6.3.3. | Critical    | Region Replication                                   | 120 |

|    | 6.4. | Vulner | rability of | Redundant Computations                               | 122 |

|    |      | 6.4.1. | Vulneral    | pility Evaluation                                    | 122 |

|    |      | 6.4.2. | A Case      | Study                                                | 124 |

|    | 6.5. | Bench  | mark App    | plications                                           | 125 |

|    | 6.6. | Exper  | imental R   | tesults                                              | 126 |

|    |      | 6.6.1. | Evaluati    | ng Critical Thread Replication                       | 127 |

|    |      |        | 6.6.1.1.    | Critical Thread Analysis                             | 127 |

|    |      |        | 6.6.1.2.    | Critical Thread Replication                          | 129 |

|    |      |        | 6.6.1.3.    | Validation of Critical Thread Replication            | 133 |

|    |      | 6.6.2. | Evaluati    | ng Critical Region Replication                       | 136 |

| 7. | CON  | NCLUS: | IONS AN     | D FUTURE WORK                                        | 141 |

| RF | EFER | ENCES  | 3           |                                                      | 144 |

# LIST OF FIGURES

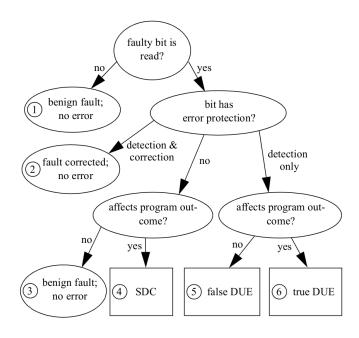

| Figure 1.1.  | Possible outcomes of a single-bit fault [1]                                        | 2  |

|--------------|------------------------------------------------------------------------------------|----|

| Figure 2.1.  | A set of program instructions and the resulting hardware operations [2]            | 15 |

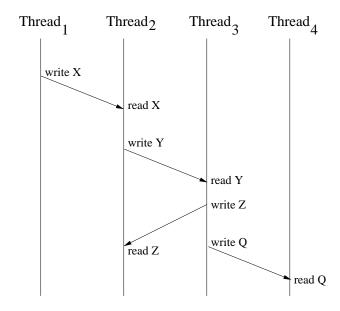

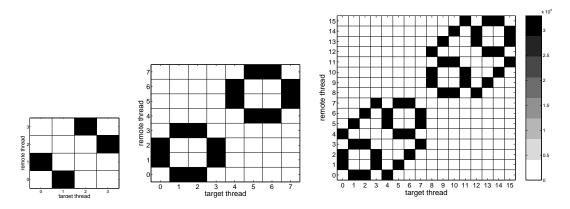

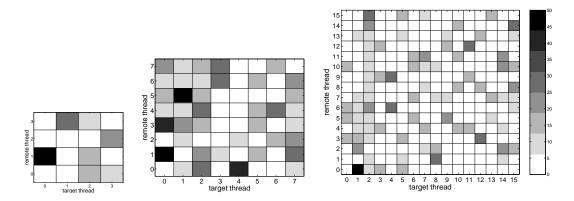

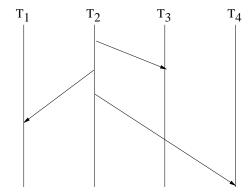

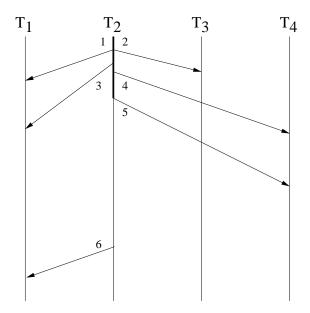

| Figure 2.2.  | Data sharing between four threads                                                  | 17 |

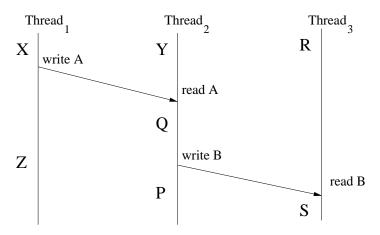

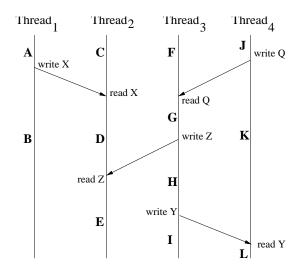

| Figure 2.3.  | An example for representing data sharing between threads                           | 23 |

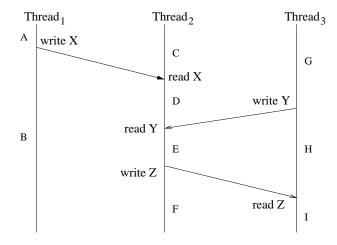

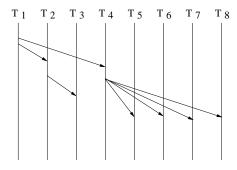

| Figure 2.4.  | An example for more complex data sharing scenario                                  | 25 |

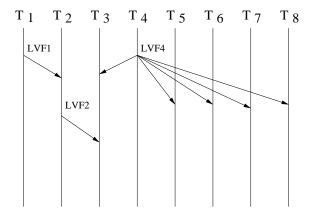

| Figure 2.5.  | The communication of four threads in a multithreaded application.                  | 27 |

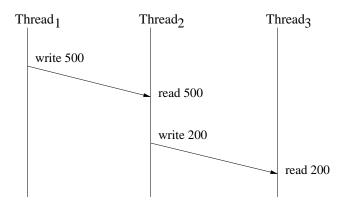

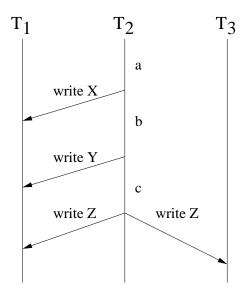

| Figure 2.6.  | Data flow among three threads for the sample code given in Table 2.2               | 29 |

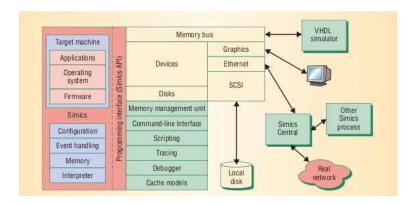

| Figure 2.7.  | Simics architecture [3]                                                            | 32 |

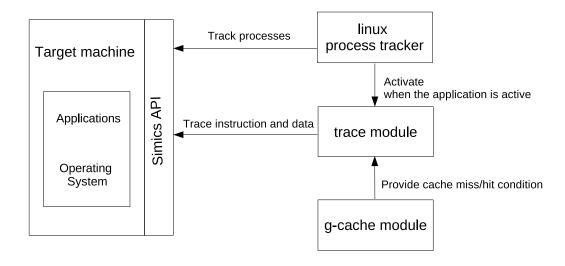

| Figure 2.8.  | Simics architecture used in our experiments                                        | 34 |

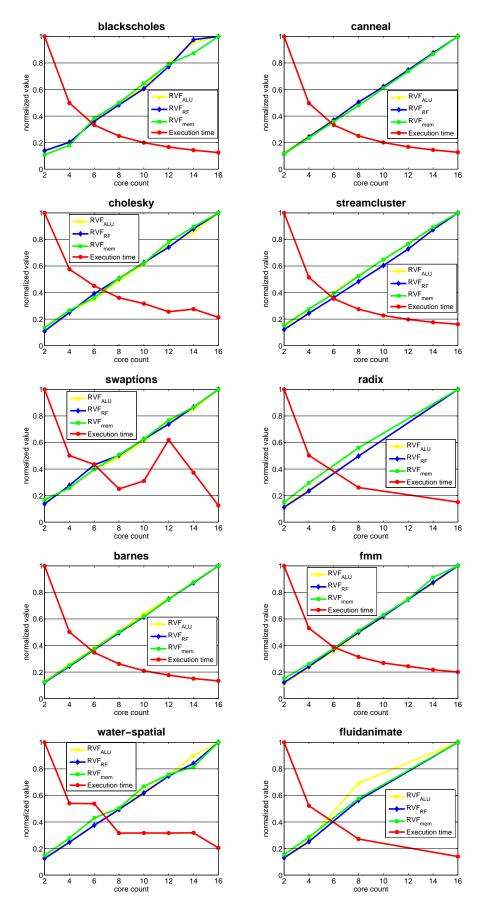

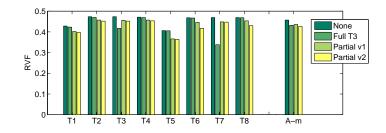

| Figure 2.9.  | Normalized RVF values and normalized execution times of our benchmark applications | 43 |

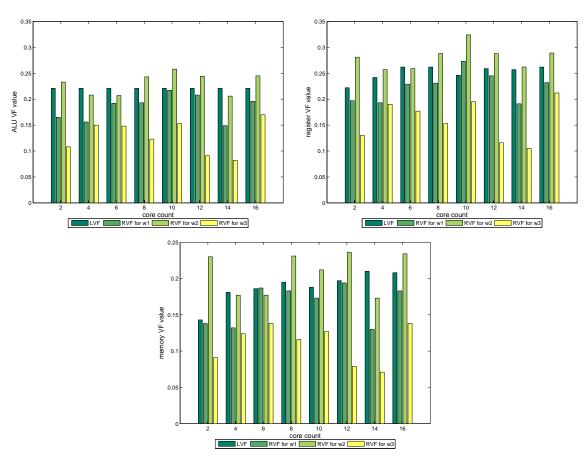

| Figure 2.10. | RVF values with different vulnerability weights ( $blackscholes$ )                 | 44 |

| Figure 2.11. | RVF values with different vulnerability weights ( $cholesky$ )                     | 46 |

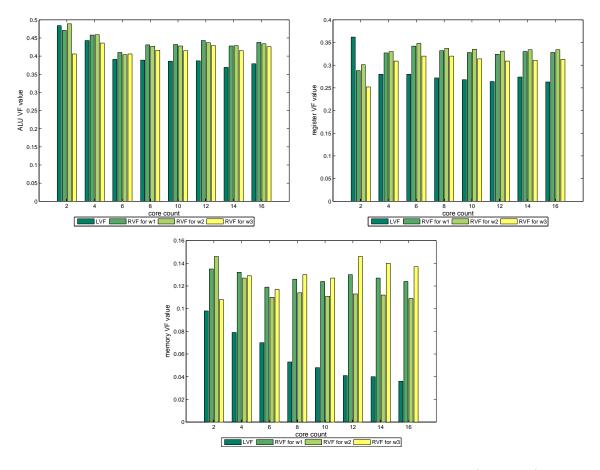

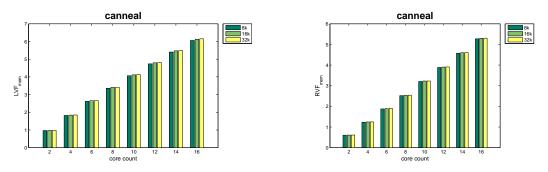

| Figure 2.12. | Memory TVF values for <i>canneal</i> with different cache sizes                    | 47 |

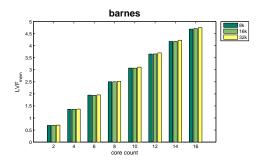

| Figure 2.13. | Memory TVF values for barnes with different cache sizes                                                        | 48 |

|--------------|----------------------------------------------------------------------------------------------------------------|----|

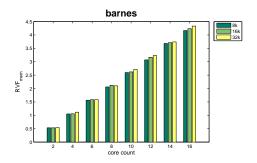

| Figure 3.1.  | Our fault injection framework, where the numbers in the arrows represent the flow of our one experiment        | 51 |

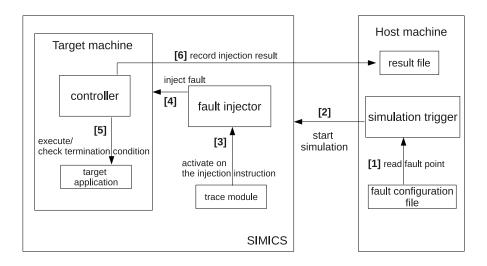

| Figure 3.2.  | Fault injection experiment results for 4 benchmark applications. $$ .                                          | 53 |

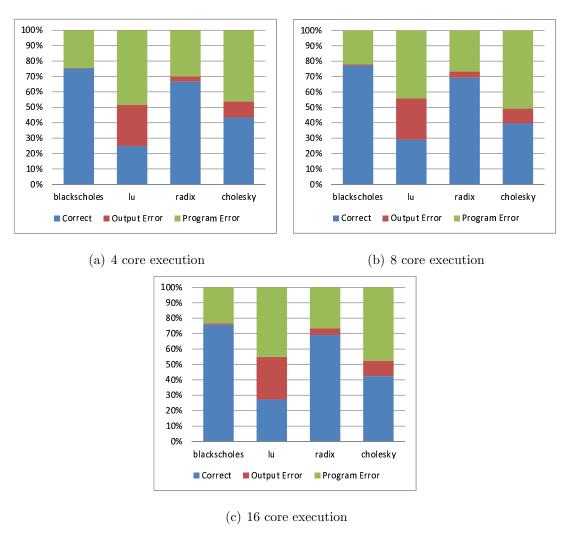

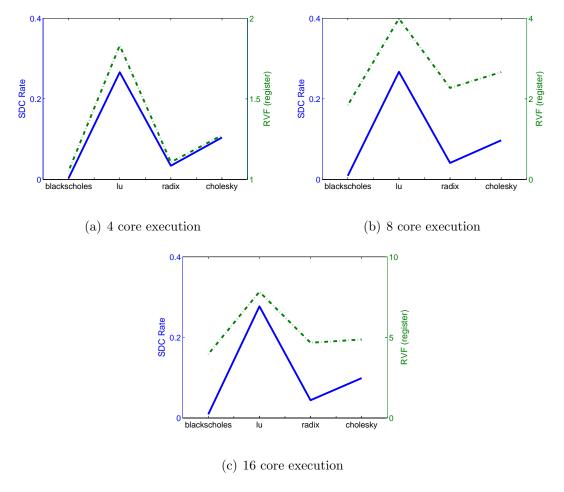

| Figure 3.3.  | Vulnerability values (SDC rate and RVF value) for 4 benchmark applications                                     | 55 |

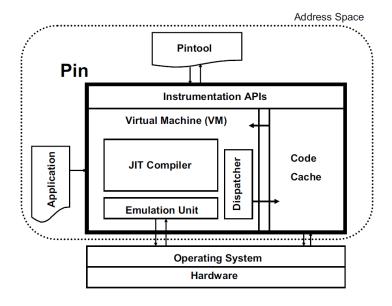

| Figure 3.4.  | Pin's software architecture [4]                                                                                | 57 |

| Figure 3.5.  | Pintool for printing addresses of all program memory reads and writes                                          | 58 |

| Figure 3.6.  | Fault insertion analysis routine                                                                               | 59 |

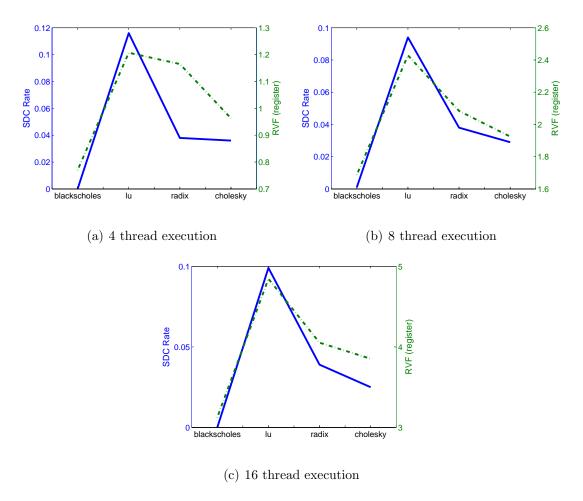

| Figure 3.7.  | Vulnerability values (SDC rate and RVF value) for 4 benchmark applications running on our 16-core architecture | 60 |

| Figure 4.1.  | The Cooley-Tukey algorithm for one-dimensional, unordered, radix-2 FFT [5]                                     | 63 |

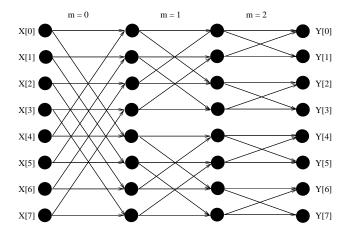

| Figure 4.2.  | The pattern of combination of input array elements in an 8-point FFT computation                               | 63 |

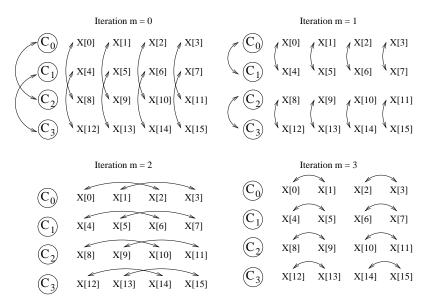

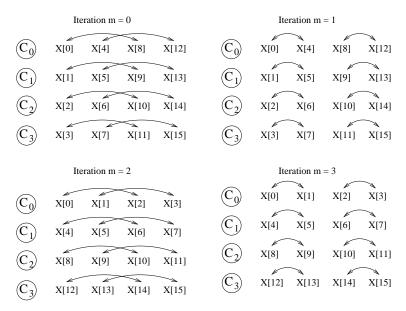

| Figure 4.3.  | Binary-exchange algorithm for a 16-point FFT on four cores                                                     | 64 |

| Figure 4.4.  | Transpose algorithm for a 16-point FFT on four cores                                                           | 65 |

| Figure 4.5.  | 2-D Jacobi code                                                                                                | 66 |

| Figure 4.6.  | Unrolled 2-D Jacobi code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.7.  | Fused 2-D Jacobi code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68 |

| Figure 4.8.  | Interchanged 2-D Jacobi code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68 |

| Figure 4.9.  | RVF contribution of each thread for binary-exchange algorithm. $% \left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( $ | 72 |

| Figure 4.10. | RVF contribution of each thread for transpose algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72 |

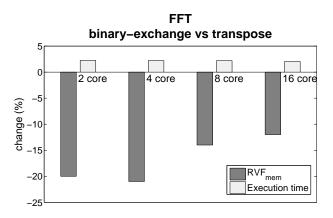

| Figure 4.11. | The change in percentage of RVF values and execution time for versions of FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 74 |

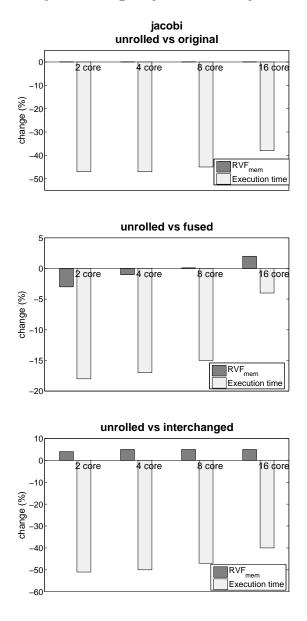

| Figure 4.12. | The change in percentage of RVF values and execution time for loop transformations of Jacobi code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 75 |

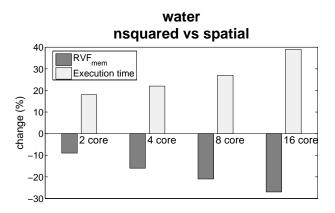

| Figure 4.13. | The change in percentage of RVF values and execution time for versions of water simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76 |

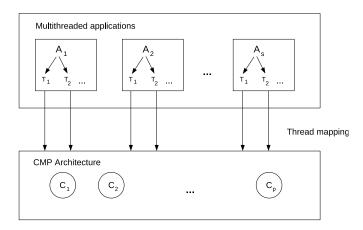

| Figure 5.1.  | System architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81 |

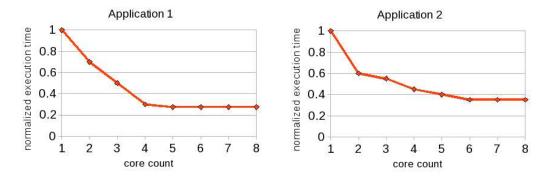

| Figure 5.2.  | Example execution time/core count behavior of two applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83 |

| Figure 5.3.  | Basic partitioning algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 85 |

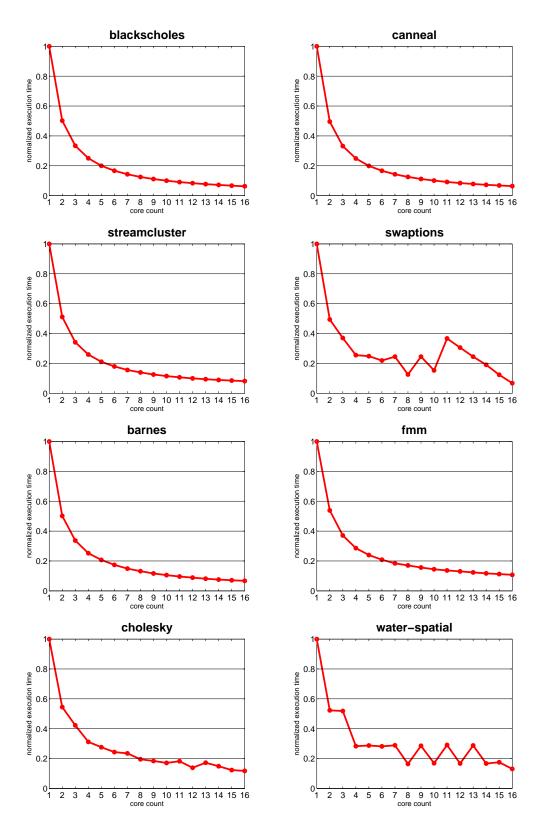

| Figure 5.4.  | Normalized execution time of our benchmark applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88 |

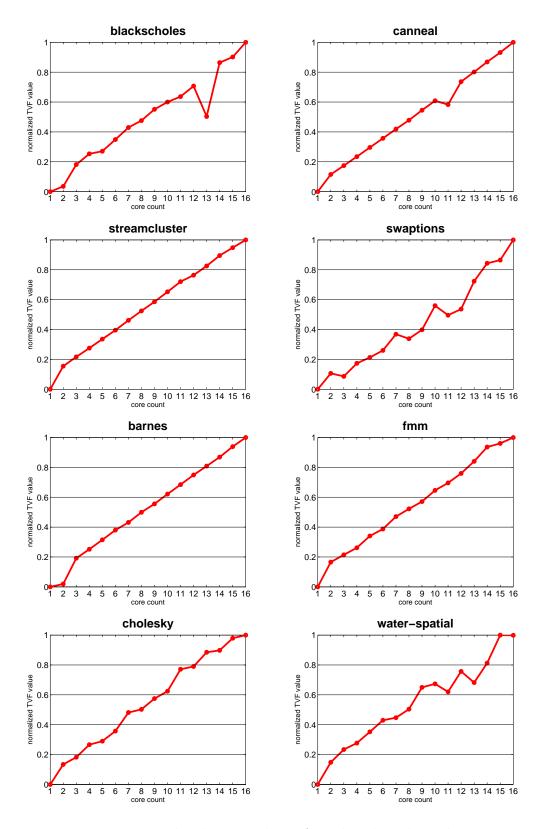

| Figure 5.5.  | Normalized TVF values of our benchmark applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 89 |

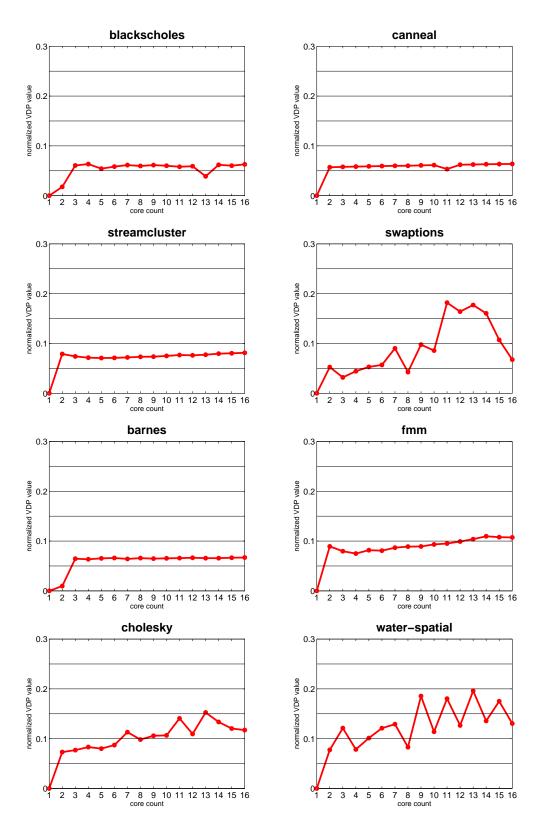

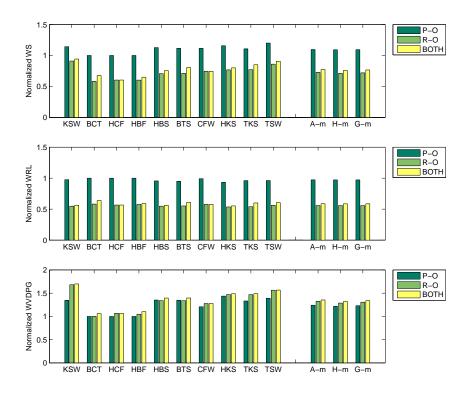

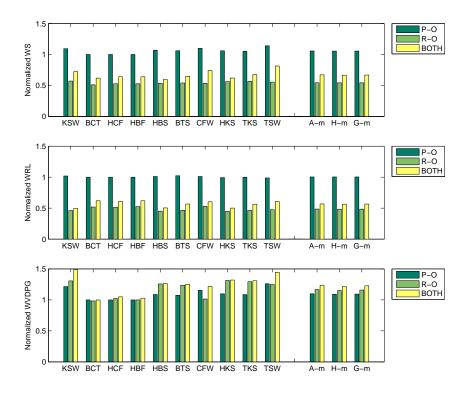

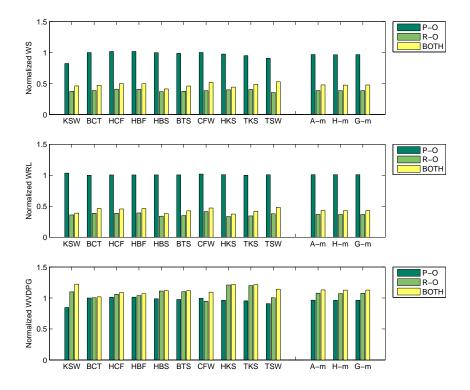

| Figure 5.6.  | Normalized VDP values of our benchmark applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90 |

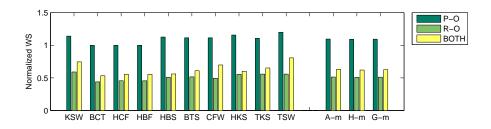

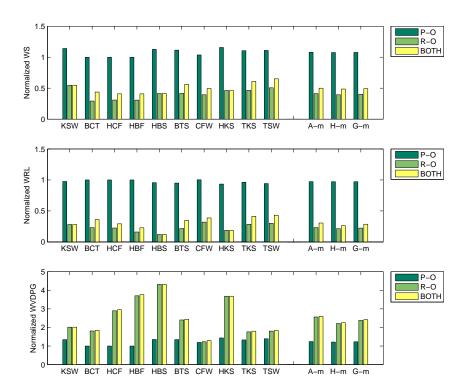

| Figure 5.7.  | Normalized weighted-speedup values of partitioning schemes to equal core partitioning for selected 10 workloads                               | 94  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.8.  | Normalized weighted-reliability loss values of partitioning schemes to equal core partitioning for selected 10 workloads                      | 94  |

| Figure 5.9.  | Normalized weighted-vulnerability-delay product gain values of partitioning schemes to equal core partitioning for selected 10 workloads.     | 94  |

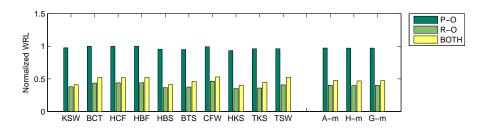

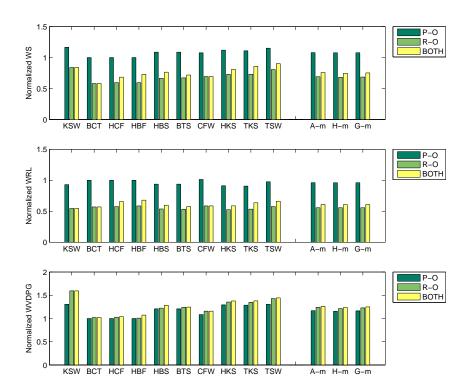

| Figure 5.10. | NWS, NWRL and NWVDPG values of partitioning schemes to equal core partitioning for selected 10 workloads with 2 core initial assignment.      | 99  |

| Figure 5.11. | NWS, NWRL and NWVDPG values of partitioning schemes to equal core partitioning for selected 10 workloads with 4 core initial assignment       | 100 |

| Figure 5.12. | NWS, NWRL and NWVDPG values of partitioning schemes to equal core partitioning for selected 10 workloads with 3, 4, 5 core initial assignment | 100 |

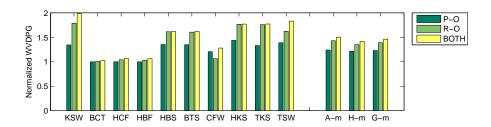

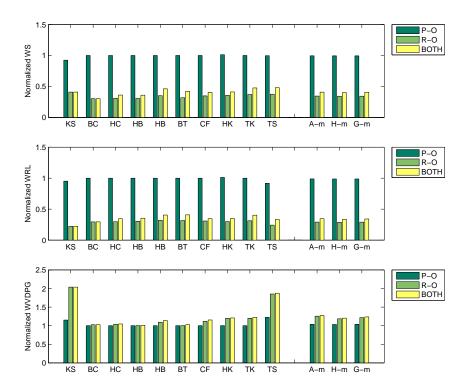

| Figure 5.13. | NWS, NWRL and NWVDPG values of partitioning schemes to equal core partitioning for 2-application workloads                                    | 101 |

| Figure 5.14. | NWS, NWRL and NWVDPG values of partitioning schemes to equal core partitioning for 4-application workloads                                    | 102 |

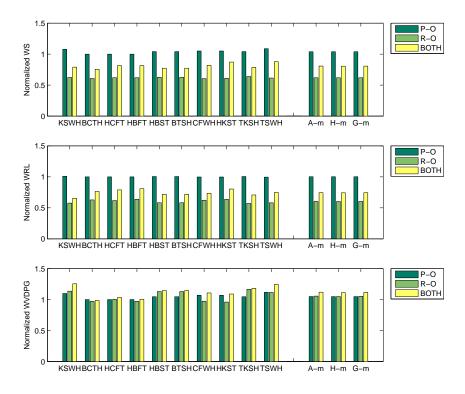

| Figure 5.15. | NWS, NWRL and NWVDPG values of partitioning schemes to equal core partitioning for 18-core system                                             | 104 |

| Figure 5.16. | NWS, NWRL and NWVDPG values of partitioning schemes to equal core partitioning for 24-core system. | 104  |

|--------------|----------------------------------------------------------------------------------------------------|------|

| Figure 6.1.  | Sample data distribution                                                                           | 111  |

| Figure 6.2.  | Flow of our reliability assessment tool                                                            | 113  |

| Figure 6.3.  | Thread interaction graph with four threads                                                         | 115  |

| Figure 6.4.  | Thread behavior of an 8-thread application                                                         | 115  |

| Figure 6.5.  | An example thread interaction graph which has multiple remote write operations of a single thread. | 116  |

| Figure 6.6.  | Algorithm for calculating direct and indirect criticality degree values of threads                 | 118  |

| Figure 6.7.  | Algorithm for determining critical thread of an application                                        | 119  |

| Figure 6.8.  | A thread interaction graph with 8 threads                                                          | 120  |

| Figure 6.9.  | A TIG example to represent synchronization of thread regions                                       | 122  |

| Figure 6.10. | TIG for thread replication case                                                                    | 123  |

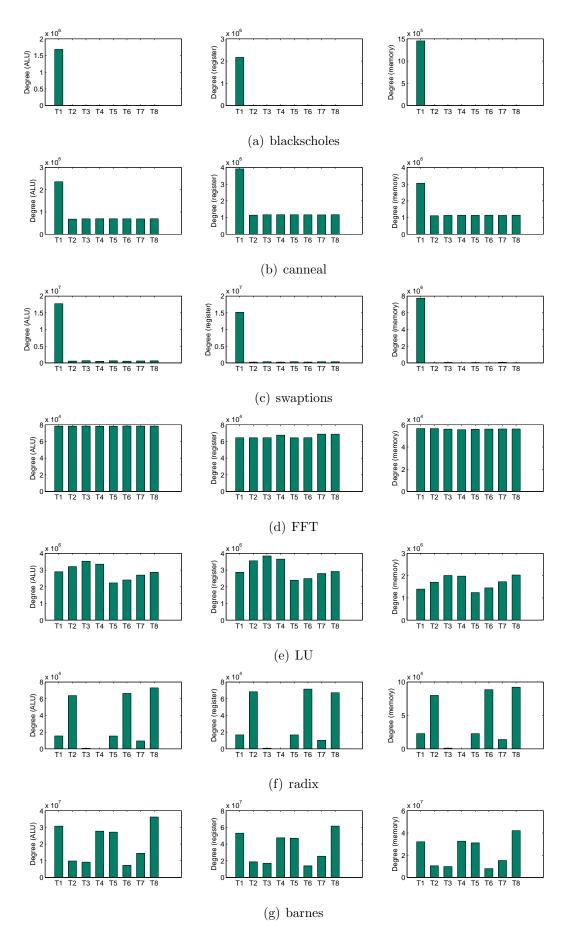

| Figure 6.11. | Metric values for benchmark applications                                                           | 128  |

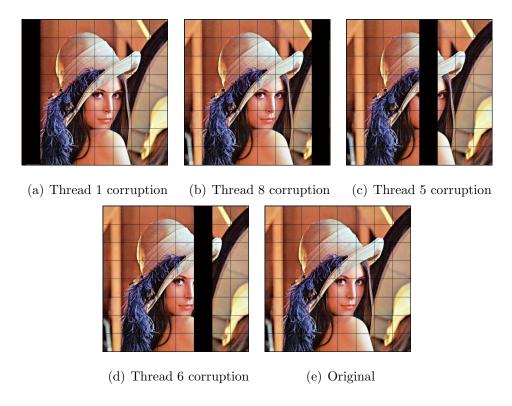

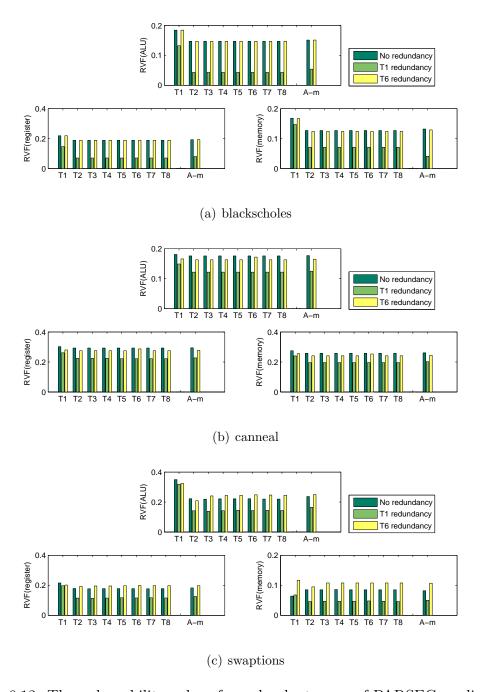

| Figure 6.12. | The vulnerability values for redundant cases of PARSEC applications                                | .130 |

| Figure 6.13. | The vulnerability values for redundant cases of SPLASH-2 applications                              | 132  |

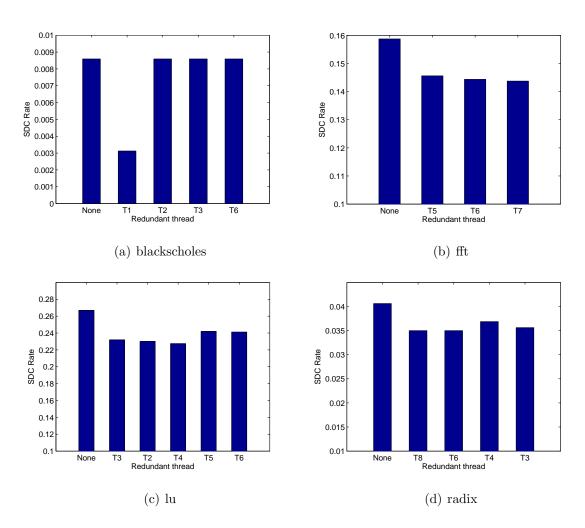

| Figure 6.14. | SDC rates for redundant cases                                                | 134 |

|--------------|------------------------------------------------------------------------------|-----|

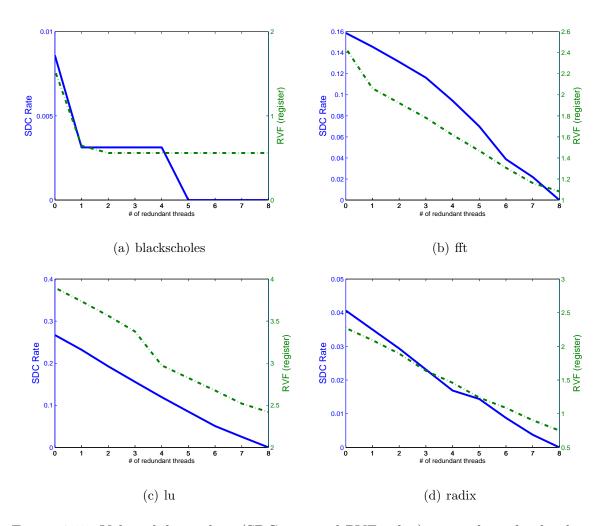

| Figure 6.15. | Vulnerability values (SDC rate and RVF value) vs number of redundant threads | 135 |

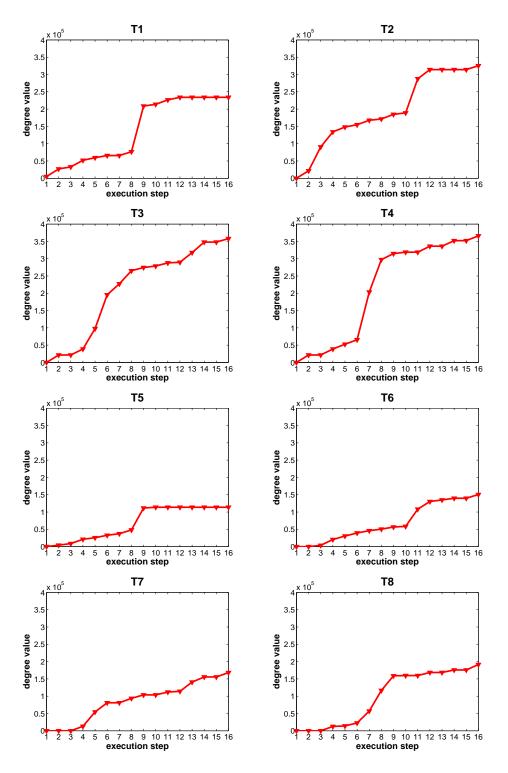

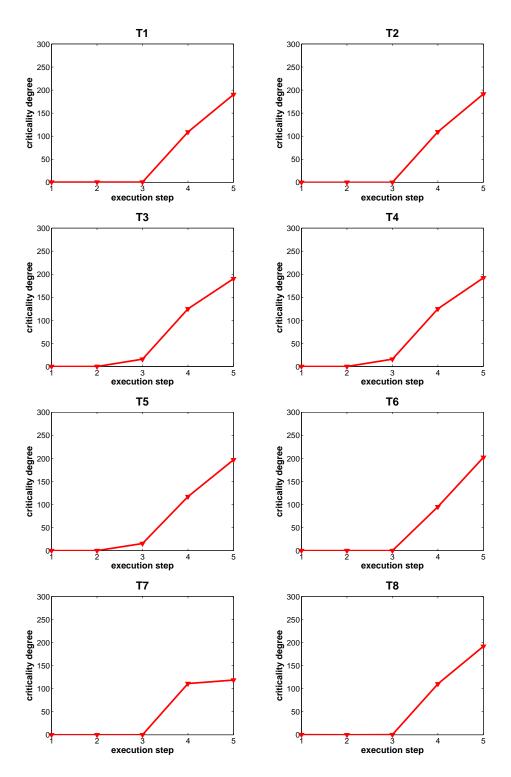

| Figure 6.16. | Metric values of LU execution steps for distinct threads                     | 137 |

| Figure 6.17. | Vulnerability values for partially redundant cases of lu application.        | 138 |

| Figure 6.18. | Metric values of FFT execution steps for distinct threads                    | 139 |

# LIST OF TABLES

| Table 2.1. | Memory location access of two threads                                                  | 24  |

|------------|----------------------------------------------------------------------------------------|-----|

| Table 2.2. | A sample code for TVF calculation                                                      | 29  |

| Table 2.3. | Parameters of the simulated multicore architecture                                     | 33  |

| Table 2.4. | Sample memory accesses of a thread                                                     | 35  |

| Table 2.5. | A sample communication of two threads                                                  | 35  |

| Table 2.6. | TVF values of our PARSEC benchmark applications for 2-core and 4-core executions.      | 39  |

| Table 2.7. | TVF values of our SPLASH-2 benchmark applications for 2-core and 4-core executions     | 40  |

| Table 3.1. | Characteristics of our workstation environment                                         | 59  |

| Table 4.1. | TVF values and execution time of our benchmark applications                            | 70  |

| Table 5.1. | NWS, NWRL and NWVDPG mean values among 56 workloads for core partitioning schemes      | 93  |

| Table 6.1. | Matrix for direct and indirect criticality degree values for critical thread analysis. | 121 |

| Table 6.2. | Metric values for critical thread analysis of synthetic application                    | 124 |

Table 6.3. RVF values of redundant executions of synthetic application. . . . 126

## LIST OF SYMBOLS

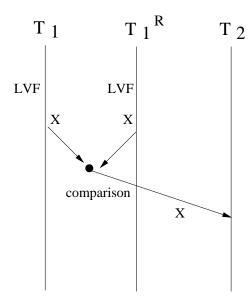

$LVF(T_i)$  Local vulnerability factor for thread i