# Precise Event Sampling: In-depth Analysis and Sampling-based Profiling Tools for Data Locality

by

#### Muhammad Aditya Sasongko

A Dissertation Submitted to the Graduate School of Sciences and Engineering in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

in

Computer Science and Engineering

# Precise Event Sampling: In-depth Analysis and Sampling-based Profiling Tools for Data Locality

#### Koç University

Graduate School of Sciences and Engineering

This is to certify that I have examined this copy of a doctoral dissertation by

#### Muhammad Aditya Sasongko

and have found that it is complete and satisfactory in all respects, and that any and all revisions required by the final examining committee have been made.

| Committe | ee Members:                        |

|----------|------------------------------------|

|          |                                    |

|          | Assist. Prof. Didem Unat (Advisor) |

|          | Prof. Öznur Özkasap                |

|          | Assoc. Prof. Aykut Erdem           |

|          | Assist. Prof. Ayşe Yılmazer        |

|          | Prof. Özcan Öztürk                 |

|          |                                    |

Date:

To my mother, wife Riana, and daughter Sofia

#### ABSTRACT

Precise Event Sampling: In-depth Analysis and Sampling-based

Profiling Tools for Data Locality

Muhammad Aditya Sasongko

Doctor of Philosophy in Computer Science and Engineering

February 2, 2022

Precise event sampling is a profiling feature in current commodity CPUs that allows sampling of hardware events and identifies the instructions that trigger the sampled events. It offers the ability to detect performance bottlenecks with low overhead as well as the locations of the bottlenecks in source code. There have been a number of profiling tools developed using this feature that detect various sources of performance bottlenecks. However, none of these tools detects inter-thread data movement nor measures data locality in multithreaded applications, which have become widely used due to the ubiquity of multicore architectures. Furthermore, though this hardware facility has been used in multiple profiling tools, there have been only few works that analyze it in terms of accuracy and overhead. All of these works target only the facility in Intel architecture, and none of these works evaluates other aspects of precise event sampling such as memory overhead, stability, and functionality of the facility.

In this dissertation, we present threefold major contributions. First, we perform the most comprehensive and in-depth qualitative and quantitative analyses to date on PEBS and IBS, which are the precise event sampling facilities of two major vendors, Intel and AMD, respectively. Next, we show the potential for imaginative use of precise event sampling in developing low overhead yet accurate profiling tools for multicore and design two diagnostic tools with a particular focus on data movement as it constitutes the main source of inefficiencies. First of such tools is COMDETECTIVE that detects inter-thread communications, classifies them into true sharing or false sharing, and records them in the form of communication matrices. Second is Reusetracker that measures data locality in private and shared caches of multithreaded applications. ComDetective and Reusetracker leverage pre-

cise event sampling to profile multithreaded applications accurately and with low overheads compared to their state-of-the-art alternatives.

To analyze key differences between Intel PEBS and AMD IBS, we firstly developed a series of carefully designed microbenchmarks. Through our qualitative analysis and quantitative study using the microbenchmarks, we found that Intel PEBS samples hardware events more accurately and with higher stability in terms of the number of samples that it captures, while AMD IBS records richer set of information at each sample. We also discovered that both PEBS and IBS are afflicted with bias when sampling the same event across multiple different instructions in a code. Moreover, we also show how our findings from the quantitative experiments using the microbenchmarks are relevant for a full-fledged profiling tool that runs on Intel and AMD machines.

We develop Comdetective, a profiling tool that captures inter-thread communications accurately and with low runtime and memory overheads. Comdetective employs precise event sampling to sample memory accesses and utilizes hardware debug registers to detect inter-thread communications. In addition to detecting communications, Comdetective can also classify them into true or false sharing. Its time and memory overheads are only  $1.30\times$  and  $1.27\times$ , respectively, for the 18 applications studied under 500K sampling interval. Using Comdetective, we generate insightful communication matrices from several microbenchmarks, PARSEC benchmark suite, and some CORAL applications and compare the produced matrices against the matrices of their MPI counterparts. Using Comdetective, we identify communication bottlenecks in a few codes and achieve up to 13% speedup from code refactoring those codes.

We also design ReuseTracker, which is a profiling technique that measures reuse distance – a widely used metric that measures data locality. Reuse distance is a measurement of data locality as it is the number of unique memory locations that are accessed between two consecutive accesses to a particular memory location (use and reuse). ReuseTracker leverages precise event sampling to capture uses and debug registers to detect reuse in measuring reuse distance. ReuseTracker can measure reuse distance in multithreaded applications by also considering cache-coherence effects with much lower overheads than existing tools. It introduces only  $2.9 \times 1.00$  time and  $2.8 \times 1.00$  memory overheads. It achieves 92% accuracy when verified against a carefully crafted configurable microbenchmark that can generate user-specified reuse

distance patterns. We demonstrate in two use cases how ReuseTracker can be used to guide code refactoring by detecting spatial reuses in shared caches that are also false sharing and how it can also be used to predict whether certain applications can benefit from adjacent cache line prefetch optimization.

We expect that the analysis, algorithms, and the tools presented in this dissertation will benefit hardware architects in designing new precise event sampling features and performance engineers in performance tuning of their software while also paving the way for a new generation of low-overhead profiling tools. Moreover, the outcomes of the dissertation can be used by the end-users (e.g., data analysts, engineers, compiler developer) to identify the performance issues and increase the data locality aspects of their software.

### ÖZETÇE

# Kesin Olay Örnekleme: Derinlemesine Analiz ve Örneklemeye Dayalı Veri Konumu için Profil Oluşturma Araçları Muhammad Aditya Sasongko Bilgisayar Bilimleri ve Mühendisliği, Doktora 13 Ocak 2022

Kesin olay örneklemesi, mevcut emtia işlemcilerde bulunan, donanımsal olayların örneklenmesinde ve bu olayların tetiklenmesine sebep olan komutların tanımlanmasını sağlayan bir profilleme özelliğidir. Bu özellik sayesinde, performans darboğazları düşük ek masraf ile saptanabilir ve bu darboğazların kaynak koddaki yerleri belirlenebilir. Çeşitli performans darboğazlarını belirlemek üzere birkaç profilleme aracı geliştirilmiştir. Ancak bu araçlardan hiçbiri, iş parçacıkları arasındaki veri hareketini belirleyemez, veya çok iş parçacıklı uygulamalarda veri yerelliğini ölçemez. Ek olarak, bu donanım özelliği birçok profilleme aracında kullanılmış olsa da, bu özelliğin doğruluğu ve masrafı analiz eden çok az çalışma vardır. Tüm bu çalışmalar sadece Intel mimarisine yöneliktir; ve bunlardan hiçbiri bu donanım özelliğinin hafıza masrafı, stabilite, ve fonksiyonellik taraflarını değerlendirmemiştir.

Bu tezde, üç-yönlü büyük katkı öne sürülmüştür. İlk olarak, sırasıyla Intel ve AMD'nin kesin olay örneklemesi araçları olan PEBS ve IBS üzerinde derinlemesine nitel ve nicel analiz yapılmıştır. İkinci olarak, iş parçacıkları arasında haberleşmeyi saptayabilen ve bunları true-sharing ve false-sharing olarak sınıflandırıp haberleşme matrislerinde kaydedebilen bir profilleme aracı olan ComDetective öne sürülmüştür. Üçüncü olarak, çok iş parçacıklı uygulamalarda özel önbellek ve paylaşılan önbellek içerisinde veri yerelliğini ölçebilen bir profilleme aracı olan Reusetracker öne sürülmüştür. ComDetective ve Reusetracker, kesin olay örneklemesi kullanarak yüksek doğruluk oranı ve düşük ek masraf ile çok iş parçacıklı uygulamaları profilleyebilmektedir.

Intel PEBS ve AMD IBS arasındaki kilit farkları analiz edebilmek adına, ilk olarak bir dizi dikkatle tasarlanmış microbenchmark geliştirilmiştir. Bu microbenchmarklar ile yapılan nicel analiz ve nitel çalışmalar sonucunda, Intel PEBS'in do-

nanımsal olayları örneklem sayısı bakımından daha yüksek doğruluk ve stabilite ile örnekleyebildiği gözlemlenirken; AMD IBS'in ise bilgi bakımından daha kapsamlı örnekleme yaptığı görülmüştür. Ek olarak, PEBS ve IBS'in farklı komutlar üzerinde aynı donanım olayını örneklerken kötü yönde etkilendiği gözlemlenmiştir. Dahası, elde edilen deney sonuçlarımızın Intel ve AMD makinelerinde çalışabilecek tam teşekküllü bir profilleme aracı bağlamında ilişkilendirilmesi gösterilmiştir.

Intel PEBS ve AMD IBS'in incelenmesinden sonra, iş parçacıkları arasındaki haberleşmeyi yüksek doğruluk, düşük ek masraf düşük çalışma zamanı ile saptayabilen bir profilleme aracı olan ComDetective öne sürülmüştür. ComDetective kesin olay örneklemesi ile hafıza erişimlerine örnekleyerek ve donanımsal debug yazmaçlarını kullanarak iş parçacıkları arasındaki haberleşmeleri saptayabilmektedir. Haberleşmeyi saptamaya ek olarak, ComDetective bu haberleşmeleri truesharing ve false-sharing olarak sınıflandırabilmektedir. 18 farklı uygulamada 500K örnekleme aralığı ile çalıştırıldığında, ComDetective'nin sırasıyla zaman ve hafıza ek masrafları sadece 1.30times ve 1.27times olarak ölçülmüştür. ComDetective kullanarak, birkaç microbenchmark, PARSEC benchmark koleksiyonu ve bazı CORAL uygulamaları için haberleşme matrisleri oluşturulmuş, ve bu matrisler MPI karşıtları ile karşılaştırılmıştır. Bu sayede bazı uygulamalarda haberleşme darboğazları keşfedilmiş olup, düzeltilmeleriyle beraber 13%'e kadar hızlanma başarılmıştır.

Ek olarak, bir veri yerelliği ölçütü olarak sıkça kullanılan yeniden-kullanım mesafesi'ni ölçebilen Reusetracker öne sürülmüştür. Yeniden-kullanım mesafesi, herhangi bir hafiza adresine ard-arda yapılan iki erişim (kullanım ve yeniden-kullanım) arasında erişilen farklı adreslerin sayısıdır, ve dolayısıyla bir veri yerelliği ölçütüdür. Reusetracker kesin olay örneklemesi ve de donanımsal debug yazmaçlarından faydalanarak yeniden-kullanım mesafesini ölçmektedir. Ek olarak, Reusetracker önbellek-tutunum etkilerini göz önünde bulundurarak çok iş parçacıklı uygulamalarda, var olan diğer araçlara göre daha az ek masraf ile yeniden-kullanım mesafesini ölçebilmektedir. Öne sürülen bu araç, sadece 2.9× zaman ve 2.8× hafıza ek masrafına sebep olmaktadır. Kullanıcı tarafından belirlenebilen yeniden-kullanım mesafesine sebep olacak şekilde özel olarak yazılmış bir microbenchmark ile ölçlüdüğü üzere, Reusetracker ortalama 92% doğruluk oranına sahiptir. Paylaşılmış önbelleklerde false-sharing olan mekansal yeniden-kullanım'ların saptanması, ve bazı uygulamaların komşu önbellek-satırı prefetch optimizasyonundan fayda sağlayabileceğine dair tahmin yapılması olarak iki farklı senaryoda Reusetracker'nin, kod düzenlemesinde

nasıl rehber alınabileceği gösterilmiştir.

Bu tez içerisinde öne sürülen araçların ve analizlerin, donanım mimarlarının yeni kesin olay örnekleme özellikleri geliştirirken ve de performans mühendislerinin yazılım performansını ayarlarken faydalı olabileceği gibi; performans analiz ve donanım içerisindeki profilleme araçları alanında ileride olabilecek araştırmalar için yeni yollar açabileceği beklentimizdir.

#### ACKNOWLEDGMENTS

First, I would like to express my gratitude to my advisor Assist. Prof. Didem Unat. Without her advice, support and guidance, this work could not have been completed successfully.

I am also thankful to my thesis progress committee members, Prof. Öznur Özkasap from Koç University and Assist. Prof. Ayşe Yılmazer from Istanbul Technical University for their critical feedbacks that have helped me improve this work. I would also like to thank Assoc. Prof. Aykut Erdem from Koç University and Prof. Özcan Öztürk from Bilkent University for their willingness to be parts of my thesis jury committee.

I would like also to thank Milind Chabbi from Scalable Machine and Paul H. J. Kelly from Imperial College London for the technical discussions that we have had and their advices for the improvement of this work.

I am also grateful to have some of the sharpest and friendliest research colleagues at ParCoreLab that have inspired me with a lot of insightful ideas through various discussions that I have had with them. I am also thankful to them for the fun moments we have shared together.

Special thanks to Mr. Ufuk Yılmaz from Koç University Advanced Computing Center for helping me with running the HPC resources. And finally, I would like to extend my deepest gratitude to my family, especially my mother and wife for their emotional support.

# TABLE OF CONTENTS

| List of | Table   | es ·                                          | xiv |

|---------|---------|-----------------------------------------------|-----|

| List of | Figur   | es                                            | xvi |

| Abbre   | viatior | 18                                            | xx  |

| Chapte  | er 1:   | Introduction                                  | 1   |

| Chapte  | er 2:   | Background                                    | 6   |

| 2.1     | Hardy   | ware Performance Monitoring Unit (PMU)        | 6   |

|         | 2.1.1   | Intel PEBS                                    | 6   |

|         | 2.1.2   | AMD IBS                                       | 8   |

| 2.2     | Hardy   | ware debug registers                          | 10  |

| 2.3     | Linux   | perf_events                                   | 10  |

| Chapte  | er 3:   | Related Work                                  | 11  |

| 3.1     | Analy   | rsis on Precise Event Sampling Features       | 11  |

| 3.2     | Inter-  | Thread Communication                          | 13  |

|         | 3.2.1   | Simulator-based Approaches                    | 13  |

|         | 3.2.2   | OS-based Approaches                           | 13  |

|         | 3.2.3   | Code Instrumentation-based Approaches         | 14  |

|         | 3.2.4   | Profiling Memory Accesses                     | 14  |

| 3.3     | PMU-    | -based Multi-Core Reuse Distance Analysis     | 15  |

|         | 3.3.1   | Modeling Individual Threads and Shared Caches | 15  |

|         | 3.3.2   | Leveraging PMUs and Debug Registers           | 18  |

| Chapter 4: |        | Comparisons of Precise Event Sampling Features in AMD |    |  |

|------------|--------|-------------------------------------------------------|----|--|

|            |        | and Intel Architectures                               | 19 |  |

| 4.1        | Introd | luction                                               | 19 |  |

| 4.2        | Qualit | cative Comparison                                     | 22 |  |

|            | 4.2.1  | Usable Counters                                       | 22 |  |

|            | 4.2.2  | Type of Precise Events                                | 23 |  |

|            | 4.2.3  | Sampled Data                                          | 24 |  |

|            | 4.2.4  | Execution Mode                                        | 25 |  |

| 4.3        | Quant  | itative Comparison                                    | 26 |  |

|            | 4.3.1  | Accuracy                                              | 27 |  |

|            | 4.3.2  | Sensitivity to Sampling Rate and Stability            | 30 |  |

|            | 4.3.3  | Bias and Instruction Attribution                      | 33 |  |

|            | 4.3.4  | Memory Overhead                                       | 35 |  |

|            | 4.3.5  | Multiple Event Monitoring                             | 37 |  |

|            | 4.3.6  | Kernel Mode vs User Mode Identification               | 39 |  |

| 4.4        | Full-F | ledged Profiling Tool                                 | 41 |  |

| Chapte     | er 5:  | ComDetective: Inter-Thread Communication Analysis     | 43 |  |

| 5.1        | Introd | luction                                               | 43 |  |

| 5.2        | Backg  | round                                                 | 46 |  |

| 5.3        | Design | n of ComDetective                                     | 47 |  |

|            | 5.3.1  | Communication Detection Algorithm                     | 48 |  |

|            | 5.3.2  | Quantifying Communication Volume                      | 52 |  |

|            | 5.3.3  | Implementation                                        | 53 |  |

| 5.4        | Exper  | imental Study                                         | 54 |  |

|            | 5.4.1  | Accuracy Verification                                 | 54 |  |

|            | 5.4.2  | Communication in CORAL Benchmarks                     | 65 |  |

|            | 5.4.3  | Communication in PARSEC Benchmarks                    | 68 |  |

|            | 5.4.4  | Use-Case: Data Structure Optimization                 | 69 |  |

|            | 5.4.5   | Sensitivity and Overhead Analysis      | . 70      |

|------------|---------|----------------------------------------|-----------|

| Chapter 6: |         | ReuseTracker: Reuse Distance Analysis  | <b>74</b> |

| 6.1        | Introdu | uction                                 | . 74      |

| 6.2        | Backgr  | round and Terminology                  | . 79      |

|            | 6.2.1   | Single-threaded Reuse Distance         | . 79      |

|            | 6.2.2   | Multi-threaded Reuse Distance          | . 79      |

| 6.3        | Metho   | dology                                 | . 83      |

| 6.4        | Design  | and Implementation                     | . 85      |

|            | 6.4.1   | Intra-thread profiling                 | . 85      |

|            | 6.4.2   | SHARED CACHE PROFILING                 | . 89      |

|            | 6.4.3   | Implementation                         | . 91      |

| 6.5        | Evalua  | tion                                   | . 93      |

|            | 6.5.1   | RIBench Benchmark                      | . 94      |

|            | 6.5.2   | Accuracy without Invalidation          | . 97      |

|            | 6.5.3   | Accuracy with Invalidation             | . 100     |

|            | 6.5.4   | Accuracy under Different Thread Counts | . 105     |

|            | 6.5.5   | Reuse Distances of PARSEC Benchmarks   | . 106     |

|            | 6.5.6   | Use Case: False Sharing Removal        | . 108     |

|            | 6.5.7   | Use Case: Adjacent Cache Line Prefetch | . 109     |

|            | 6.5.8   | Overhead Analysis                      | . 111     |

| Chapte     | r 7:    | Conclusion and Future Work             | 113       |

| Bibliog    | raphy   |                                        | 116       |

| Append     | dix A:  | List of Microbenchmarks                | 136       |

# LIST OF TABLES

| 4.1 | Qualitative comparison of Intel PEBS and AMD IBS. *This informa-                          |     |

|-----|-------------------------------------------------------------------------------------------|-----|

|     | tion is valid for Cascade Lake microarchitecture [55]                                     | 22  |

| 4.2 | Specs of the AMD and the Intel Machines                                                   | 27  |

| 4.3 | Percentage of samples attributed to each instruction in the Bias-Bench                    |     |

|     | benchmark                                                                                 | 35  |

| 5.1 | Running time and data movement comparison of OpenMP and MPI                               |     |

|     | implementations for AMG, MiniFE and Quicksilver using 32 threads                          | 67  |

| 5.2 | Runtime and space overhead of COMDETECTIVE under different sam-                           |     |

|     | pling intervals for applications using 32 threads (LULESH 27 threads)                     | 72  |

| 6.1 | Comparison of ReuseTracker against other techniques that per-                             |     |

|     | form online detection of reuses. Overheads of RDX are measured                            |     |

|     | using a sampling interval of 100<br>K. $^{\dagger} \text{The reported overheads}$ and ac- |     |

|     | curacy are from the original paper. <sup>‡</sup> The reported overheads and               |     |

|     | accuracy are measured in this work. *StatCache's accuracy is high in                      |     |

|     | terms of predicting miss ratio                                                            | 77  |

| 6.2 | Intra-thread reuse. Read (R) or Write (W) may be accessing data at                        |     |

|     | any level in the memory hierarchy.                                                        | 81  |

| 6.3 | Reuse in shared cache                                                                     | 81  |

| 6.4 | Reuse distance and reuse count of RIBench                                                 | 96  |

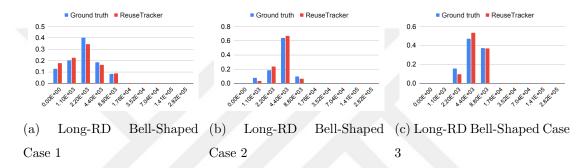

| 6.5 | Parameter values of $RIBench$ when assessing accuracy without cache                       |     |

|     | line invalidation                                                                         | 98  |

| 6.6 | Parameter values of $RIBench$ when assessing accuracy with cache line                     |     |

|     | invalidations on bell-shaped pattern                                                      | 101 |

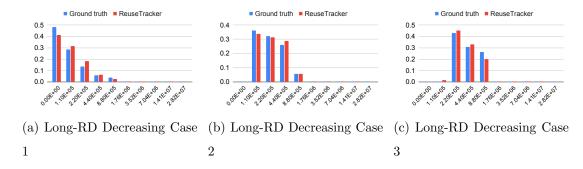

| 6.7 | Parameter values of <i>RIBench</i> when assessing accuracy with cache line |

|-----|----------------------------------------------------------------------------|

|     | invalidations on decreasing pattern                                        |

| 6.8 | Prediction of execution outcomes when ACP is activated 110                 |

# LIST OF FIGURES

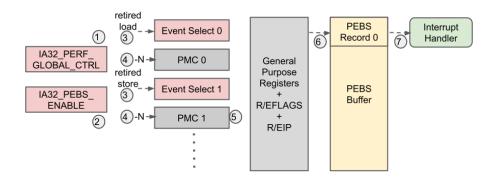

| 2.1 | Execution scenario of Intel PEBS hardware when it monitors retired      |    |

|-----|-------------------------------------------------------------------------|----|

|     | load and store micro-operations                                         | 7  |

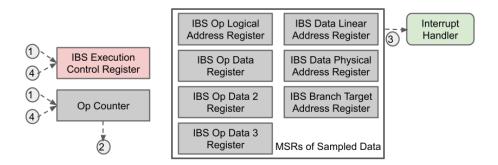

| 2.2 | Execution scenario of AMD IBS hardware when sampling executed           |    |

|     | micro-operations                                                        | 9  |

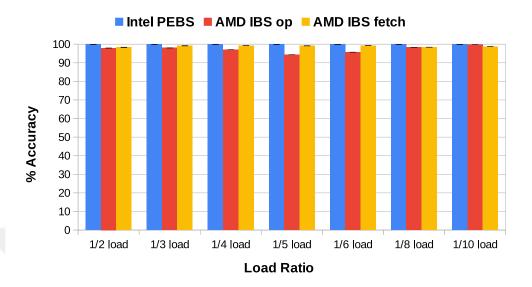

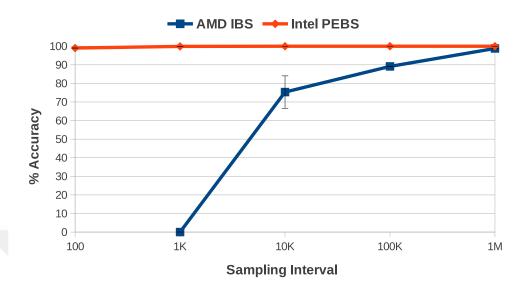

| 4.1 | Comparison of accuracy of PEBS monitoring retired instruction, IBS      |    |

|     | monitoring micro-operation execution (IBS op), and IBS monitoring       |    |

|     | instruction fetch on the <i>Load-Ratio</i> benchmark                    | 30 |

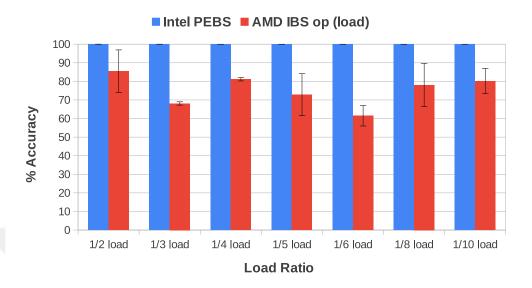

| 4.2 | Accuracy of PEBS and IBS in capturing retired load samples from         |    |

|     | the Load-Ratio benchmark                                                | 31 |

| 4.3 | Accuracy of PEBS and IBS in sampling locked load operations under       |    |

|     | different sampling intervals                                            | 32 |

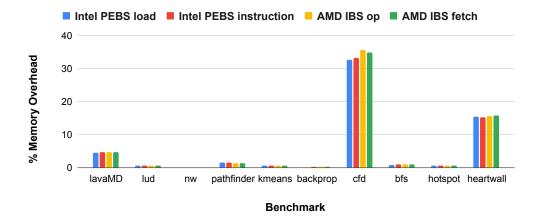

| 4.4 | Comparison of memory overheads on Rodinia benchmarks                    | 36 |

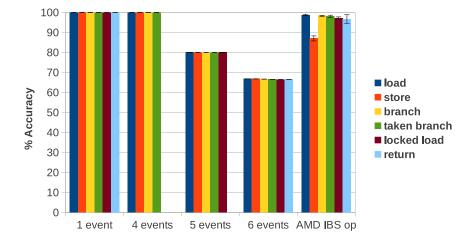

| 4.5 | Comparison of PEBS accuracy in monitoring different numbers of          |    |

|     | events against IBS op. PEBS monitors multiple events simultaneously     |    |

|     | except for 1 event case, where it monitors each event in a separate     |    |

|     | run. IBS can capture all events at once in its microoperation sampling. | 38 |

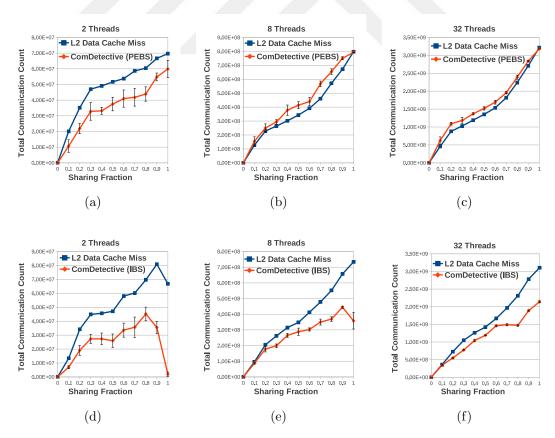

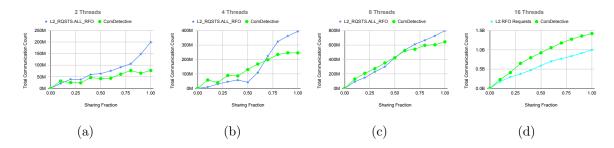

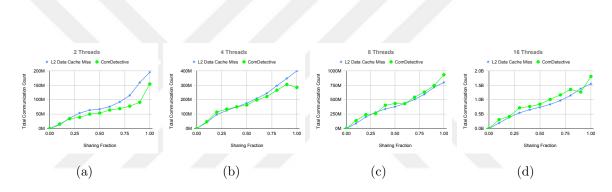

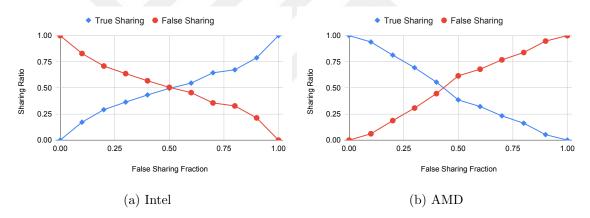

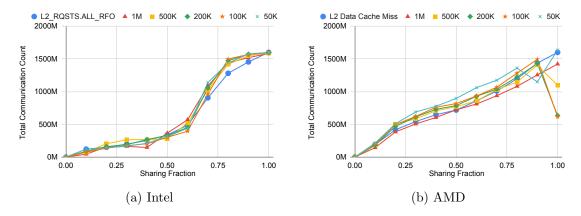

| 4.6 | Total communication counts under different sharing fractions in the     |    |

|     | Intel (Figures 4.6a, 4.6b, 4.6c) and AMD (Figures 4.6d, 4.6e, 4.6f)     |    |

|     | machines                                                                | 41 |

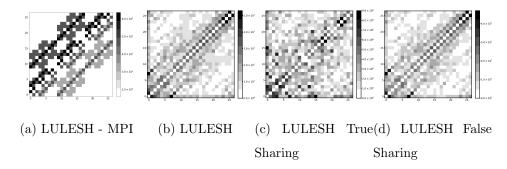

| 5.1 | Communication matrices of LULESH taken from an Intel Broadwell          |    |

|     | machine (Left to Right: MPI, COMDETECTIVE: All, True and False          |    |

|     | Sharing). Darker color indicates more communication                     | 45 |

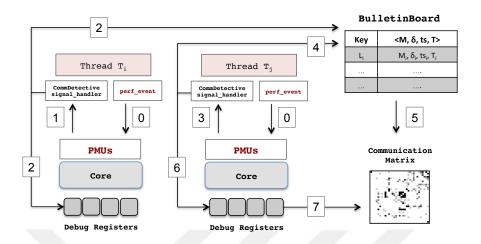

| 5.2  | One possible execution scenario: 0) Every thread configures its PMU      |    |

|------|--------------------------------------------------------------------------|----|

|      | to sample its stores and loads. 1) Thread $T_i$ 's PMU counter overflows |    |

|      | on a store. 2) $T_i$ publishes the sampled address to BulletinBoard if   |    |

|      | no such entry exists and tries to arm its watchpoints with an address    |    |

|      | in the BulletinBoard (if any). 3) Thread $T_j$ ' PMU counter overflows   |    |

|      | on a load. 4) $T_j$ looks up BulletinBoard for a matching cache line. 5) |    |

|      | If found, communication is reported. 6) Otherwise, $T_j$ tries to arm    |    |

|      | watchpoints. 7) $T_j$ accesses an address on which it set a watchpoint,  |    |

|      | the debug register traps, communication is reported                      | 50 |

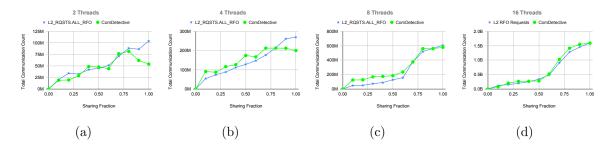

| 5.3  | Total communication counts for across different sharing fractions with   |    |

|      | threads mapped to a single socket (compact) in the Intel machine         | 56 |

| 5.4  | Total communication counts for different sharing fractions with threads  |    |

|      | mapped evenly to two sockets (scatter) the Intel machine                 | 57 |

| 5.5  | Total communication counts for across different sharing fractions with   |    |

|      | threads mapped to a single socket (compact) in the AMD machine           | 57 |

| 5.6  | Total communication counts for different sharing fractions with threads  |    |

|      | mapped evenly to two sockets (scatter) the AMD machine                   | 57 |

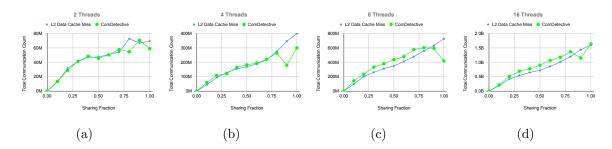

| 5.7  | Comparison between total communication counts captured by Nu-            |    |

|      | malize[33], Comdetective, and the real RFO counts in the Intel           |    |

|      | machine                                                                  | 59 |

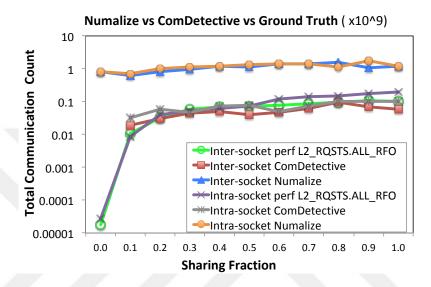

| 5.8  | Comparing true sharing vs. false sharing counts across different shar-   |    |

|      | ing fractions using 8 threads                                            | 60 |

| 5.9  | Total communication counts under different fraction of read opera-       |    |

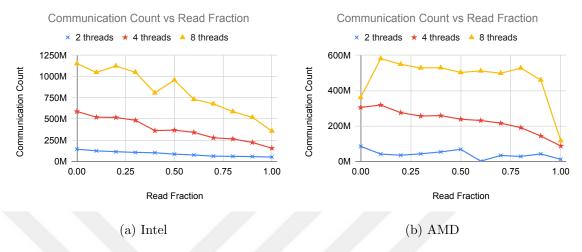

|      | tions detected by ComDetective                                           | 62 |

| 5.10 | Communication matrices for point-to-point communications having          |    |

|      | different sharing fractions in the Intel machine. Thread 0 only com-     |    |

|      | municates with thread 1, thread 2 only communicates with thread 3.       |    |

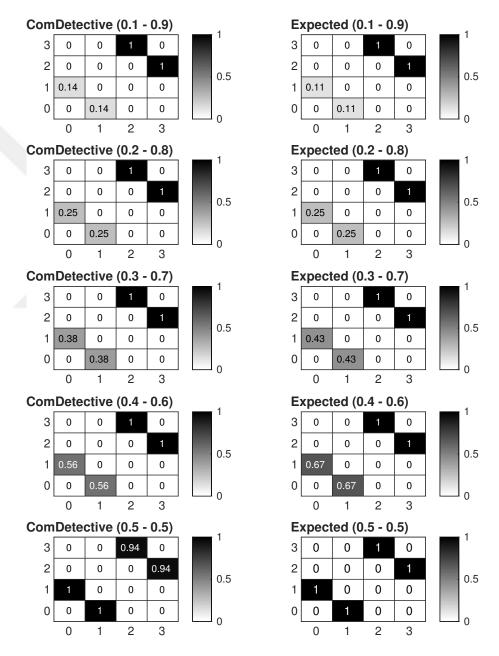

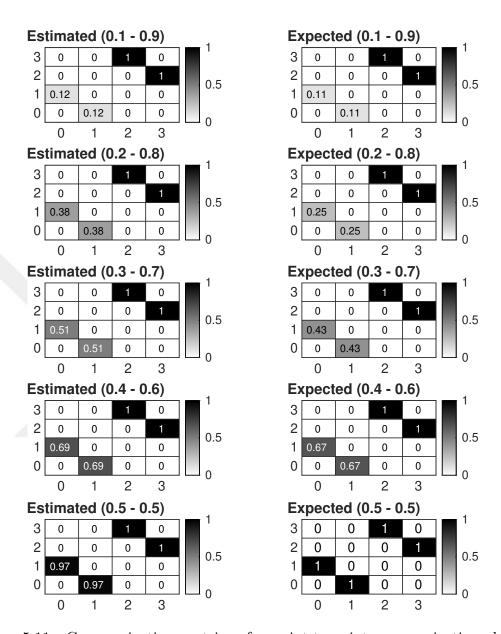

|      | Sharing fractions for each pair are shown on the top of the maps         | 63 |

| 5.11 | Communication matrices for point-to-point communications having               |    |

|------|-------------------------------------------------------------------------------|----|

|      | different sharing fractions in the AMD machine                                | 64 |

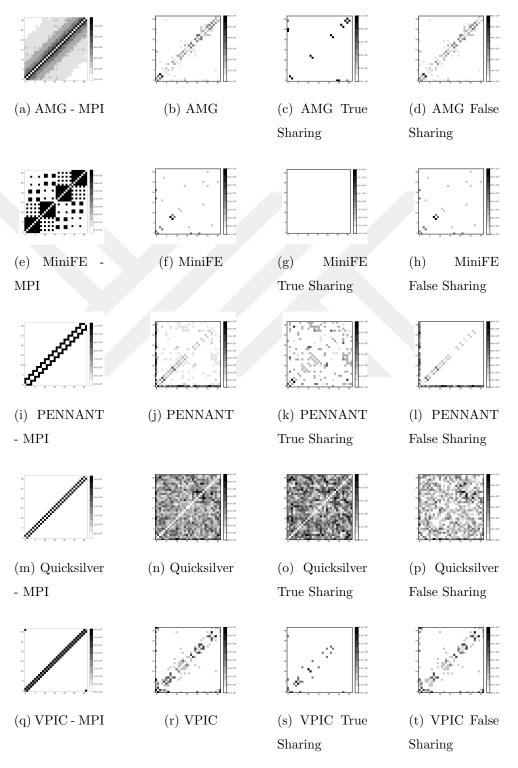

| 5.12 | Communication matrices of CORAL benchmarks. Darker color indi-                |    |

|      | cates more communication                                                      | 66 |

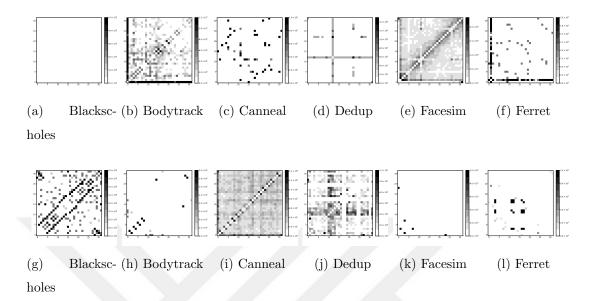

| 5.13 | Communication matrices of PARSEC benchmark suites. Darker color               |    |

|      | indicates more communication                                                  | 69 |

| 5.14 | Total communication counts detected by ComDetective under dif-                |    |

|      | ferent sampling intervals compared with the ground truths when 16             |    |

|      | threads are mapped to 2 sockets                                               | 71 |

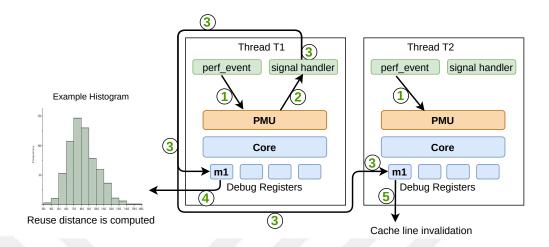

| 6.1  | One possible execution scenario when profiling intra-thread reuse dis-        |    |

|      | tance: (1) Every thread sets its PMUs to sample its stores and loads.         |    |

|      | (2) Thread $T_1$ 's PMU counter overflows on a store to address $m_1$ . (3)   |    |

|      | $T_1$ arms its watchpoint with type RW_TRAP and watchpoints of other          |    |

|      | threads (e.g., the one in $T_2$ ) with type W_TRAP and with address $m_1$     |    |

|      | in debug registers. (4) $T_1$ accesses address $m_1$ again before any other   |    |

|      | thread, the watchpoint traps, time reuse distance is computed. (5)            |    |

|      | Cache line invalidation happens if $T_2$ stores to address $m_1$ before $T_1$ |    |

|      | accesses $m_1$                                                                | 86 |

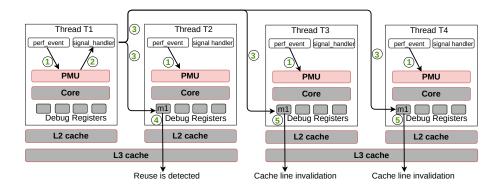

| 6.2  | One possible execution scenario in profiling reuse distance in L3 cache:      |    |

|      | (1) Every thread sets its PMUs to sample its load and store accesses.         |    |

|      | (2) Thread $T_1$ 's PMU counter overflows on a store or a load on address     |    |

|      | $m_1$ . (3) $T_1$ arms the watchpoints on other cores that share the same     |    |

|      | L3 cache with itself with type RW_TRAP and with type W_TRAP on cores          |    |

|      | that do not share the same L3 cache. (4) $T_2$ accesses address $m_1$ again   |    |

|      | before any other thread, the debug register traps, time reuse distance        |    |

|      | in L3 is computed. (5) Cache line invalidation in L3 level occurs if $T_3$    |    |

|      | or $T_4$ stores to address $m_1$ before $T_2$ accesses $m_1$ .                | 90 |

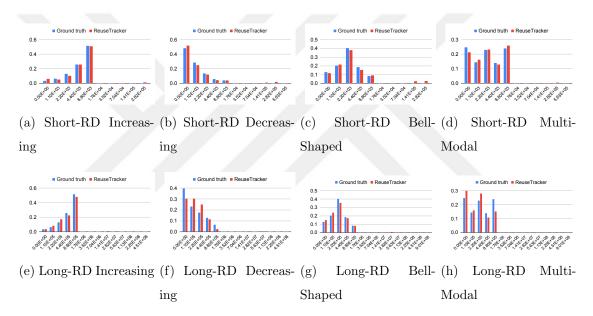

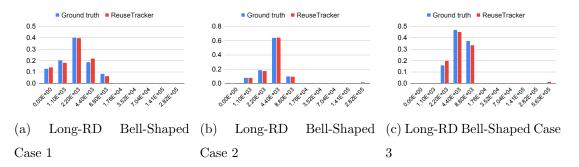

| 6.3  | Reuse distance histograms of <i>RIBench</i> without cache line invalida- |

|------|--------------------------------------------------------------------------|

|      | tion in the Intel machine. X-axis shows the reuse distance ranges        |

|      | in logarithm-scale. Y-axis displays the fraction of reuse-pairs that     |

|      | belong to specific reuse distance ranges                                 |

| 6.4  | Reuse distance histograms of $RIBench$ without cache line invalidation   |

|      | in the AMD machine                                                       |

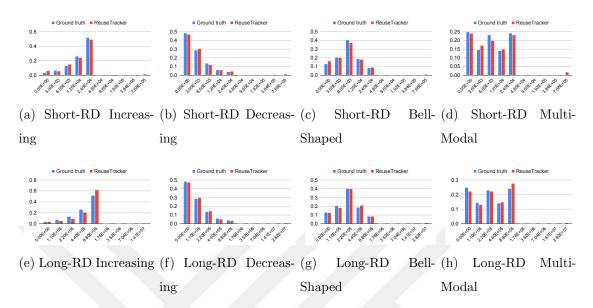

| 6.5  | Reuse distance histograms of $RIBench$ with cache line invalidations     |

|      | on bell-shaped pattern in the Intel machine                              |

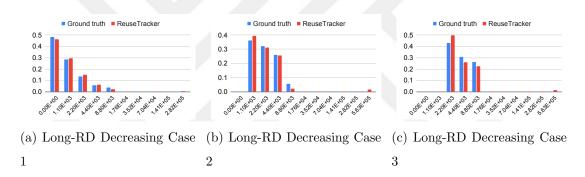

| 6.6  | Reuse distance histograms of $RIBench$ with cache line invalidations     |

|      | on decreasing pattern in the Intel machine                               |

| 6.7  | Reuse distance histograms of $RIBench$ with cache line invalidations     |

|      | on $bell$ -shaped pattern in the AMD machine                             |

| 6.8  | Reuse distance histograms of $RIBench$ with cache line invalidations     |

|      | on decreasing pattern in the AMD machine                                 |

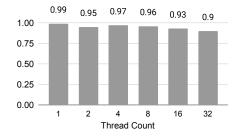

| 6.9  | Accuracy of ReuseTracker running the $RIBench$ under different           |

|      | thread counts in the Intel machine. X-axis displays the thread counts,   |

|      | and Y-axis shows the accuracy for each thread count. $$ 105              |

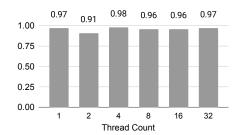

| 6.10 | Accuracy of ReuseTracker running the $RIBench$ under different           |

|      | thread counts in the AMD machine                                         |

| 6.11 | Histograms of intra-thread reuse distance of blackscholes and body-      |

|      | track from PARSEC. X-axis shows the reuse distance ranges in logarithm-  |

|      | scale. Y-axis displays in logarithm-scale the fraction of reuse-pairs    |

|      | that belong to specific reuse distance ranges                            |

| 6.12 | Histograms of reuse distance in L3 cache of streamcluster and fre-       |

|      | qmine from PARSEC. X-axis shows the reuse distance ranges in             |

|      | logarithm-scale. Y-axis displays in linear scale the fraction of reuse-  |

|      | pairs that belong to specific reuse distance ranges                      |

#### **ABBREVIATIONS**

CPU Central Processing Unit

PMU Performance Monitoring Unit

PEBS Processor Event Based Sampling

IBS Instruction Based Sampling

MRK Marked Event Sampling

SPE Statistical Profiling Extension

OS Operating System

PMC Performance monitoring counter

MSR Model Specific Register

TLB Translation Look-aside Buffer

PEBS Processor Event Based Sampling

RAW Read after Write

RAR Read after Read

MRC Miss Ratio Curve

AET Average Eviction Time

RISC Reduced Instruction Set Computer

ITLB Instruction Translation Look-aside Buffer

MPI Message Passing Interface

WP Watchpoint

RFO Read for Ownership

LRU Least Recently Used

DRAM Dynamic Random-Access Memory

ACP Adjacent Cache Line Prefetch

#### Chapter 1

#### INTRODUCTION

Profiling tools are essential resources for performance tuning of any computer applications. Using profiling tools, programmers are able to identify bottlenecks, such as cache misses, long-latency memory accesses, or branch mispredictions, that cause performance slowdowns in the profiled programs. In the post-Moore era where multithreaded applications become ubiquitous, there is a higher variety of bottlenecks that prevent these applications from reaching their theoretical peak performance. Some examples of bottlenecks that may afflict multithreaded code are false sharing, inter-thread cache line transfers, and coherence misses.

A number of profiling tools have been developed to detect performance bottlenecks in multithreaded applications and associate these bottlenecks with the threads

or locations in source code that cause them. Among these tools, there are techniques that leverage hardware simulators [14, 29, 104]. There are also techniques

that insert profiling code to original program code, i.e. code instrumentation, using

compiler techniques [82, 83] or binary instrumentation [34, 33, 103, 125]. These existing tools, though have been demonstrated to be able to locate some bottlenecks

in the code that they profile, still suffer from several drawbacks. One drawback

is that the tools that rely on cycle-accurate simulators and most tools that leverage code instrumentation suffer from huge time and memory overheads. Another

drawback is that the simulator and code instrumentation-based tools might suffer

from inaccuracy. Hardware simulators might not accurately capture the behavior

of multithreaded programs when running on actual hardware due to the simplistic

or idealized nature of the simulated machines. Some examples of how simulators

might alter program behavior are when they simulate CPU cores with in-order ex-

ecution instead of out-of-order execution, or when the simulated CPU cores access shared data from memory in different order compared to CPU cores in real machines, which will result in different amount of inter-thread communication or false sharing detected by the simulators. Not only simulators, binary instrumentation-based techniques might also fail to capture the behavior of multithreaded code on actual hardware as these techniques can distort the parallel schedule of concurrent threads [92] unless a supplementary tool that can record and replay original program execution deterministically such as Intel's PinPlay is also utilized [90].

To avoid the overhead and inaccuracy problems incurred by simulator and code instrumentation-based techniques, one solution is to leverage performance monitoring units (PMUs), which are hardware features that exist in current commodity CPUs. PMUs can be programmed to count and sample hardware events, such as retired instructions, branch instructions, and memory accesses, and software events, such as page faults and context switches. As PMUs are hardware features, they incur much lower overheads than simulators or code instrumentation-based tools, and cause minimal perturbations to program execution when used for profiling. However, ordinary PMUs still have a flaw in the way that they cannot accurately attribute sampled events to the actual instructions that trigger those events. When one such PMU samples an event, the instruction address recorded is the value of instruction pointer at the time the sampling interrupt is handled, and not the address of the actual instruction that causes the event. To fix this flaw, PMUs are enhanced further with precise event sampling technology [53, 38, 108, 124], which allows sampled events to be accurately associated with the instructions that trigger them and the effective addresses that they access, in case the sampled events are memory accesses.

Precise event sampling is supported in a number of architectures. Intel provides this feature through Processor Event Based Sampling (PEBS) that is supported in Nehalem microarchitecture and its successors [53]. AMD supports this feature through Instruction Based Sampling (IBS) that is available in AMD Opteron (microarchitecture family 10h) and its successors [38]. IBM PowerPC architecture also provides this capability through Marked Event Sampling (MRK) [108] feature that

is available in IBM POWER5 and its successors. The most recent example of precise event sampling technology is ARM's Statistical Profiling Extension (SPE) which is available in Armv8.2 [124] and its successors.

A number of profiling techniques have leveraged precise event sampling for various purposes. Some of these techniques detect long-latency memory accesses and identify their locations in source code [71, 70]. There are also other techniques that capture remote memory accesses [72, 74], cache misses [93], false sharing [74, 23, 50], and profile data locality in single-threaded applications [119]. However, to the best of our knowledge, none of these hardware-based techniques is able to capture data movement and measure data locality in the context of multithreaded execution, which are common sources of bottlenecks in shared memory parallel programs that run on multicore machines. To address this need, we design a profiling algorithm that captures inter-thread communications in the form of communication matrices by also differentiating them into true and false sharing communications, and we also devise two other profiling algorithms that measure reuse distance, which is a widely used metric for data locality, in private and shared caches, respectively, in the context of multithreaded execution.

Though precise event sampling features have been used in a number of profiling tools, there have been very few works that perform in-depth analysis on these features. These works only focus on Intel PEBS, and only analyze its accuracy and time overhead without addressing other aspects such as memory overhead, stability of sample counts, and differences in functionality among precise event sampling features across different architectures. To address this research gap, in addition to proposing profiling techniques, we also perform in-depth qualitative and quantitative analyses of two most widely used precise event sampling facilities, i.e. Intel PEBS and AMD IBS, by analyzing their accuracy, memory overhead, stability, and functionality.

In this dissertation, we perform qualitative and quantitative analyses on Intel PEBS and AMD IBS, and present profiling tools that leverage Intel PEBS to capture inter-thread communications and measure reuse distance. To our knowledge, the analysis on PEBS and IBS that we perform in this work is the most comprehensive study on precise event sampling to date. Furthermore, the algorithms utilized by our profiling tools are microarchitecture agnostic as they will work on any multicore with precise event sampling support and debug registers. To summarize, the major contributions of this dissertation are as follows.

- The most comprehensive qualitative and quantitative study to date on the precise event sampling facilities of two major vendors, i.e. Intel and AMD, using the microbenchmarks

- Imaginative uses of precise event sampling in the forms of two low-overhead, open-source tools and their underlying algorithms that profile data locality and communication using precise event sampling and debug registers

- COMDETECTIVE, a communication detection tool and its algorithm that captures inter-thread communications and distinguishes them into false and true sharing communications

- ReuseTracker, a reuse distance analysis tool and its two algorithms that measure reuse distance of multithreaded applications in private and shared caches, respectively

- An extensive set of microbenchmarks that evaluates accuracy, memory overhead, sampling biases, stability, and functionality of precise event sampling facilities, and another set of microbenchmarks that evaluates the accuracy of the developed precise event sampling-based tools, which can also be used to evaluate other tools that capture inter-thread communications and measure reuse distance

- Extensive experiments on an Intel Cascade Lake and an AMD Zen 2 machines using the microbenchmarks as well as large benchmarks from Parsec, Rodinia, CORAL, CORAL 2, and Synchrobench suites to measure the accuracy and

overheads of the developed tools, and to gain insights into data locality and communication in the benchmarks

• Important use-case scenarios that demonstrate how the profiling tools can be used to guide optimizations on profiled applications

Comdetective and ReuseTracker have been published in [101] and [102] respectively. The repository of Comdetective is publicly available at https://github.com/comdetective-tools, and the repository of ReuseTracker is publicly available at https://github.com/ParCoreLab/ReuseTracker. The microbenchmarks developed and used in this work are listed in Appendix A.

#### Chapter 2

#### BACKGROUND

#### 2.1 Hardware Performance Monitoring Unit (PMU)

CPU's PMU offers a programmable way to count hardware events such as loads, stores, CPU cycles, etc. PMUs can be configured to trigger an overflow interrupt once a threshold number of events elapse. A profiler, running in the address space of the monitored program, handles the interrupt and records and attributes the measurements to their corresponding communication types or objects. We refer to a PMU interrupt as a "sample." PMUs are per CPU core and virtualized by the operating system for each OS thread.

A subset of PMUs that is called *precise event sampling* can sample hardware events and accurately locate the instructions that trigger the events. Intel supports this capability through Processor Event Based Sampling (PEBS) [25] that is available in Intel Nehalem and its successors, while AMD processors allow precise event sampling through their Instruction-Based Sampling (IBS) [17] feature that is supported in AMD Opteron (microarchitecture family 10h) and its successors.

#### 2.1.1 Intel PEBS

On Intel architecture, precise event sampling can utilize any programmable counters available in PMUs [55]. The PMUs in an Intel core consist of a number of components: global control registers, status registers, event select registers, and performance monitoring counters (PMCs). Global control registers are used to globally enable or disable event counters or precise event sampling ability of each counter. Status registers contain info about the capabilities supported by the PMUs or the overflow status of each event counter. Event select registers are used to choose the

hardware or software event to be monitored. A PMC counts the occurrences of a monitored event.

To enable precise event sampling, a programmable counter is enabled along with its PEBS capability by global control registers [55]. This counter is then configured to monitor a targeted hardware event by programming its event select register with the mask and number of the targeted event. The counter is also configured to have a counter overflow in every elapsing of a specified number of events, which is the sampling interval. When a counter overflows, PEBS hardware is armed to trap the next occurrence of the monitored event. When the next monitored event occurs, a mechanism called *PEBS assist* will copy the machine state to a memory buffer called PEBS buffer. The machine state and other data such as effective address and load latency collected by a PEBS assist are grouped into a data structure called a PEBS record in the PEBS buffer. When the number of PEBS records in the PEBS buffer has reached a predefined threshold, a hardware interrupt is triggered and handled by an interrupt handler that is a part of the OS. The interrupt handler reads all of the PEBS records in the PEBS buffer, clears the buffer, and sends an OS signal to a user process or thread that will collect the sampled data. On receiving the signal, the user process/thread retrieves the sampled data and uses it for profiling.

Figure 2.1: Execution scenario of Intel PEBS hardware when it monitors retired load and store micro-operations.

Figure 2.1 shows an example execution of PEBS when profiling retired load and store micro-operations. (1) The global control register IA32\_PERF\_GLOBAL\_CTRL

enables PMC 0 and PMC 1 by setting its bits that correspond to the counters to 1. (2) Another global control register, i.e. IA32\_PEBS\_ENABLE MSR, enables PMC 0 and PMC 1 to capture architectural state using PEBS by setting the corresponding bits to 1. (3) The event select registers IA32\_PERFEVTSEL0 and IA32\_PERFEVTSEL1 are programmed to make PMC 0 and PMC 1 count retired load micro-operations and retired store micro-operations, respectively. (4) The configured PMCs are also preloaded with -N with N being the sampling interval, so that they overflow on elapsing N monitored events. (5) After the profiled program executes for a while, PMC 1's counter overflows after N stores occur. The PEBS hardware is armed to trap the next store access that happens in the same core. PMC 1 is preloaded with -N again. (6) Another store access occurs after the counter overflow. The armed PEBS hardware traps the access and a microcode records the architectural state in a PEBS record located in PEBS buffer in kernel space. (7) If the number of PEBS records has reached a specified threshold, which is 1 in this case, a hardware interrupt is triggered, and an interrupt handler is called to transfer the PEBS records to user space.

#### 2.1.2 AMD IBS

Different from Intel, the precise event sampling in AMD, i.e. IBS, employs a hardware-based facility that is separate from the PMUs that are commonly used to count or imprecisely sample specific hardware or software events. This mechanism is based on the instruction sampling technique proposed in [31]. The IBS facility in each CPU core consists of a couple of components: two control registers, two internal counters, and a number of MSRs (Model Specific Registers) for sampled data [8].

This facility allows only two flavors of sampling: instruction fetch sampling and micro-operation sampling [38, 8]. Either one of the two control registers is programmed to control the IBS hardware depending on the sampling flavor that is chosen. If instruction fetch sampling is selected, the fetch control register is programmed. Otherwise, the execution control register is programmed. After the con-

trol register is programmed, the internal counter that belongs to the selected sampling flavor, i.e. either the fetch counter or the op counter, will count the monitored event in the CPU core. When an event sampling occurs, information related to the event is recorded in the MSRs of sampled data that belong to the chosen sampling flavor.

The counter for micro-operation sampling, i.e. op counter, can be programmed to count either clock cycles or dispatched micro-operations. If it is programmed to count clock cycles, it increments for each clock cycle, and when the counter reaches the specified sampling interval, a micro-operation is selected for sampling from the next dispatch line. On the other hand, if the counter is programmed to count dispatched micro-operations, it increments for every dispatched micro-operation, and when the counter reaches the sampling interval, a micro-operation is selected to be sampled in the next cycle. In this work, we only consider the op counter to be programmed for counting dispatched micro-operations, which is the default configuration of the IBS driver in [47]. We also choose this configuration as it generates predictable number of samples given a known number of micro-operations in a profiled application, which suits our accuracy verification method.

Figure 2.2: Execution scenario of AMD IBS hardware when sampling executed micro-operations.

Figure 2.2 shows an execution scenario of IBS when counting and sampling microoperations. 1 IBS execution control register in a CPU core is programmed to make the IBS hardware count and sample executed micro-operations. The sampling interval is also written as a field in the control register. The op counter is set to a pseudorandom 7-bit value in the range of 1 to 127. ② After the profiled thread executes for a while, the value in the op counter equals the specified sampling interval. When the value of the counter equals the sampling interval, the next executed micro-operation will be tagged for sampling. ③ The tagged micro-operation retires. The execution info of the tagged micro-operation, which includes instruction pointer and effective address, is recorded in a number of MSRs. After the tagged operation retires, a hardware interrupt is triggered, and the interrupt handler copies the recorded data in the MSRs to a memory buffer in kernel space. ④ After copying sampled data, the interrupt handler configures the control register again to re-enable IBS, and the op counter is preloaded with another pseudorandom 7-bit value.

#### 2.2 Hardware debug registers

Hardware debug registers [59, 85] trap CPU execution when a program counter reaches an instruction address (breakpoint) or when an instruction accesses a monitored address (watchpoint). When a thread sets up a debug register to trap a future memory access to certain address, we consider this thread to be *arming a watchpoint* on that address. One can configure debug registers with different addresses, widths, and types of memory accesses to be trapped (i.e. W\_TRAP for stores and RW\_TRAP for both loads and stores). Current processors from x86 architectures typically have four debug registers.

#### 2.3 Linux perf\_events

Linux provides an interface to configure PMUs and debug registers using the perf\_event \_open [67] system call and ioctl calls. The ability to configure debug registers has been available since Linux 2.6.33, and the ability to program multiple PMUs since Linux 2.6.39 [67]. The Linux kernel can deliver a signal to the specific thread that encounters a PMU interrupt or a debug register trap. The user code can (1) create a circular buffer into which the kernel appends the sampled data on each sample using mmap function and (2) collect the signal context on each watchpoint trap.

#### Chapter 3

#### RELATED WORK

#### 3.1 Analysis on Precise Event Sampling Features

While there have been a few works that analyze the accuracy and overheads of PEBS, there is no in-depth study on the accuracy, overheads, stability, or functionality of IBS. To the best of our knowledge, none of the previous work on PEBS analyzes the stability and explore the functionality, such as execution mode detection, of PEBS either.

Larysch [64] evaluated the accuracy and overhead of PEBS in measuring memory bandwidth. The author performed their experiments using low sampling intervals, which are between 10 and 1000. Through the experiments, the author discovered that PEBS suffers from higher sample losses as sampling interval is decreased.

Nonell et al., [89] evaluated the accuracy and time overhead of PEBS on applications running on a large numbers of CPU cores, which range from 2048 to 128k cores. By using the PEBS driver that they developed in a lightweight kernel, they could reach low overhead in capturing memory access patterns with high accuracy. Their driver could also maintain high accuracy of PEBS in capturing memory access patterns even under low sampling interval, which is up to 64.

Yi et al., [128] analyzed the accuracy of PEBS, and discovered that PEBS is prone to bias in event sampling due to shadowing. To eliminate the bias, they propose insertion of nop instructions after each monitored event. Gottschall et al., [43] proposed *Oracle profiler* as a golden reference for time-proportional attribution of event sampling. They found out that existing precise event sampling facilities such as Intel PEBS, AMD IBS, and ARM SPE are not time proportional in sampling instructions i.e. the number of samples taken from an instruction is not proportional

to the number of CPU cycles incurred by that instruction. They also discovered that PEBS suffers from instruction attribution problem when multiple instructions commit at the same cycle under ILP after a sample is taken.

Weaver and McKee [120] evaluated the variation or, as we refer to it, stability of event counting by PMUs in nine implementations of x86 architecture. They discovered that inter-machine variations could happen because certain instructions could be counted double in certain microarchitectures or a counter for a specific event in one CPU version could be more accurate than in older versions. They also found out that intra-machine variations of PMU-generated instruction count might also occur, which could be caused by virtual memory layout of profiled programs or OS activities such as page faults and timer interrupts. Weaver et al. [121] also evaluated PMUs in eleven different implementations of x86\_64 architecture and discovered sources of variation in their counted events. They explored possible ways to work around these limitations in the machines to produce more deterministic counts.

Akiyama and Hirofuchi [6] quantitatively analyzed the time overhead of PEBS, and demonstrated how the quantified overhead can be used to predict the actual overhead of complex applications. They also evaluated the effect of sampling rate and PEBS buffer size on cache pollution and the performance of profiled applications. Xu et al., [126] identify the inaccuracies of sampling in PEBS and develop a mathematical model in software to rectify inaccuracies.

This work differs from the previous work first by benchmarking several behavioral aspects of precise event sampling through some carefully crafted microbenchmarks. Second, we evaluate the accuracy and memory overhead under more complex situations such as while monitoring multiple events in PEBS and monitoring in different modes. Third, we quantify on the stability of sample counts generated by precise event sampling.

#### 3.2 Inter-Thread Communication

#### 3.2.1 Simulator-based Approaches

Barrow-Williams et al. [14] generate communication patterns for SPLASH-2 and PARSEC benchmarks by collecting memory access traces using Virtutech simics simulator [79]. Thread table of the kernel running on the simulator is also accessed to keep track of all running threads. Similar to [14], Henrique Molina da Cruz et al. [29] also employ a simulator to generate memory access traces. The resulting memory traces are used as the basis to create memory sharing matrix. By considering the memory sharing matrix, thread affinity is implemented by taking memory hierarchy into account. Application threads are mapped according to the generated thread affinity by using Minas framework [88]. Comdetective differs from these techniques in the way that they generate thread communication pattern with the help of a hardware simulator, while we generate communication matrix by PMUs. This makes Comdetective practical to use and runs faster than the simulator-based techniques, especially for full application execution.

#### 3.2.2 OS-based Approaches

Tam et al. [109] and Azimi et al. [12] obtain communication patterns from running parallel applications through PMUs. Unlike COMDETECTIVE, their technique requires kernel support. PMUs are accessed by the kernel and the communication pattern of a running application can be generated by the kernel. The PMUs that are accessed are pipeline stall cycle breakdown, L2/L3 remote cache access counters, and L1 cache miss data address sampler.

Cruz et al. [28] use Translation Look-aside Buffers (TLBs) to generate of communication matrix that records page level memory sharing. Two approaches were introduced that use software-managed TLB and hardware-managed TLB. For the software-managed TLB, a trap is sent to OS when TLB miss occurs. Before the missing page table entry is loaded, TLB content of each core is checked for the matches of the missing entry. The information on the matches is used to update

the communication matrix. For the hardware-managed TLB, kernel will check the content of TLBs periodically. Both approaches require OS support. In contrast, ComDetective uses user-space PMU sampling. Moreover, TLB-granularity monitoring is too coarse-grained because inter-thread communications happen at cacheline granularity.

#### 3.2.3 Code Instrumentation-based Approaches

Diener et al. [33, 34] develop Numalize, which uses binary instrumentation [75] to intercept memory accesses and identify potential communications among threads by comparing the intercepted memory accesses. Two or three threads that perform accesses to a memory block consecutively are considered to communicate by the tool. We have compared Competentive with Numalize in our experimental study. Numalize introduces more than 16× runtime overhead and almost 2000× memory overhead, whereas Competentive introduces only 1.30× runtime overhead and 1.27× space overhead. Moreover, Competentive does not dilate execution and produces more accurate communication matrices.

A more recent work [83, 82] performs code instrumentation with the help of the LLVM compiler. This instrumentation allows detection of RAW and RAR dependencies in the original code and outputs this information as communication and reuse matrices. Through communication reuse distance and communication reuse ratio derived from these outputs, the tool facilitates analysis of communication bottlenecks that arise from thread interactions in different code regions. However, this tool still suffers from significant slowdown  $(140\times)$ , and is limited to detection of memory accesses to similar addresses. Hence, to our knowledge, it cannot detect cache line transfers that are triggered by false sharing.

#### 3.2.4 Profiling Memory Accesses

Concerning the use of Performance Monitoring Units (PMUs) by library or standalone tool to profile memory accesses or data movement, our work is not the first one that implements this idea. Lachaize et al. [61] introduced MemProf, which utilizes

kernel function calls to sample data from memory access events. This data is used to identify objects that are accessed remotely by any thread. Like COMDETECTIVE, MemProf also intercepts functions for thread creation, thread destruction, object creation, and object destruction to differentiate memory accesses belonging to different objects and different threads. Unat et al. [113] introduce a tool, ExaSAT, to analyze the movement of data objects using compiler analysis. Even though it has no runtime overhead, it cannot capture all the program objects or their references as it relies on static analysis. Chabbi et al. [23] employ PMUs and debug registers to detect false sharing but do not generalize it for inter-thread communication matrices; furthermore, their technique does not quantify communication volume even for false sharing. Even though these tools can count memory access events, they do not associate these events to threads and are not used in generating communication pattern among threads.

#### 3.3 PMU-based Multi-Core Reuse Distance Analysis

Existing works related to PMU-based multi-core reuse distance analysis can be organized into two groups. The first group consists of the papers that proposed multi-core reuse distance analysis techniques that profile individual threads and shared caches. The second group introduced reuse distance analysis techniques that leverage PMUs and debug registers.

#### 3.3.1 Modeling Individual Threads and Shared Caches

Ding and Chilimbi proposed an analytical model that predicts shared cache behavior indirectly by combining per-thread reuse distance, interleaving, and data sharing information [35]. This technique processes execution trace of a multithreaded code to generate a set of per-thread metrics. This set of metrics covers locality (i.e. reuse distance profile), data sharing, and interleaving information of each thread. By accounting for multiple sets of metrics from a subset of threads using the model, miss ratio of this subset of threads while running in a shared cache can be predicted. Another work by Jiang et al. [58] proposed a probabilistic model that can approx-

imate concurrent reuse distance from reuse distances of individual threads. The multithreaded applications targeted by this model are those that perform similar computations in all threads and have uniform amount of shared data across their thread groups. These techniques in [35] and [58] require processing of execution traces that might incur large storage overhead in the host machines. Furthermore, the computation of reuse distance profiles from the traces can also require huge performance overhead depending on the size of the traces.

Schuff et al. introduced a different approach in [104]. Their technique performs on-the-fly reuse distance computations by using a modified hardware simulator. This technique computes reuse distances in both private and shared caches by also ensuring the coherence in the private caches. Furthermore, it also models the interleaving of memory accesses by all threads in the shared cache. This technique was improved in [103] by having all threads run in parallel while being profiled. Moreover, sampling technique was also introduced to reduce overhead by computing reuse distances only on randomly selected memory references. A shortcoming in these approaches is that they require simulator or binary instrumentation to intercept every single memory access. The use of simulator introduces huge performance and memory consumption overhead. Furthermore, the use of binary instrumentation might distort the parallel schedules of task-parallel and dataflow applications as reported in [92].

Chandra et al. [32] introduced one of the first models that predict L2 cache misses when multiple threads run on a shared L2 cache. Eklov et al. [42] also proposed another model that estimates miss ratio and CPI of co-scheduled applications that run on a shared cache. These models work by firstly approximating the reuse distance profile of the applications' interleaved accesses in the shared cache. After that, the models calculate the shared cache miss ratio based on the approximated profile. One key difference of these works from ours is that they target co-scheduled applications that do not share data among them.

Pericas et al. [92] introduced a low-overhead method to generate execution traces of multithreaded code and compute reuse distances of shared caches from these traces. In generating shared cache reuse distance histograms, it also captures cache coherence-based invalidations across caches. To minimize overhead, this method reduces trace sizes by operating at the granularity of compute kernels. By operating at coarse-grained level, this method can accurately capture distant reuses while losing information on near reuses.

Maeda et al. [78] introduced a technique to profile reuse distances in every level of a multi-level cache hierarchy. Since this technique still requires memory address trace as an input, it still needs other tools to generate the trace. As a result, this technique is still exposed to the drawbacks of these tools, such as huge overhead in simulators or distortion of parallel schedule due to binary instrumentation.

Another work that leverages memory traces to profile reuse distances in private and shared caches was proposed by Barai et al. [13]. In this work, they utilized a compiler-assisted technique to generate a basic block-labeled memory trace from a single sequential execution of a profiled application. This trace is then used by a probabilistic analytical method to predict the reuse distance profiles of the application in private and shared caches when the application runs in parallel.

Hu et al. [51] proposed a model that reduces time and space costs in constructing cache miss ratio curves (MRCs) by analyzing only reuse-time distribution. They used average eviction time (AET) as a parameter to detect reuses that lead to cache misses. Their model could be extended to predict cache misses in a shared cache when multiple threads run on it. However, in estimating cache misses in private and shared caches, their model does not assume data sharing among threads that might lead to coherence misses in private caches and shared caches.

Ji et al. [56] developed a probability model that computes L2 reuse distance profile and predicts cache misses in L2 without requiring extra simulations or trace generations. Though able to give cache miss prediction, this model still needs inputs in the form of L1 reuse distance histograms. These inputs might have to be generated by simulator or binary instrumentation-based tools.

There are also recent works in [100], [118], [65], and [66] that proposed analytical models to profile shared cache behaviors by processing L1 cache reuse distance profiles. Similar to previously discussed works, these works also depend on other

tools to generate per-thread reuse distance histograms that they need.

# 3.3.2 Leveraging PMUs and Debug Registers

To the best of our knowledge, there have been only two techniques in literature that utilize hardware counters and watchpoint mechanism to compute reuse distances. The first technique was presented by Berg and Hagersten in [16]. In that paper, they proposed StatCache, a profiling tool that calculates time reuse distances by using hardware counters and watchpoints and deploys a statistical model to predict cache miss ratio based on the collected time reuse distance profile. This tool could predict the miss ratio of a fully associative cache with random replacement policy. The second technique that leverages hardware counters and watchpoints was introduced by Wang et al. [119]. This technique, which is named RDX, utilizes PMUs and debug registers in Intel machines to compute time reuse distances, and then, convert them to stack reuse distances. Both techniques in [16] and [119] differ from our work in the way that they do not account for inter-thread interactions in multithreaded code and they do not model shared caches.

# Chapter 4

# COMPARISONS OF PRECISE EVENT SAMPLING FEATURES IN AMD AND INTEL ARCHITECTURES

#### 4.1 Introduction

Precise event sampling is a powerful profiling feature supported by Performance Monitoring Units (PMUs) in modern CPUs. This technology has been incorporated in a number of profiling tools that identify performance bottlenecks in parallel applications [52, 54, 80, 77, 101, 70, 101, 102, 73, 97, 74, 69, 122, 23, 98]. For instance, some of such tools are used to detect long latency memory accesses, false sharing and inter-core cache line transfers. In addition to identifying the bottlenecks, precise event sampling also offers the possibility to pinpoint the source code lines and data objects causing the bottlenecks through its ability to sample instruction pointers and effective addresses of the operations. Compared to alternative technologies such as cycle-accurate hardware simulators [79, 19] and binary instrumentation [21, 75], techniques that leverage precise event sampling incur much lower time and memory overheads as they employ existing hardware features to capture real hardware events without introducing additional software layer.

A number of architectures support hardware-based precise event sampling. Intel supports this capability through Processor Event Based Sampling (PEBS) [53] that is available in Intel Nehalem and its successors and many researchers develop several tools for PEBS [52, 54, 40, 69, 23, 101]. Similarly, AMD processors allow event sampling through their Instruction-Based Sampling (IBS) [38] feature that is supported in AMD Opteron (microarchitecture family 10h) and its successors. A number of tools have been developed using this sampling facility for AMD [10, 39, 7, 84, 62, 70, 74]. The support for event sampling in IBM PowerPC

architecture is provided through Marked Event Sampling (MRK) [108] feature that is available in IBM POWER5 and its successors. This capability is also recently supported in ARM architecture through Statistical Profiling Extension (SPE) feature that was introduced in Armv8.2 [124].

Despite the fact that event sampling feature is commonly used for developing profiling tools, there exists no rigorous study that benchmarks this capability in the microarchitecture. In this dissertation, we analyze and compare the precise event sampling facilities of two major vendors namely, Intel and AMD, in depth through extensive benchmarks. To support precise event sampling, Intel PEBS and AMD IBS adopt drastically different designs resulting in different characteristics at hardware level that affect the accuracy, stability, overheads and functionality of the sampling facility. While the outcomes of this work can be used by the profiling tool developers to better understand the behaviours of their tools, hardware designers can leverage the findings to design better PMUs not only for x86-based systems but also for ARM [124, 11] and emerging RISC-V processors [95, 37].

We firstly present qualitative differences between the two precise event sampling schemes in terms of usable counters, type of precise events, sampled data, and execution mode. Based on the observations on the qualitative characteristics, we developed a number of microbenchmarks that can assess the effects of the observed qualitative characteristics. Through these benchmarks, we then quantitatively compare the two schemes in terms of accuracy and memory overhead in sampling individual and multiple events. We also evaluate the stability and sampling bias of both schemes, and analyze the ability in attributing samples to the instructions that trigger the samples and the execution modes of those instructions, i.e. kernel mode or user mode. Lastly, to demonstrate how the microarchitectural characteristics that we identified in our qualitative and quantitative analyses impact profiling tools, we study a full-fledged open-source tool, namely ComDetective [101, 1], that employs precise event sampling to detect inter-thread communication.

Our findings based on the quantitative and qualitative study are as follows. (1) PEBS offers a large set of specific hardware events such as branches, memory loads,

etc to select from, while IBS has only two flavors of sampling: instruction fetch sampling and micro-operation execution sampling. One impact of this difference is that PEBS is more accurate than IBS in capturing proportional number of samples from specific events, such as loads or branches. (2) Though IBS supports fewer sampling choices than PEBS, it offers richer information in each sample, which shows, for example, the origin of accessed data in memory hierarchy and the status of TLB accesses. As a consequence, PEBS would have to monitor multiple events simultaneously in order to generate the similar level of information as in one IBS run. (3) PEBS shares the same counters with other non-PEBS PMU events, while IBS has its own internal counters. As a result, the number of different events that PEBS can monitor without multiplexing is limited to the number of available PMU counters per logical core. Multiplexing in PEBS suffers from sample loss, leading to reduced accuracy. (4) PEBS is more stable than IBS in capturing sample counts, and both PEBS and IBS exhibit similar memory overheads. (5) IBS is very sensitive to the sampling interval and its accuracy significantly drops at high sampling frequency. PEBS has high accuracy regardless of sampling rate. (6) Both PEBS and IBS are equally biased in sampling an event from multiple different instructions. (7) PEBS can be programmed to count events that execute only in user mode, only in kernel mode, or in any of the two modes, while an IBS counter always increments on any fetch or micro-operation without discriminating its execution mode.

In summary, the contributions in this chapter are.

- Presenting the most comprehensive study to date on precise event sampling supported by two major vendors

- Detailed qualitative and quantitative comparisons of microarchitectural characteristics between Intel PEBS and AMD IBS and demonstrating their accuracy, stability, bias, functionality and memory overhead

- A suite of synthetic benchmarks that can be used for extending this study to other vendors and architectures

Providing invaluable information both to the hardware designers and tool developers through our findings that would help understand and improve their designs

# 4.2 Qualitative Comparison

This section presents qualitative differences between the two precise event sampling schemes, Intel PEBS and AMD IBS, and Table 4.1 summarizes these differences.

| Aspect          | *Intel PEBS                                                                                                                                                                                    | AMD IBS                                                                                                                     |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Usable Counters | 4 general-purpose                                                                                                                                                                              | 2 internal counters                                                                                                         |  |

| per thread      | performance counters                                                                                                                                                                           | (1 for each sampling flavor)                                                                                                |  |

| Event Type      | 62 subevents of 12 events                                                                                                                                                                      | 2 sampling flavors                                                                                                          |  |

| Sampled Data    | general purpose registers,  RFLAGS register, RIP register, applicable counter, data linear address, data src encoding/store status, latency value, timestamp counter eventingIP, TX abort info | 16 attributes in each sampled data for inst. fetch sampling 44 attributes in each sampled data for micro-operation sampling |  |

| Execution Mode  | User or kernel or both modes                                                                                                                                                                   | Both user and kernel modes                                                                                                  |  |

Table 4.1: Qualitative comparison of Intel PEBS and AMD IBS. \*This information is valid for Cascade Lake microarchitecture [55].

#### 4.2.1 Usable Counters

**Observation 1** PEBS can use up to 4 counters and monitor up to 4 events without multiplexing in microarchitectures. Starting Ice Lake, PEBS can monitor up to 7, while IBS has two dedicated counters, one for each sampling flavor.

**Observation 2** If the op counter of IBS is programmed to count dispatched micro-operations, it is always preloaded with a pseudorandom 7-bit value after its sampling interrupt is handled.

PEBS shares the PMCs that are also used by other non-precise PMU events. All microarchitectures before Ice Lake (launched in 2019) allow PEBS to utilize any of the four general-purpose performance counters in each logical core. In Ice Lake, PEBS can also use the three fixed-function performance counters in addition to the general-purpose ones. When the number of events that it monitors is higher than the number of counters, software overcomes this limitation by context switching more events on limited counters. When this oversubscription happens, the approximated counter values are inaccurate, and might cause the events to lose some counter overflows.

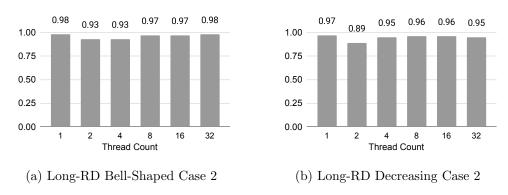

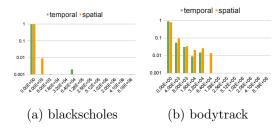

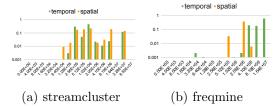

Different from PEBS that shares counters with other PMU events, IBS counts instruction fetches and executed micro-operations using its own internal counters that are separate from other PMCs in each AMD CPU core. It has two internal counters, one for each sampling flavor. Since these counters are not multiplexed, IBS does not miss an overflow.