# Low-Density Parity-Check Code Decoder Design and Error Characterization on an FPGA Based Framework

by Burak Unal

Copyright © Burak Unal 2019

A Dissertation Submitted to the Faculty of the Department of Electrical and Computer Engineering

In Partial Fulfillment of the Requirements For the Degree of

DOCTOR OF PHILOSOPHY

In the Graduate College

THE UNIVERSITY OF ARIZONA

# THE UNIVERSITY OF ARIZONA GRADUATE COLLEGE

As members of the Dissertation Committee, we certify that we have read the dissertation prepared by Burak Unal,

entitled Low-Density Parity-Check Code Decoder Design and Error Characterization on an FPGA Based Framework

and recommend that it be accepted as fulfilling the dissertation requirement for the Degree of Doctor of Philosophy.

Ali Akoglu

Date: April 8, 2019

Bane Vasic

Date: April 8, 2019

Ali Bilgin

Date: April 8, 2019

Tosiron Adegbija

Final approval and acceptance of this dissertation is contingent upon the candidate's submission of the final copies of the dissertation to the Graduate College.

I hereby certify that I have read this dissertation prepared under my direction and recommend that it be accepted as fulfilling the dissertation requirement.

Dissertation Director: Ali Akeglu

Date: April 8, 2019

#### ACKNOWLEDGMENTS

I would like to thank all the people who contributed to my PhD journey with their support. Those who inspired me; those who encouraged me; those who were with me on difficult times.

First and foremost, I would like to express my deepest acknowledgments to the most valuable persons in my life, my beloved family, and most importantly my parents, Nurettin Ünal and Güldane Ünal. I would not be reaching for and achieving my dreams without their encouragement and endless love. I am sincerely grateful to my grandfather, Bayram Ünal and my wonderful sisters, Cansu, Özge, and İpek Naz Ünal.

I would like to thank you Dr. Ali Akoglu for serving as my advisor during past several years. This dissertation is the outcome of several years of research and collaborations. I would like to thank the following people who have made this work possible either through a direct collaboration or through their guidance: Dr. Ali Bilgin and Dr. Bane Vasić. In addition, I would like to thank Dr. Fakhreddine Ghaffari for his collaboration.

I would like to thank all my friends and colleagues in the Reconfigurable Computing Laboratory for sharing their enjoyable moments.

I am very grateful to my undergrad advisor, Prof. Kenan Danisman for his friendship, support, and understanding throughout both my professional career and personal life.

## DEDICATION

To Nurettin Ünal:  $My \ father$  And the most beautiful hearted man.

# TABLE OF CONTENTS

| List of Figures                                                                                                                                                                                                                                                                               | 7                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| List of Tables                                                                                                                                                                                                                                                                                | 9                                            |

| Abstract                                                                                                                                                                                                                                                                                      | 10                                           |

| CHAPTER 1. INTRODUCTION  1.1. Overview  1.2. Problem Statement and Aims  1.3. Summary of Contributions  1.3.1. Algorithmic Contribution  1.3.2. Architecture Specific Contribution  1.3.3. FPGA Based Framework                                                                               | 12<br>12<br>13<br>14<br>14<br>15<br>16       |

| Chapter 2. Preliminaries                                                                                                                                                                                                                                                                      | 20<br>20<br>21<br>22                         |

| Chapter 3. Probabilistic Gab Algorithm Methodology                                                                                                                                                                                                                                            | 26<br>27<br>28<br>31<br>32                   |

| CHAPTER 4. HARDWARE DESIGN OF LDPC DECODERS  4.1. Hardware Design  4.1.1. GaB and PGaB Hardware Design  4.1.2. GDBF and PGDBF Hardware Design  4.2. Simulation Environment  4.3. Performance Analysis  4.4. Robustness Analysis  4.4.1. Effect of Code Rate  4.4.2. Effect of Codeword Length | 36<br>36<br>39<br>43<br>45<br>48<br>49<br>51 |

| Chapter 5. Routability Problem of the LDPC Code                                                                                                                                                                                                                                               | <b>5</b> 4 54 55 57                          |

## Table of Contents—Continued

| 5.3.1. Codeword Length and Code Rate vs. Resource Usage           | 58         |

|-------------------------------------------------------------------|------------|

| 5.3.2. Codeword Length and Code Rate vs. Critical Path Delay      | 61         |

| 5.3.3. Partitioning Amount vs. LUT Usage-Delay Product Analysis . | 63         |

| CHAPTER 6. FPGA BASED FRAMEWORK                                   | 67         |

| 6.1. Related Work                                                 | 67         |

| 6.2. Framework and Hardware Implementation                        | 70         |

| 6.3. Quantifying the Benefits of the FPGA Based Framework         | 73         |

| 6.3.1. Case Study: Time to Generate FER Analysis                  | 74         |

| 6.3.2. Case Study: Error Pattern Analysis                         | 74         |

| Chapter 7. Conclusions and Perspectives                           | <b>7</b> 9 |

| 7.1. Summary and Contributions                                    | 79         |

| References                                                        | 81         |

# LIST OF FIGURES

| FIGURE 2.1. Tanner graph (left) and its parity check matrix (right) FIGURE 2.2. General architecture of VNUs for (a) GaB, (b) PGaB, (c) GDBF,                                                                                                                          | 20                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| and (d) PGDBF for $dv = 4$ and $N = 1296$ . (e) Maximum finder unit for                                                                                                                                                                                                |                                 |

| GDBF and PGDBF decoders                                                                                                                                                                                                                                                | <ul><li>24</li><li>25</li></ul> |

| FIGURE 3.1. Frame Error Rate versus $p_v$ ( $\alpha = 0.02, 0.025, 0.03, \text{ and } 0.035$ ). LDPC code ( $d_v = 4, d_c = 8, Z = 54$ ), ( $N = 1296, M = 648$ ) when switching iteration a in get to 15                                                              | 32                              |

| switching iteration $s_i$ is set to 15                                                                                                                                                                                                                                 |                                 |

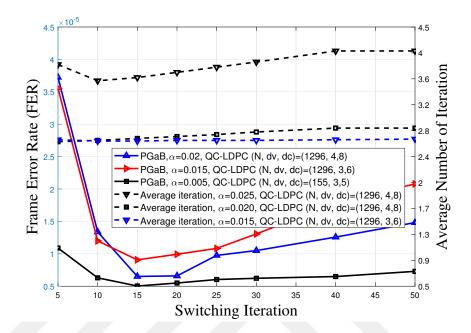

| configurations of (155, 3, 5, 0.5), (1296, 3, 6, 0.5) and (1296, 4, 8, 0.5)). FIGURE 3.3. Comparison of average number of iterations for PGaB, GaB, PGaB Hybrid (GaB for the first 15 iterations, and PGaB onwards) ( $d_v = 4$ , $d_c = 8$ , $N = 1296$ , $M = 648$ ) | 33<br>34                        |

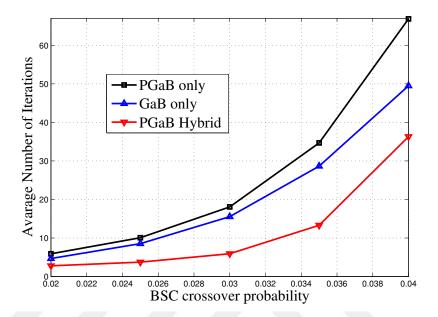

| Figure 4.1. Overall decoder architecture (a) for PGaB, VNU architecture for dv4 (c) and LFSR-32bits based Random Number Generator (b)                                                                                                                                  | 37                              |

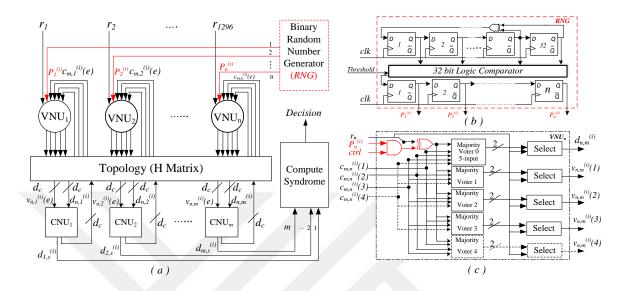

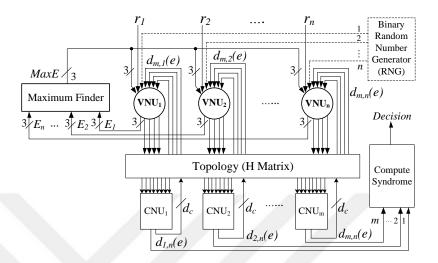

| FIGURE 4.2. Architecture of GDBF and PGDBF for $d_v = 4$ , and $N = 1296$ , where dc is determined by the code rate                                                                                                                                                    | 39                              |

| FIGURE 4.3. Architecture of VNU for GDBF and PGDBF for $d_v = 4$ , and N = 1296                                                                                                                                                                                        | 39                              |

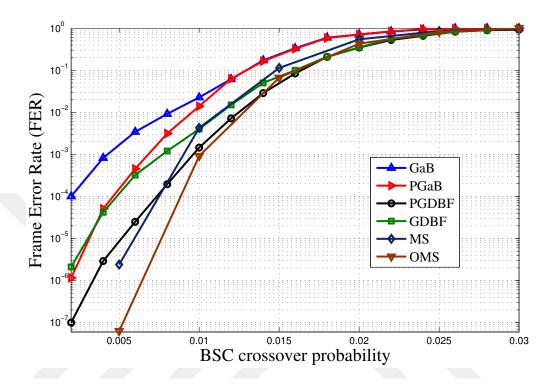

| FIGURE 4.4. GaB, PGaB, GDBF, PGDBF, MS, OMS FER comparison: FER vs. probability of error introduced to each bit of the 1296-bit codeword with $d_v = 4$ , $d_c = 8$ , $M = 648$ , and Code Rate = 0.5                                                                  | 44                              |

| FIGURE 4.5. GaB, PGaB, GDBF, PGDBF, MS, OMS FER comparison: FER vs. probability of error introduced to each bit of the 1296-bit codeword                                                                                                                               | 44                              |

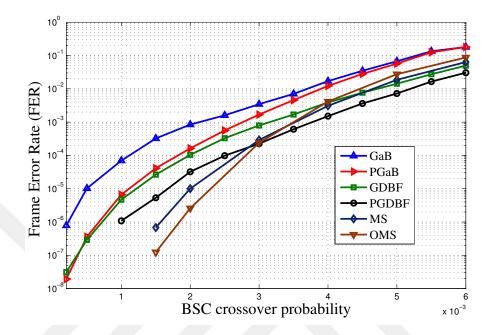

| with $d_v = 4$ , $d_c = 16$ , $M = 324$ , and Code Rate = 0.75 FIGURE 4.6. GaB, PGaB, GDBF, PGDBF, MS, and OMS: FER vs. crossover probability for the QC-LDPC code with $(d_v = 4, d_c = 28, N = 2212, M = 2000)$                                                      | 45                              |

| 312, and Code Rate = 0.857)                                                                                                                                                                                                                                            | 47                              |

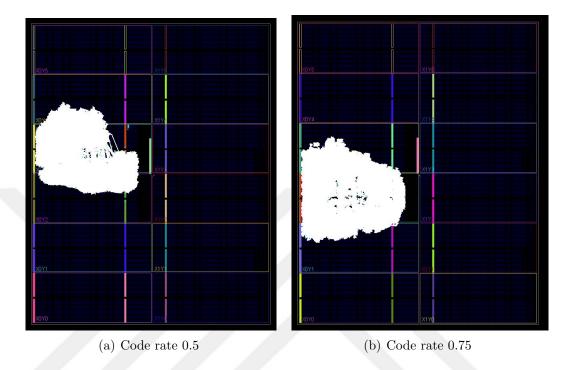

| a) PGaB decoder on the QC-LDPC code with $(d_v = 4, d_c = 8, N = 1296, M = 648, \text{ and Rate} = 0.5)$ . b) PGaB decoder on the QC-LDPC code                                                                                                                         |                                 |

| with $(d_v = 4, d_c = 16, N = 1296, M = 324, \text{ and Rate} = 0.75)$                                                                                                                                                                                                 | 50                              |

## LIST OF FIGURES—Continued

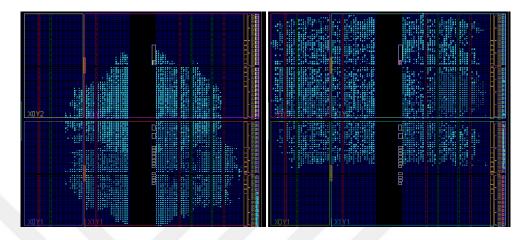

| Figure 5.1. Post-routing layout of GaB decoder for the QC-LDPC code ( $d_v =$                                                                             |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| $4, d_c = 28, n = 1106$ , and code rate = 0.857) on the Xilinx Zynq XC7Z020                                                                               |     |

| FPGA for Regular (left) and Depopulation based implementation (right).                                                                                    | 56  |

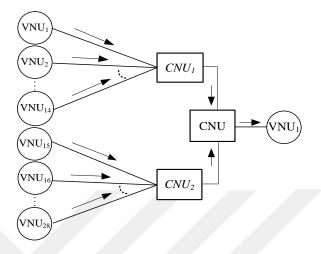

| FIGURE 5.2. Two-way partitioning methodology for CNU with $d_c = 28$                                                                                      | 57  |

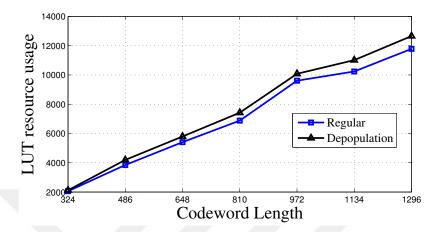

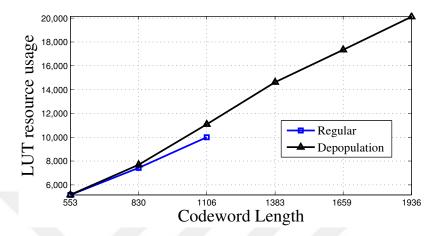

| FIGURE 5.3. Resource usage vs Codeword length comparison for the QC-                                                                                      |     |

| LDPC code with $(d_v = 4, d_c = 8, \text{ code rate} = 0.5)$ based on Xilinx Zynq                                                                         |     |

| XC7Z020 FPGA                                                                                                                                              | 59  |

| FIGURE 5.4. Resource usage vs. Codeword Length comparison for the QC-                                                                                     |     |

| LDPC code with $(d_v = 4, d_c = 28, \text{ code rate} = 0.857)$ based on Xilinx Zynq                                                                      |     |

| XC7Z020 FPGA                                                                                                                                              | 60  |

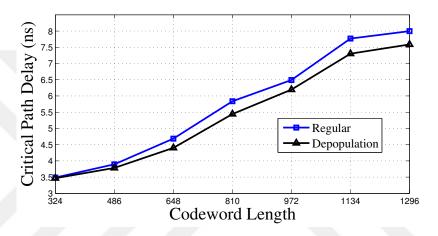

| FIGURE 5.5. Critical path delay (ns) vs Codeword length for the QC-LDPC                                                                                   |     |

| code with $(d_v = 4, d_c = 8, \text{ code rate} = 0.5)$ based on Xilinx Zynq XC7Z020                                                                      |     |

| FPGA                                                                                                                                                      | 61  |

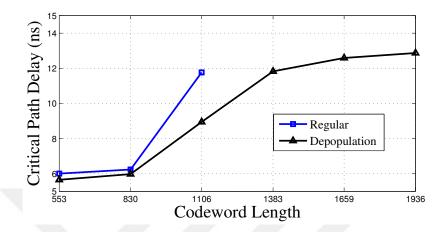

| FIGURE 5.6. Critical path delay (ns) vs Codeword length for the QC-LDPC                                                                                   |     |

| code with $(d_v = 4, d_c = 28, \text{ code rate} = 0.857)$ based on Xilinx Zynq                                                                           |     |

| XC7Z020 FPGA                                                                                                                                              | 62  |

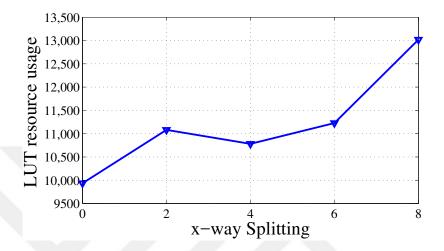

| FIGURE 5.7. Resource usage trend with respect to the x-way partitioning for the QC-LDPC code with codeword length of 1106 ( $d_v = 4$ , $d_c = 28$ , code |     |

| rate=0.857) based on Xilinx Zyng XC7Z020 FPGA                                                                                                             | 64  |

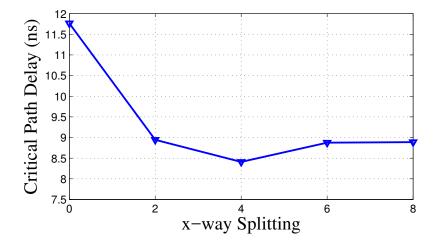

| FIGURE 5.8. Critical path delay trend with respect to the x-way partitioning                                                                              |     |

| for the QC-LDPC code with codeword length of 1106 ( $d_v = 4$ , $d_c = 28$ ,                                                                              |     |

| code rate=0.857) based on Xilinx Zynq XC7Z020 FPGA                                                                                                        | 64  |

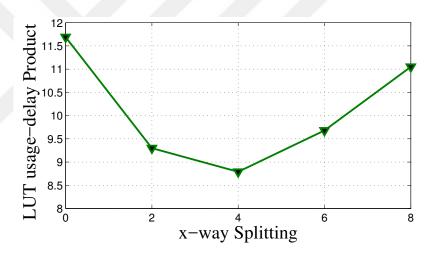

| FIGURE 5.9. LUT usage-delay product trend with respect to the x-way par-                                                                                  |     |

| titioning for the QC-LDPC code with codeword length of 1106 ( $d_v = 4$ ,                                                                                 |     |

| $d_c = 28$ , code rate=0.857) based on Xilinx Zynq XC7Z020 FPGA                                                                                           | 66  |

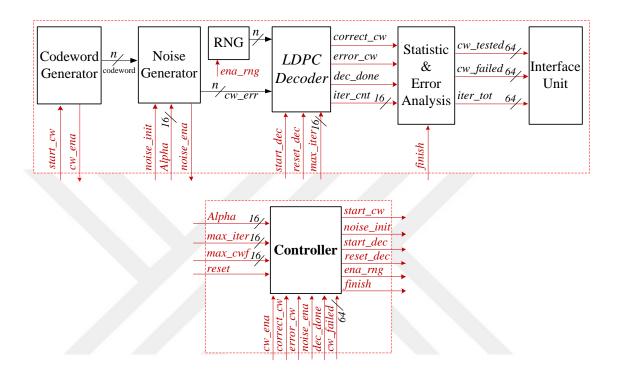

| FIGURE 6.1. Overall architecture of FPGA based testbed. Red colored wires                                                                                 |     |

| indicate control signals, others indicate internal connections                                                                                            | 72  |

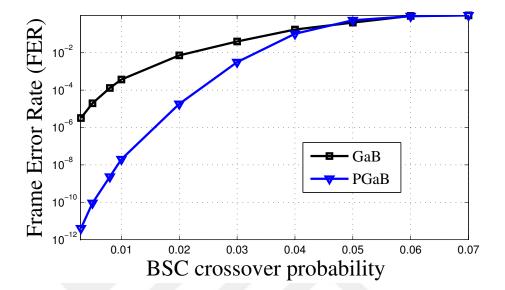

| FIGURE 6.2. GaB and PGaB FER comparison: FER vs. probability of error                                                                                     | ' - |

| introduced to each bit of the 1296-bit codeword with $(d_v = 4, d_c = 8, \text{ code})$                                                                   |     |

| rate = $0.5$ )                                                                                                                                            | 75  |

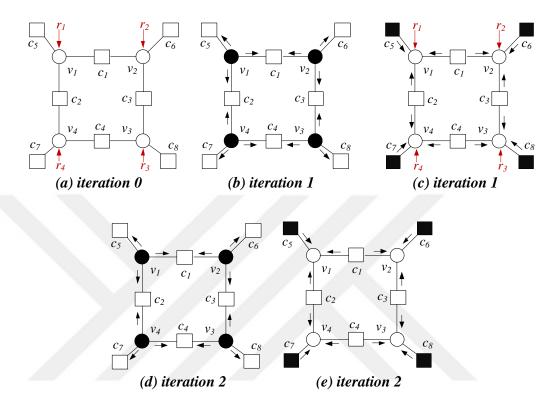

| FIGURE 6.3. 4-error pattern for GaB algorithm. Black/white denotes erro-                                                                                  |     |

| neous/correct VNU. and unsatisfied/satisfied CNU                                                                                                          | 76  |

## LIST OF TABLES

| Table 3.1. Truth Table for PGaB Algorithm                                                                                                                                                                                                                                         | 29 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 4.1. Hardware Resource Utilization, Throughput and Clock Rate of Decoding Algorithms Implemented for Tanner Code on Virtex6 FPGA . Table 4.2. Resource usage of GaB, PGaB, GDBF, and PGDBF based on the FPGA implementations for QC-LDPC $(N, d_v, R)$ =(1296, 4, 0.5), QC- | 40 |

| LDPC $(N, d_v, R)$ =(1296, 4, 0.75), and QC-LDPC $(N, d_v, R)$ =(2212, 4, 0.857). (% indicates the difference with respect to GaB)                                                                                                                                                | 46 |

| PGDBF based on the FPGA implementations for QC-LDPC $(N, d_v, R)$ =(1294, 0.5), QC-LDPC $(N, d_v, R)$ =(1296, 4, 0.75), and QC-LDPC $(N, d_v, R)$ =(22                                                                                                                            |    |

| 4, 0.857). (% indicates the difference with respect to GaB) TABLE 4.4. Throughput-to-area ratio (TAR) and Normalized Throughput $(T_p)$ for GaB, PGaB, GDBF, and PGDBF when the crossover probability is                                                                          | 46 |

| fixed. Based on the FPGA implementations for QC-LDPC with $(N, d_v, R)$ =(4, 0.5), QC-LDPC $(N, d_v, R)$ =(1296, 4, 0.75), and QC-LDPC $(N, d_v, R)$ =(224, 0.857)                                                                                                                |    |

| Table 5.1. The number of LUTs used as routing resource for different codeword length on the LDPC code with $(d_v = 4, d_c = 28, \text{ code rate} = 0.857)$                                                                                                                       |    |

| based on Xilinx Zynq XC7Z020 FPGA                                                                                                                                                                                                                                                 | 60 |

| TABLE 5.2. Total number of paths vs. codeword length $(n)$ on the LDPC code with $(d_v = 4, d_c = 28, \text{ rate} = 0.857)$                                                                                                                                                      | 61 |

| Table 6.1. FPGA based LDPC testbeds                                                                                                                                                                                                                                               | 69 |

| and Virtex-7 XC7VX485T FPGAs                                                                                                                                                                                                                                                      | 73 |

| TABLE 6.3. Execution time for GaB and PGaB on the FPGA based testbed (Xilinx Zynq XC7Z020 FPGA) for the crossover probabilities of 0.005 and 0.01 where ( $d_v = 4$ , $d_c = 8$ , $n = 1296$ , code rate=0.5) (* indicates                                                        |    |

| estimated time)                                                                                                                                                                                                                                                                   | 75 |

#### Abstract

Low-Density Parity-Check (LDPC) codes have gained popularity in communication systems and standards due to their capacity approaching error correction performance. Among all the hard-decision based LDPC decoders, Gallager B (GaB), due to simplicity of its operations, poses as the most hardware friendly algorithm and an attractive solution for meeting the high-throughput demand in communication systems. However, GaB suffers from poor error correction performance. In this work, we first propose a resource efficient GaB hardware architecture that delivers the best throughput while using fewest Field Programmable Gate Array (FPGA) resources with respect to the state of the art comparable LDPC decoding algorithms. We then introduce a Probabilistic GaB (PGaB) algorithm that disturbs the decisions made during the decoding iterations randomly with a probability value determined based on experimental studies. We achieve up to four orders of magnitude better error correction performance than the GaB with a 3.4% improvement in normalized throughput performance. PGaB requires around 40% less energy than GaB as the probabilistic execution results with reducing the average iteration count by up to 62% compared to the GaB. We also show that our PGaB consistently results with an improvement in maximum operational clock rate compared to the state of the art implementations.

In this dissertation, we also present a high throughput FPGA based framework to accelerate error characterization of the LDPC codes. Our flexible framework allows the end user adjust the simulation parameters and rapidly study various LDPC codes and decoders. We first show that the connection intensive bipartite graph based LDPC decoder hardware architecture creates routing stress for longer codewords that are utilized in today's communications systems and standards. We address this problem by partitioning each processing element (PE) in the bipartite graph in such a

way that the inputs of a PE are evenly distributed over its partitions. This allows depopulating the Loo Up Table (LUT) resources utilized for the decoder architecture by spreading the logic across the FPGA. We show that even though LUT usage increases, critical path delay reduces with the depopulation. More importantly, with the depopulation technique an unroutable design becomes routable, which allows longer codewords to be mapped on the FPGA. We then conduct two experiments on error correction performance analysis for the GaB and PGaB algorithms, demonstrate our framework's ability to reach a resolution level that is not attainable with general purpose processor (GPP) based simulations, which reduces the time scale of simulations to 24 hours from an estimated 199 years. We finally conduct the first study on identifying all possible codewords that are not correctable by the GaB for the case where a codeword has four errors. We reduce the time scale of this simulation that requires processing 117 billion codewords to 4 hours and 38 minutes with our framework from an estimated 7800 days on a single GPP.

#### Chapter 1

#### Introduction

#### 1.1 Overview

Error correction codes have been utilized in several communication systems to ensure reliable transmission of information. Claude Shannon established theoretical limit at which information can be transmitted reliably over a noisy channel in 1948 [1]. Transmitting information reliably with a rate close to this theoretical limit is known as the channel capacity. Research efforts in decoding Low-Density Parity-Check (LDPC) codes have led to design and implementation of a myriad iterative decoding algorithms approaching channel capacity [2], [3], [4], [5]. LDPC codes offer performance improvement and implementation cost saving for long codeword lengths compared to Reed-Solomon (RS) [6] and Bose-Chaudhuri-Hocquenghem (BCH) [7], [8] codes as they are theoretically proven to be asymptotically good family of codes [9]. Therefore, for a sufficiently high codeword length, LDPC will outperform a BCH or RS code of a comparable rate. Binary LDPC codes have been widely adopted in several standards and applications [10], such as mobile communications [11], 10 Gigabit Ethernet (10GBase-T) [12], [13], digital video broadcasting (DVB-S2) [14], wireless local area network (WiFi IEEE 802.11n) [15], WiMAX (IEEE 802.16e) wireless communications [16], deep-space communications [17], as well as data storage systems [18]. LDPC codes have also been selected as the data channel coding scheme for the 3GPP new radio access technology of the fifth generation (5G) mobile communication standard [19], [20]. In addition, LDPC codes handle soft channel outputs which is essential in numerous applications even in optical communications and data storage channels, especially in flash memories [21], [22].

LDPC decoding algorithms mainly differ based on the nature of iterative opera-

tions applied over the received messages. Complexity level of these operations determine the trade-off between hardware performance and decoding performance. Here we note that, throughout this dissertation, with the hardware performance, we refer to the operational clock rate and throughput as well as the resource requirements of the decoder algorithm, and with the decoder performance, we refer to the error correction capability of the decoder algorithm measured based on the frame error rate metric. In the literature, we have seen soft-decision and hard-decision decoders as two main classes of LDPC decoding algorithms. Soft-decision decoders such as Belief Propagation (BP) [23],[24], Sum Product (SP) [25], Min-Sum (MS) [26], and Offset Min-Sum [27] offer high error correction performance with the cost of high computation complexity. On the other hand, hard-decision decoders such as Gallager B (GaB) [28],[29], Bit-Flipping (BF) [30], Gradient Descent Bit-Flipping (GDBF) [31], and Probabilistic Gradient Descent Bit-Flipping (PGDBF) [32] have much less hardware requirements than soft-decision decoders, and achieve higher throughput with a trade-off in the error correction performance.

#### 1.2 Problem Statement and Aims

Research efforts to this date for improving the error correction performance of LDPC decoding algorithms have inevitably faced the trade off on increased computational complexity. From hardware implementation and practical use perspectives, the increase in computational complexity results with increased demand for hardware resources. Therefore, these implementations, even though algorithmically efficient and highly parallelizable, become less scalable and harder to deploy as a component in systems designed for emerging standards that require longer codewords [33], [34], [35], [36]. We believe that there is a need for algorithms that target resource efficiency, scalability and error correction performance metrics concurrently. Among the hard-decision class of LDPC algorithms, hardware realization of the GaB has not been favorable due

to its poor decoding performance. On the other hand, GaB is an ideal candidate for designing a high-throughput decoder due to its simplicity of computations requiring combinational circuits at the scale of only 2-bit multiplication operations [28], [37]. Rapid evaluation of the LDPC algorithms and decoders while maintaining the trade-off between the hardware implementation efficiency and error correction performance becomes critical during this research. Therefore, this dissertation is concerned with a) improving the error correction performance of the GaB algorithm through algorithmic contributions without sacrificing its hardware efficiency, b) improving the scalabality of the GaB hardware architecture to make it feasible to implement for longer codewords, and c) implementation of a general purpose Field Programmable Gate Array (FPGA) based framework to accelerate the simulations of hard-decision decoders for error correction performance analysis.

#### 1.3 Summary of Contributions

#### 1.3.1 Algorithmic Contribution

In this dissertation, our aim is to answer the question of whether it is feasible or not to bridge the gap between GaB and better performing hard-decision (bit flipping) based algorithms in terms of decoding performance without sacrificing its suitability for hardware implementation. We introduce a new algorithm called Probabilistic Gallagher B (PGaB) by applying a probabilistic stimulation function over the iterative decoding process, conduct detailed experimental evaluations with respect to other decoders and show that our algorithm not only improves the decoding performance with respect to GaB by four orders of magnitude, but also requires fewest amount of hardware resources with respect to other comparable decoding algorithms GDBF and PGDBF while achieving equivalent or better decoding performance. We present the details of our incremental approach to designing and implementing the GaB and PGaB hardware architecture.

#### 1.3.2 Architecture Specific Contribution

The connection intensive bipartite graph based LDPC decoder hardware architecture creates routing stress when implemented on the FPGA for longer codewords that are utilized in today's communications systems and standards. From FPGA point of view, even though there is sufficient amount of computing resources that would match the degree of parallelism desired by the design, implementation is less likely to pass the routing stage of the synthesis as the number of connections in the implementation increase with the code length, which in turn increases the stress on FPGA routing resources. Another contributor to the routing stress is the number of parity bits used by the communication medium, which has direct impact on the number of connections between each iteration of the decoding process since increasing the ratio of parity bit to data from 0.5 to 0.75 would mean increasing number of connections by a factor of 4 for a given codeword. Therefore for implementations of longer codewords and/or higher code rates, designers resort to reducing the degree of parallelism in their implementations. We address the routability problem by partitioning each processing element (PE) in the bipartite graph based LDPC decoder hardware architecture in such a way that we distribute inputs of a PE evenly over its partitions. This allows depopulating the Look Up Table (LUT) resources available on the FPGA fabric utilized for the decoder architecture by spreading the logic across the FPGA. Spreading the logic across the FPGA allows reducing the stress on routing. We use the GaB decoder as a case study and show that even though LUT usage increases, critical path delay reduces with the depopulation. More importantly, with the depopulation technique, an unroutable design becomes routable, which allows longer codewords to be mapped on the FPGA.

#### 1.3.3 FPGA Based Framework

Evaluating the decoding performance of an LDPC code on a general purpose processor based single node requires extremely long simulation times, scaling to months and even years [38]. A typical simulation involves generating codewords (frames), injecting random errors to each, and measuring the ratio of codewords that are not recovered (frame error) to the total number of codewords tested. This ratio is referred to as the Frame Error Rate (FER). Many LDPC codes today reach to FER of  $10^{-12}$ , which indicates that  $10^{14}$  codewords have been tested and a benchmark of 100 codes were not corrected within a predefined number of iterations per codeword (typically 100 iterations). Therefore such simulations involve well beyond hundreds of millions of iterative error correction processes, and in most cases, the iteration count exceeds the billion mark for a conclusive evaluation at a resolution of  $10^{-12}$ . Furthermore, in parallel to the technological advances in communication systems, the length of codewords have been steadily increasing. The need for extremely high resolution simulations combined with growing codeword length trends lead to excessively long simulation times, which makes software based simulations unpractical for the information theory researchers. From this regard, we propose to design and implement a flexible FPGA based framework to rapidly evaluate a given decoder algorithm with user defined simulation parameters. Our aim is to reduce the time scale of simulations and further allow researcher to conduct analysis such as error pattern, trapping set, and absorbing set. We present our approach for implementing the entire simulation flow on the FPGA as a self contained testbed.

The technical contributions of this dissertation are as follows:

• We propose a resource efficient GaB architecture for widely used quasi-cyclic (QC)-LDPC codes, implement it on the FPGA, and evaluate its hardware performance.

- We analytically study the cases for which a message bit received from the channel becomes the determining factor in GaB for a decision made during the iterative decoding process. We introduce an algorithm that disturbs those decisions with a predefined probability, and experimentally identify the probability value that results with optimal decoder performance.

- We experimentally show that a simple hardware-friendly random number generator based on linear feedback shift register (LFSR) is sufficient to disturb the decoder and improve the decoding performance.

- We propose a heuristic that allows switching to PGaB only after when GaB is not able to correct the errors in predetermined number of iterations.

- We investigate the impact of switching from GaB to PGaB at a specific iteration, and experimentally identify the iteration number that results with optimal decoder performance.

- We design and implement GaB and PGaB along with two hard decision based algorithms (GDBF and PGDBF) on the Xilinx Virtex- 6 FPGA (vc6vlx240t-2ff1156).

- We conduct a detailed robustness analysis that involves evaluating the impact

of a change in code rate and codeword length over the FPGA based implementations of GaB, PGaB, GDBF and PGDBF covering 12 hardware implementations.

- We show that GaB architecture delivers the best throughput while using fewest FPGA resources, however performs the worst in terms of decoding performance.

The PGaB results with up to four orders of magnitude decoding performance improvement over the GaB, exceeding the performance of GDBF over the codes

studied in this dissertation, with a negligible loss (less than 1%) in throughput performance compared to the GaB.

- We analyze the critical path delay and resource usage trends for hardware implementations of the GaB algorithm with respect to the increase in codeword length.

- We show that routability becomes a bottleneck as the codeword length increases and adapt design partitioning technique to depopulate the logic across the FPGA and reduce congestion.

- We present an experimental analysis through resource usage, delay, and resource usage-delay product trends with respect to the amount of partitioning. We also correlate these trends with fracturable LUT utilization based on the level of partitioning and number of occupied paths.

- We propose a depopulation based hardware implementation technique and show that designs for the codewords that are not routable with the regular implementation become routable with the depopulation approach, while reducing the critical path delay by up 32% and increasing the LUT usage by 9%.

- We propose an FPGA based framework to accelerate the study of error correction performance analysis for LDPC codes. We present our approach to implementing the entire simulation flow on the FPGA as a self-contained framework in order to reduce the timescale of our simulations.

- Finally we present two case studies on investigating the error correction performance and the types of error patterns that are not recoverable by a given LDPC algorithm. We show that our testbed reduces the timescale of error correction performance simulations from an estimated time scale of 199 years on a CPU

to less than a day, and four error pattern analysis from an estimated time of 7800 days to less than five hours.

We believe that our self-contained FPGA based framework [39] is a valuable tool for information theorists to expose the weaknesses of a decoder algorithm under investigation through rapid error analysis and study ways to improve that decoding algorithm [40], [41]. The rest of this dissertation is organized as follows. In Chapter 2, we fist provide the background necessary for the discussions LDPC code, and then give an overview of the baseline GaB LDPC algorithm, along with the GDBF and PGDBF decoding algorithms. In Chapter 3, we present our methodology for introducing the probabilistic behavior to the GaB and determining the critical parameters for the PGaB implementation. In Chapter 4 we first discuss the hardware implementations for GaB, PGaB, GDBF, and PGDBF, and then we we evaluate the decoding performance and hardware performance of PGaB after giving an overview of our simulation environment. In Chapter 5, we investigate the congestion problem experimentally, introduce the partitioning approach for depopulating the logic, and conduct resource usage and path delay trend analysis to quantify the benefits of the depopulation strategy from FPGA implementation point of view. After discussing the details of our FPGA based framework in Chapter 6, we present our error correction performance and error pattern analysis case studies based on the proposed framework. Finally, in Chapter 7, we present our conclusions and future work.

#### Chapter 2

#### Preliminaries

In this chapter, we provide the background information necessary for discussion of the LDPC code.

#### 2.1 Overview of Decoding Algorithms

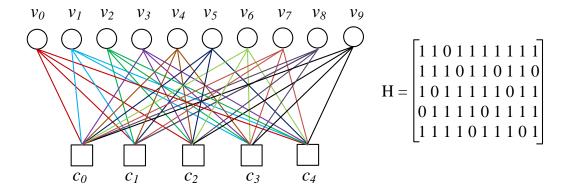

An LDPC code is defined by a sparse parity-check matrix H [2], with size (M, N), where N > M. A codeword is a vector  $\mathbf{x} = (x_1, x_2, \dots, x_N) \in \{0, 1\}^N$ , which satisfies  $H\mathbf{x}^T = 0$ . We denote by  $\mathbf{r} = \{r_1, r_2, \dots, r_N\} \in \{0, 1\}^N$  the output of a Binary Symmetric Channel (BSC), in which the bits of the transmitted codeword  $\mathbf{x}$  have been flipped with crossover probability  $\alpha$ . The graphical representation of an LDPC code is a bipartite graph called Tanner graph [42], [43] composed of two types of nodes including N number of Variable Node Units (VNUs,  $v_n$ ,  $n = 1, \dots, N$ ) and M number of Check Node Units (CNUs,  $c_m$ ,  $m = 1, \dots, M$ ). In the Tanner graph, a VNU  $v_n$  is connected to a CNU  $c_m$  when H(m, n) = 1. An example Tanner graph and its H

FIGURE 2.1. Tanner graph (left) and its parity check matrix (right).

matrix are shown in Figure 2.1. Let us also denote  $\mathcal{N}(v_n)$  the set of CNUs connected to the VNU  $v_n$ , with a connection degree  $d_v = |\mathcal{N}(v_n)|$ , and denote  $\mathcal{N}(c_m)$  the set of VNUs connected to the CNU  $c_m$ , with a connection degree  $d_c = |\mathcal{N}(c_m)|$ . Based on a decision function applied over the received messages from each adjacent vertex, each CNU and VNU sends a message back to its adjacent vertices. This iterative message processing between nodes recover the original data, which may have been exposed to channel noise.

#### 2.1.1 Gallager B (GaB)

Binary messages are exchanged between CNUs and VNUs during each iteration of the decoding process and new messages are computed in an extrinsic manner. A VNU excludes the message received from a CNU, when the VNU is calculating the message to be sent back to that specific CNU. This is valid for the message calculation for the CNU as well. Each message represents an estimation on the correctness of the received word from the channel. Eventually, VNUs and CNUs accumulate gradually more information with each new iteration, which increasingly improves the codeword correction capacity. The estimation of the codeword is called posteriori decision information and is represented by  $d_{n,m}^{(i)}$ . Let E(x) represent a set of edges connected to a node x in the Tanner graph. The  $v_{n,m}^{(i)}(e)$  denotes the extrinsic messages sent on edge e from a VNU  $v_n$  to a CNU  $c_m$  at iteration i and the  $c_{m,n}^{(i)}(e)$  represents the extrinsic messages sent on edge e from a CNU  $c_m$  to a VNU  $v_n$  at iteration i. The received word from the channel at a VNU  $v_n$  is denoted as  $r_n$ . We express the operation of VNU and CNU using Equations 2.1.1 and 2.1.2 respectively.

$$v_{n,m}^{(i)}(e) = \begin{cases} 1, & if \ r_n + (\sum_{e' \in \mathcal{N}(v_n) \setminus e} c_{m,n}^{(i)}(e')) > b_n \\ 0, & if \ r_n + (\sum_{e' \in \mathcal{N}(v_n) \setminus e} c_{m,n}^{(i)}(e')) < b_n \\ r_n, & otherwise \end{cases}$$

(2.1.1)

where i is the iteration count, e' is the set of extrinsic edges, and  $b_n$  is the threshold calculated as  $b_n = d_v/2$ .

$$c_{m,n}^{(i)}(e) = \left(\sum_{e' \in \mathcal{N}(c_m) \setminus e} v_{n,m}^{(i)}(e')\right) mod 2$$

(2.1.2)

At each iteration, a new value of posteriori decision  $d_{n,m}^{(i)}$  is computed as follows

$$d_{n,m}^{(i)} = \begin{cases} 1, & if \ r_n + (\sum_{e \in \mathcal{N}(v_n)} c_{m,n}^{(i)}(e)) > b_n \\ 0, & if \ r_n + (\sum_{e \in \mathcal{N}(v_n)} c_{m,n}^{(i)}(e)) < b_n \\ r_n, & otherwise \end{cases}$$

(2.1.3)

The GaB decoding process is shown in Algorithm 1. This iterative decoding process begins with sending the received message bit from each VNU to its CNUs defined by the *H matrix*. In a series of iterations CNUs and VNUs exchange information till a satisfaction criteria is met, which indicates successful recovery of the original data transmitted over a channel, which may have been exposed to errors due to noise. The CNU and VNU functions, satisfaction criteria, and connection topology among CNUs and VNUs determine nature of the LDPC algorithm. The VNU for GaB can be implemented using *Majority* gates (based on *and* and *or* logic functions only), and does not require complex operations such as the maximum finder required by the GDBF and PGDBF, along with the additional random number generator required by the PGDBF, which will be described in the following subsection.

#### 2.1.2 GDBF and PGDBF Analysis

The Gradient Descent formulation of Bit Flipping (BF) algorithm for the Binary Symmetric Channel (BSC) [31] sets a threshold for each VNU unit to determine whether the output of the VNU should be flipped or not based on an energy objective function. Energy objective is an integer value that varies between 0 and  $d_v + 1$  and results with fewer number of flips in the successive iterations of the decoding

#### Algorithm 1 Gallager B

```

i = 0, \ v_{n,m}^{(0)}(e)_{e \in \mathcal{N}(v_n)} \leftarrow r_n, \ n = 1, \dots, N.

Initialization

d_{n,m}^{(0)} \leftarrow r_n, \ n = 1, \dots, N.

s = H\mathbf{v}^{(0)^T} \mod 2

while s \neq 0 and i \leq i_{max} do

for n = 1, \ldots, N do

Compute

c_{m,n}^{(i+1)}(e)_{e \in \mathcal{N}(c_m)} using Equation 2.1.3

v_{n,m}^{(i+1)}(e)_{e \in \mathcal{N}(v_n)} using Equation 2.1.1

d_{n,m}^{(i+1)} using Equation 2.1.2

end for

s = H\mathbf{v}^{(i+1)^T} \mod 2

i = i + 1

end while

\mathbf{v}^{(i)}

Output:

```

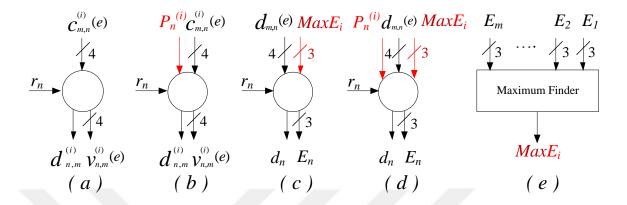

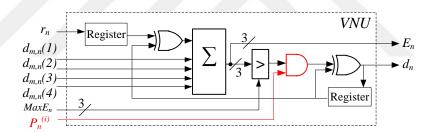

process. Due to the integer representation of energy function, several VNUs may share the same maximum of energy value resulting with several bits to be flipped in one iteration. This may induce a negative impact on the convergence of the algorithm [32]. The Probabilistic GDBF (PGDBF) has been proposed to flip the outputs of only a random number of those VNUs with the maximum energy value. Energy calculations for the GDBF and PGDBF are governed by expressions similar to Equations 2.1.1 and 2.1.2 [31], but they involve finding the maximum value across all VNUs in each iteration of the decoding process as illustrated in Figure 2.2. This gradient descent algorithm used in the PGDBF increases hardware complexity of PGDBF. On the other hand, the VNU for GaB can be implemented using majority logic and xor gates and does not require complex operations. Later in section 4.1.2, we will show that the maximum energy computation is the main bottleneck on the throughput performance of GDBF and PGDBF implementations.

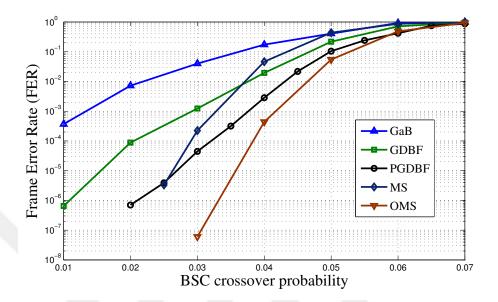

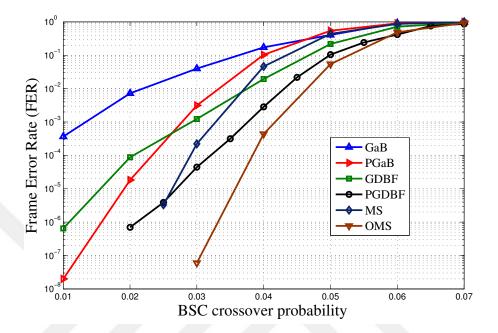

In Figure 2.3, the evolution of hard decision LDPC decoding algorithms is presented in term of error correction performance. Figure 2.3 shows the FER performance of three decoding algorithms, GaB, GDBF, and PGDBF, based on simulations

FIGURE 2.2. General architecture of VNUs for (a) GaB, (b) PGaB, (c) GDBF, and (d) PGDBF for dv = 4 and N = 1296. (e) Maximum finder unit for GDBF and PGDBF decoders.

conducted for codeword length N of 1296 bits. In this figure, we show FER curve of the MinSum (MS) and Offset MinSum (OMS) [27] based decoder even though they are different class of decoder algorithm, where CNUs and VNUs exchange messages of multi-bit granularity, as opposed to the bit flip class of algorithms with single-bit granularity that are considered in this dissertation. We include the MS and OMS in the figure to set the stage on where the hard-decision (bit flip) based algorithms stand with respect to this best performing soft-decision decoder. As shown from the Figure 2.3, GaB is the worst performing among the four algorithms. Based on the scale and nature of the arithmetic operations involved during each iteration of the decoding process, GaB method is the most hardware friendly among the three algorithms, requiring combinational circuits at the scale of only 2-bit multiplication operations. Given the codeword length is N, the GDBF design requires N number of 3-bit maximum finder components, which returns the maximum of all. Additionally, the PGDBF design incorporates a 32-bit LFSR-based (Linear Feedback Shift Register) random number generator. We observe that as the complexity of the computation units increases, the performance of the decoding algorithm improves significantly compared to GaB. Unlike other methods, hardware realization of GaB has not been

FIGURE 2.3. The evolution of decoding algorithms in term of error correction performance. GaB, GDBF, PGDBF, MS, and OMS FER comparison: FER vs. probability of error introduced to each bit of the 1296-bit codeword with  $d_v = 4$ ,  $d_c = 8$ , M = 648, and Code Rate = 0.5.

desirable due to its poor decoding performance, and its application is limited to environments that require fast execution. Given that GaB offers speed advantage over the other methods, in this dissertation our aim is to answer the question of whether it is feasible or not to bridge the gap between GaB and better performing algorithms without sacrificing its throughput performance.

#### Chapter 3

## PROBABILISTIC GAB ALGORITHM

In this chapter, we introduce a Probabilistic GaB (PGaB) algorithm by applying a probabilistic stimulation function over the iterative decoding process. We present the details of our incremental approach to designing and implementing the PGaB hardware architecture.

In order to improve the GaB decoding performance, we first analytically study the cases for which a message bit received from the channel becomes the determining factor in GaB for a decision made during the iterative decoding process. We then introduce an algorithm that disturbs those decisions with a predefined probability, which we refer to as  $p_v$ . We experimentally identify the  $p_v$  that results with preferable decoder performance.

In order to reduce the hardware cost and improve the throughput of the implementation, we first show that, rather than using a complex and hardware demanding random number generator, using a less sophisticated random number generator based on the linear feedback shift register (LFSR), which requires fewer hardware resources, is sufficient to improve the decoding performance. We then propose a heuristic that allows switching to PGaB only when GaB is not able to correct the errors in predetermined number of iterations. We investigate the impact of switching from GaB to PGaB at a specific iteration, which we refer to as  $s_i$ . We experimentally identify the  $s_i$  that results with preferable decoder performance, and show that when  $s_i$  is set to fifteen, we also drastically reduce the average iteration count by up to 62% compared to GaB.

#### 3.1 Probabilistic GaB Algorithm Methodology

During the decoding process, the interactions between CNUs and VNUs may result in an oscillation phenomena due to the  $n^{th}$  order dependencies between CNUs and VNUs. In such cases, the decoding process may get trapped in a cyclic behavior. For example, in the Tanner graph [43] given in Figure 2.1,  $c_0$  transmits message to  $v_1$  and  $v_3$ . After receiving their inputs from all CNUs,  $v_1$  and  $v_3$  send their messages back to their designated CNUs. In this example, there is a third order dependency between  $c_0$  and  $v_0$  based on the message passing in the order of  $(v_0 - c_0 - v_5 - c_4 - v_3 - c_3 - v_2)$ . If we count each CNU-VNU interaction as one iteration, then it would take three iterations for the message of  $c_0$  to propagate to  $v_0$ . Similarly, there is also a second order dependency in the order of  $(c_0 - v_1 - c_1 - v_0)$ . During each iteration, CNUs and VNUs update their states. The sequence of states observed for a given VNU may show repeating pattern, which is called a trapping set [44]. Trapping means that the decoder cannot correct the error, and then it remains in the cyclic sequences of states. One way to break this cyclic behavior is to disturb the VNU when such a pattern is detected. One may introduce large memory to keep track of the states, but that would not be hardware friendly, since the trapping set size is unknown and there can be many thousands of different trapping sets. Therefore, we randomly disturb the state of each VNU to be able to escape from the trapping set. Of course, one may question that such disturbance could adversely affect the normal behavior of the VNU, but theoretical results indicate that this side effect does not significantly increase the number of iterations [45], [46], [47]. If the GaB decoder does not converge within user-defined number of (k) iterations, then we apply this probabilistic strategy (Probabilistic GaB) to escape from trapping set. We modify Equation 2.1.1 by introducing a probability function  $p_n^{(i)}$  as shown in Equation 3.1.1. The PGaB flow is shown in Algorithm 2.

$$v_{n,m}^{(i)}(e) = \begin{cases} 1, & if \ p_n^{(i)} \oplus r_n + (\sum_{e' \in \mathcal{N}(v_n) \setminus e} c_{m,n}^{(i)}(e')) > b_n \\ 0, & if \ p_n^{(i)} \oplus r_n + (\sum_{e' \in \mathcal{N}(v_n) \setminus e} c_{m,n}^{(i)}(e')) < b_n \\ r_n, & otherwise \end{cases}$$

(3.1.1)

#### Algorithm 2 Probabilistic Gallager B

```

Initialization i=0,\ v_{n,m}^{(0)}(e)_{e\in\mathcal{N}(v_n)}\leftarrow r_n,\ n=1,\ldots,N.

d_{n,m}^{(0)}\leftarrow r_n,\ n=1,\ldots,N.

s=H\mathbf{v}^{(0)^T}\ \mathrm{mod}\ 2

while s\neq 0 and i\leq i_{max} do

Generate p_n^{(i)},\ n=1,\ldots,N, from \mathcal{B}(p_v).

for n=1,\ldots,N do

Compute c_{m,n}^{(i+1)}(e)_{e\in\mathcal{N}(c_m)} using Equation 2.1.3 v_{n,m}^{(i+1)}(e)_{e\in\mathcal{N}(v_n)} using Equation 3.1.1 d_{n,m}^{(i+1)} using Equation 2.1.2 end for s=H\mathbf{v}^{(i+1)^T}\ \mathrm{mod}\ 2 i=i+1 end while Output: \mathbf{v}^{(i)}

```

#### 3.1.1 Determining How to Disturb the VNU

The truth table shown in Table 3.1 captures how we propose to modify the VNU function with an example on calculating only one of the output messages  $(v_{n,m}^{(i)}(4))$ . In this example we assume that the  $d_v$  is four where each VNU has five inputs including the received word  $(r_n)$  and four CNU messages  $(c_{m,n}^{(i)}(1,2,3,4))$ . Since in this example we are calculating the message for the fourth output of the VNU, message  $(c_{m,n}^{(i)}(4))$  received from CNU is not used in the calculation.

Table 3.1. Truth Table for PGaB Algorithm

| Inputs for VNU |                    |                    | GaB                | PGaB               |                    |

|----------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| $r_n$          | $c_{m,n}^{(i)}(1)$ | $c_{m,n}^{(i)}(2)$ | $c_{m,n}^{(i)}(3)$ | $v_{n,m}^{(i)}(4)$ | $v_{n,m}^{(i)}(4)$ |

| 0              | 0                  | 0                  | 0                  | 0                  | 0                  |

| 0              | 0                  | 0                  | 1                  | 0                  | 0                  |

| 0              | 0                  | 1                  | 0                  | 0                  | 0                  |

| 0              | 0                  | 1                  | 1                  | 0                  | 1                  |

| 0              | 1                  | 0                  | 0                  | 0                  | 0                  |

| 0              | 1                  | 0                  | 1                  | 0                  | 1                  |

| 0              | 1                  | 1                  | 0                  | 0                  | 1                  |

| 0              | 1                  | 1                  | 1                  | 1                  | 1                  |

| 1              | 0                  | 0                  | 0                  | 0                  | 0                  |

| 1              | 0                  | 0                  | 1                  | 1                  | 0                  |

| 1              | 0                  | 1                  | 0                  | 1                  | 0                  |

| 1              | 0                  | 1                  | 1                  | 1                  | 1                  |

| 1              | 1                  | 0                  | 0                  | 1                  | 0                  |

| 1              | 1                  | 0                  | 1                  | 1                  | 1                  |

| 1              | 1                  | 1                  | 0                  | 1                  | 1                  |

| 1              | 1                  | 1                  | 1                  | 1                  | 1                  |

In GaB algorithm,  $v_{n,m}^{(i)}(e)$  is calculated by Equation 2.1.1 and is illustrated in Table 3.1. CNU messages  $(c_{m,n}^{(i)}(1,2,3))$  represent whether the previous decision of VNU is correct or not. We take a close look at the GaB VNU logic for the cases where there is a tie over the three inputs  $(c_{m,n}^{(i)}(1), c_{m,n}^{(i)}(2), c_{m,n}^{(i)}(3))$  and the received message  $(r_n)$ . In such cases, shown with rows in bold in Table 3.1, the VNU output is determined by the  $r_n$  input. We argue that when the decoder is stuck in the trapping set, we should not use the  $r_n$  as a determining factor. Looking closely, when we express  $v_{n,m}^{(i)}(4)$  for the PGaB (column 5) of Table 1, we see that function is equivalent to  $c_{m,n}^{(i)}(2).c_{m,n}^{(i)}(3) + c_{m,n}^{(i)}(1).c_{m,n}^{(i)}(3) + c_{m,n}^{(i)}(1).c_{m,n}^{(i)}(2)$ , and shows that we

ignore the received message for all input scenarios. If we ignore the received messages completely, decoder will fail. If we force all VNUs to rely on the received messages from the channel for the tie cases, then for the trapping set cases the decoder may not converge. The decoder cannot ignore the received messages, however during the decoding we do not know which VNU is in the trapping set. For this we introduce a mechanism that selects a predefined percentage of VNUs to ignore the received message and operate as the PGaB column of Table 3.1. We refer to predefined percentage of VNUs as the  $p_v$  term in our implementation. The subset of VNUs that ignore the received message is randomly chosen based on the  $p_v$  value. In the following section we present our experimental approach for determining the value of  $p_v$ . The probability function can be applied to the decoder in various positions. For example, in the PGDBF decoder [48], [49] the probabilistic function is applied randomly during the final output decision of a VNU to decide whether to flip the channel value or not. In the Noisy GaB [50], the randomness effect acts arbitrarily on both messages exchanged mutually between VNU and CNU. The main objective of these these studies is to distract the decoder by adding noise. Our approach to utilization of randomness is different from these studies as we attempt to use randomness in a more deterministic way. Rather than disturbing the outcome of decisions made during each iteration, we incorporate randomness directly into the message computation only for the cases when a tie occurs among the received messages of a VNU. Our Monte-Carlo simulations show better decoding performance, for the studied LDPC codes, when we introduce randomness as a tie-breaker for the VNU function when computing only messages sent from VNU to CNU. In the following subsection we present our approach for determining the  $p_v$  value.

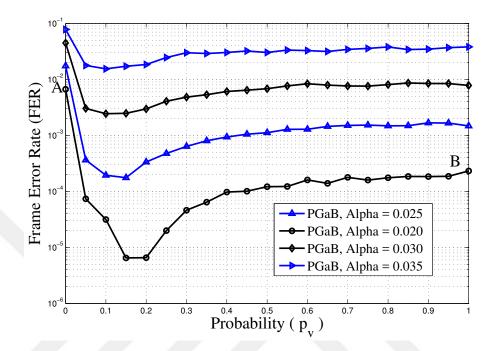

#### 3.1.2 Determining the $p_v$ Value

Before proceeding to the hardware implementation, we need to determine Bernoulli distribution  $p_v$ , which represents the probability of  $p_n^{(i)}$  taking the value of 1 ( $P(p_n^{(i)} = 1)$ ). This will indicate the proportion of VNUs that will be disturbed in the hardware architecture. In this case, setting  $p_v$  to 0 would mean no disturbance for all VNUs. We conduct experiments, as shown in Figure 3.1, for four values of channel crossover probability  $\alpha$  (0.025, 0.02, 0.03, and 0.035) by sweeping the  $p_v$  between 0 and 1. We choose four  $\alpha$  values in order to check the consistency on the FER performance. In the figure, x-axis shows the range of  $p_v$  being 1 and y-axis shows the frame error rate for the LDPC codeword length of 1296 with degrees of VNU and CNU set to 4 and 8 respectively. As shown in Figure 3.1, for the case of alpha 0.02, the simulation point labeled with A indicates no stochastic behavior (GaB) where  $p_v$  is 0 and the point labeled with B shows the case where all VNUs operate as PGaB where  $p_v$  is 1.

Based on the plots in Figure 3.1, we conclude that disturbing all VNUs results with an improvement over the GaB (point B). We observe two trends in the figure that reveal important insights for determining the  $p_v$ . As the  $p_v$  value reduces to 0.4, the FER is almost insensitive to this change for both  $\alpha$  values. We also observe a flood region between 0.1 and 0.2 where FER performance is the best for both  $\alpha$  values. Based on this observation we set the  $p_v$  value to 0.2 for the hardware implementation. This leads us to selecting a random number generator (RNG) for generating the  $p_v$  with Bernoulli distribution. Random number generators have been studied in terms of their quality and complexity in the literature extensively [51]. For example, the Park-Miller [52] algorithm is one of the high quality random number generators that relies on linear congruential method, which would require complex hardware components. Therefore this type of RNG even though generates strong random numbers is not hardware friendly. Our design choice favors simplicity with the objective of a light-weight decoder architecture in terms of its hardware resource

FIGURE 3.1. Frame Error Rate versus  $p_v$  ( $\alpha = 0.02, 0.025, 0.03,$  and 0.035). LDPC code ( $d_v = 4, d_c = 8, Z = 54$ ), (N = 1296, M = 648) when switching iteration  $s_i$  is set to 15.

requirement. We argue that, in our case there is no need for a sophisticated RNG in the hardware implementation that gives precise distribution for a given  $p_v$ . This is because, for all cases where  $p_v$  is set to a non-zero value, we observe improvement over the GaB and the preferable performance occurs in a window ranging between 0.1 and 0.2. We use this conclusion as basis for choosing a simpler and hardware friendly linear feedback shift register (LFSR) based RNG.

#### 3.1.3 Determining the $s_i$ Value

In section 3.1.1 we discussed the way we introduce probabilistic behavior to GaB to overcome trapping sets. Based on our simulations, we observe that GaB when successfully decodes a code, typically resolves the errors in less than ten iterations. Therefore we believe that a hybrid implementation that switches to PGaB only when GaB is not able to correct the errors in predetermined number of iterations would

FIGURE 3.2. Frame Error Rate and Average iteration versus iteration number to switch from GaB to PGaB (QC-LDPC codes with  $(N, d_v, d_c, R)$  configurations of (155, 3, 5, 0.5), (1296, 3, 6, 0.5) and (1296, 4, 8, 0.5)).

be a better approach than executing only PGaB in terms of FER performance. We conduct two experiments to validate our claim.

In the first experiment, we evaluate the impact of switching from GaB to PGaB after a specific number of iterations ( $s_i$ ) for three regular LDPC codes with (N,  $d_v$ ,  $d_c$ , R) configurations of (155, 3, 5, 0.5), (1296, 3, 6, 0.5) and (1296, 4, 8, 0.5). We vary the switching point from 5 to 50 and show the FER performance for different  $\alpha$  values for each code shown in Figure 3.2. In the same plot we also plot the average number of iterations for three  $\alpha$  values. For all experiments, we set the maximum number of iterations to 300. We evaluate the impact of change in codeword length on switching iteration using codeword length of 155 and 1296; and the impact of change in VNU and CNU degree using codes with connection degree  $d_v$  set to 3 and 4, and  $d_c$  set to 5, 6, and 8. All of these experiments indicate that setting the switching point between 15 and 20 iterations would be preferable for achieving better FER performance. Since

FIGURE 3.3. Comparison of average number of iterations for PGaB, GaB, PGaB Hybrid (GaB for the first 15 iterations, and PGaB onwards) ( $d_v = 4, d_c = 8, N = 1296, M = 648$ ).

the average number of iterations for three  $\alpha$  values show an increasing trend as the switching point moves from 5 to 50, we conclude that 15 is the ideal point to make the switching from GaB to PGaB. A side benefit of switching after 15 iterations is the reduced power consumption since we dont use PGaB for all iterations and in hardware implementation we turn on the the RNG unit only after iteration count 15 has been reached.

In the second experiment, we set the switching point to 15 and  $p_v$  value to 0.2, and evaluate the impact of disturbing VNUs on average number of iterations. In Figure 3.3, we compare average number of iterations for the baseline GaB, the PGaB, and the hybrid implementation that relies on the execution of GaB for the first 15 iterations of the decoding process and PGaB afterwards. In the figure, x-axis shows the  $\alpha$  range and y-axis shows the average number of iterations for three simulations. Figure shows that when we start using the PGaB after 15 iterations, the average number

of iterations is always better than the deterministic GaB. We reduce the average iteration count by 40%, 56%, 62%, 54%, and 26% compared to the GaB for the  $\alpha$  values studied in this experiment respectively. The PGaB only approach consistently results with larger number of iterations compared to the GaB only method. Disturbing the decoder starting with the first iteration results with adding more noise and therefore leads to increase in the average number of iterations. The hybrid PGaB on the other hand reduces the average number of iterations consistently with respect to the GaB only method. We believe that disturbing the GaB decoder after 15 iterations helps resolve some of the trapping set cases as shown theoretically by Ivanis and Vasic [50], which contribute to the increase in average number of iterations for the GaB only method. Reducing the maximum iteration count has also direct impact on the power consumed by the decoder. By reducing average iteration number, we also increase the throughput of the decoder. PGaB spends fewer iterations in average compared to the GaB to correct the errors.

In the following chapter we will present our hardware results and decoding performance based on the hybrid PGaB implementation where we set  $p_v$  value to 0.2 and the  $s_i$  to 15. For the remainder of the this dissertation we refer to the hybrid PGaB as the PGaB. We will compare the decoding performance of the PGaB with GaB, GDBF, PGDBF, and MinSum based on the FER performance for each code studied in this dissertation. We will show that the PGaB results with up to four orders of magnitude decoding performance improvement over the GaB.

#### Chapter 4

#### HARDWARE DESIGN OF LDPC DECODERS

In this chapter, we present the details of hardware implementations for GaB, PGaB, GDBF, and PGDBF LDPC decoders. We show that GaB architecture delivers the best throughput while using fewest FPGA resources, however performs the worst in terms of decoding performance. We compare the decoding performance of the PGaB with GaB, GDBF, and PGDBF based on the FER performance. We show that the PGaB results with up to four orders of magnitude decoding performance improvement over the GaB, exceeding the performance of GDBF over the codes studied in this dissertation, with a negligible loss (less than 1%) in throughput performance compared to the GaB. We conclude that the PGaB is able to bridge the gap between GaB and complex decoding algorithms such as GDBF and PGDBF without sacrificing the throughput advantage of the GaB by consistently exceeding FER performance of the GDBF.

### 4.1 Hardware Design

#### 4.1.1 GaB and PGaB Hardware Design

We first show the generic architecture for GaB and PGaB with VNUs, CNUs and the H matrix based on a regular QC-LDPC code for codeword length (N) in Figure 4.1(a). The *Compute Syndrome* unit in the figure checks whether all of the CNUs are satisfied or not.

We show the details of the VNU architecture for  $d_v$  equals to 4 in Figure 4.1(c). The colored arrows along with the *and* and *xor* gates in the VNU architecture are used by the PGaB implementation. When  $d_v$  is set to 4, besides the control input

FIGURE 4.1. Overall decoder architecture (a) for PGaB, VNU architecture for dv4 (c) and LFSR-32bits based Random Number Generator (b).

(ctrl), there are six 1-bit inputs for each VNU. The first two inputs from top to bottom are 1-bit data received from the channel  $(r_n)$  and 1-bit random value  $(P_n^{(i)})$  generated by the LFSR based RNG. Remaining four inputs  $(c_{m,n}^{(i)}(1), c_{m,n}^{(i)}(2), c_{m,n}^{(i)}(3), c_{m,n}^{(i)}(4))$  are the 1-bit messages received from CNUs (as  $d_v = 4$ ). There are four 4-input majority voter units (labeled as 1-4) and one 5-input majority voter unit (labeled as 0). The majority voter generates a 2-bit output representing majority of 1s, majority of 0s, or tie cases. The select unit acts as a selection of the majority output, which generates 1 for the majority of 1s case, and 0 for the majority of 0s case. In the case of a tie, the select unit passes the received word to its output. In this generic architecture, if the  $d_v$  changes than the number of Majority Voters and the number of inputs need to be adjusted properly. For example, when  $d_v$  is set to three, the input  $(c_{m,n}^{(i)}(4))$ , output  $(v_{n,m}^{(i)}(4))$ , and components (Majority Voter 4 and Select for  $v_{n,m}^{(i)}(4)$  output) marked with dotted lines are excluded from the VNU. We implement a regular majority voter based on Table I. We do not show the details of the Majority Voter architecture, since it is straightforward to implement. The VNU

operation is modified with the red marked lines and glue logic to adopt its function to PGaB. The control bit (ctrl) sets the first input of the xor gate to 0 if the algorithm is GaB, in which the xor gate passes the  $r_n$  input to its output, otherwise the output becomes a function of  $r_n$  and the  $P_n^{(i)}$  for implementing the PGaB. A state machine controls switching between GaB and PGaB. After iteration number 15, if the decoder does not converge, the control bit (ctrl) is set to 1 by the state machine to switch to PGaB. The controller allows us to use VNU architecture of GaB to implement PGaB. Based on our conclusion about the RNG type to utilize in Section III.B, we implement a regular LFSR based RNG, shown in Figure 4.1(b) to feed a 1-bit random value to each VNU. We implement 32-bit LFSR to generate a 32-bit random number. The 32 bits Logic Comparator compares 32-bit random number with the user defined Threshold value determined in Section 3.1.2. Finally, the output of the comparator, a one bit random number, is stored in the shift register. If the codeword length is N, then the RNG will take N number of cycles to generate the bits needed by all the VNUs. This N cycle overhead is applied only once during the first iteration of the decoding. During the subsequent iterations between the CNUs and VNUs, we simply generate one bit and use a shift register of size N to distribute the values to each VNU.

We do not show the details of the CNU architecture, since it is straightforward to implement. When  $d_c$  is set to 8, inputs are eight bit messages  $v_{n,m}^{(i)}(e)$ , and eight bit decision information  $(d_{n,m}^{(i)})$  received from the VNUs. The outputs of a CNU are an eight bit message  $(c_{m,n}^{(i)}(e))$  and one bit decision information  $(d_{m,s}^{(i)})$ . The  $d_{m,s}^{(i)}$  is the output of the xor operation on the 8-bit input  $d_{n,m}^{(i)}$ . Decision information is sent to the ComputeSyndrome unit to decide whether the decoder has converged or not. Message calculation is different than decision information calculation as it is executed in an extrinsic manner. The  $c_{m,n}^{(i)}(e)$  is calculated by Equation 2.1.2. For instance,  $c_{m,n}^{(i)}(1)$  is determined by calculating the xor of messages  $v_{n,m}^{(i)}(2),...,v_{n,m}^{(i)}(8)$  and excludes the  $v_{n,m}^{(i)}(1)$ . In summary, the CNU implementation requires one 8-bit

FIGURE 4.2. Architecture of GDBF and PGDBF for  $d_v = 4$ , and N = 1296, where dc is determined by the code rate.

FIGURE 4.3. Architecture of VNU for GDBF and PGDBF for  $d_v = 4$ , and N = 1296. xor gate and eight 7-bit xor gates.

### 4.1.2 GDBF and PGDBF Hardware Design

In order to present a comprehensive analysis on the decoding and hardware performance of PGaB, we implement two hard-decision based algorithms (GDBF and PGDBF). In this section, we present hardware implementations for these two algorithms. High level architectures for the GDBF and PGDBF decoders are shown in Figure 4.2 for a QC-LDPC code with codeword length of 1296 bits ( $d_v = 4$ ,  $d_c = 8$ ). The only difference between GDBF and PGDBF architectures is the binary RNG indicated with the dotted lines in Figure 4.2. The RNG generates 1296 binary 1-bit

Table 4.1. Hardware Resource Utilization, Throughput and Clock Rate of Decoding Algorithms Implemented for Tanner Code on Virtex6 FPGA

| Algorithm   | 1-bit    | Slice | Fmax  | Throughput |

|-------------|----------|-------|-------|------------|

| Aigortiiiii | register | LUTs  | (MHz) | (Mbps)     |

| GDBF* [48]  | 946      | 2151  | 132.7 | 4114.3     |

| PGDBF* [48] | 9161     | 3545  | 135.6 | 4202.5     |

| MinSum [48] | 13694    | 15350 | 237.2 | 197.5      |

| GDBF        | 502      | 1630  | 137.5 | 4263.4     |

| PGDBF       | 687      | 1802  | 138.2 | 4285.8     |

random numbers  $(P_n^{(i)})$  to distribute to each VNU. Detailed architecture for the VNU is shown in Figure 4.3. The 1-bit received message  $(r_n)$  from the channel, the 1-bit decision estimations from the four CNUs  $(d_{m,n}(e))$ , and the 3-bit maximum energy value for the current iteration  $(MaxE_n)$  are common inputs for the VNU in GDBF and PGDBF. The summation operation in the VNU calculates the output energy value  $(E_n)$ , which can be between zero and five. Therefore bit-width for the  $E_n$  and  $MaxE_n$  are set to three bits. The Maximum Finder unit shown in Figure 4.2 computes the maximum of the  $E_n$  values received from each VNU in the current iteration i labeled as  $MaxE_n$  in the figure. Each VNU uses the  $MaxE_n$  and  $E_n$  to generate a 1-bit decision value  $(d_n)$ . In the same iteration, if the  $E_n$  of a VNU is equal to the  $MaxE_n$ , then the output message  $d_n$  is flipped. If the  $E_n$  is less than the  $MaxE_n$ , then the  $d_n$  is not flipped. Additionally, for the PGDBF, a VNU receives a 1-bit random value generated by the LFSR based RNG  $(P_n^{(i)})$ . The  $d_n$  is a new message for all CNUs connected to the VNU. This iterative process continues till all CNUs are satisfied. A 1-bit message is sent by CNU to Compute Syndrome unit indicating whether a CNU it is satisfied or not. A state machine controls the Compute Syndrome unit to make a decision on whether the decoder has converged or not.

The hardware implementations for the GDBF and PGDBF have been studied

```

Algorithm 3 Simulation flow for generating FER plots

Input

: Decoding Algorithm (GaB, PGaB, GDBF, PGDBF), Codeword

length of 1296 (code rate 0.5 and 0.75) and Codeword length of

2212 (code rate 0.857) and Crossover Probability (\alpha)

Output

: FER plot of each algorithm over \alpha

1 foreach Decoding Algorithm do

foreach Code do

FrameCounter = 0;

foreach \alpha do

# \alpha \in [0.001, 0.07] for N = 1296, rate 0.5

\# \alpha \in [0.02, 0.03] \text{ for } N = 1296, \text{ rate } 0.75

# \alpha \in [0.005, 0.6] for N = 2212, rate 0.857

ErrorCount = 0;

while (ErrorCount < 100) do

4

Generate a random codeword (Frame);

FrameCounter = FrameCounter + 1;

Add noise to Frame using \alpha;

Value = Decoding Algorithm();

# Value from Compute Syndrome

if (Value == 0) then

ErrorCount = ErrorCount + 1;

end

if ErrorCount == 100 then

FER = 100/FrameCounter;

\quad \text{end} \quad

end

Mark FER for \alpha on FER plot;

end

end

end

```

based on the Tanner code (N=155, M=93 ,  $d_v=3$  ,  $d_c=5$ ) in [48]. We first implement these two algorithms based on the same code and compare their hardware resource usage and throughput performance with the published results (indicated as \* in the table) on the Xilinx Virtex6 FPGA using Table 4.1. With this comparison, our aim is to show that our implementations form a credible baseline for our extensive performance evaluations in the following section across GaB, PGaB, GDBF and PGDBF over various code lengths and code rates. We include MinSum in the table just to highlight the hardware efficiency of the hard-decision based algorithms with respect to this best performing soft-decision decoder. As shown in the table, we reduce the 1-bit register usage significantly by 92% compared to the PGDBF\*. We also reduce the Slice LUT usage by 24% and 49% with our implementations of the GDBF and PGDBF respectively. The study by Le et. al. [48] reveals limited amount of information about the hardware implementation approach for the GDBF\* and PGDBF\*. We believe that there are two factors contributing to significant reduction on resource usage for our implementations. First, our CNU implementation does not require any register, as we implement it as a combinatorial logic and each CNU sends its output message  $d_{m,n}(e)$  back to the VNU without having to store it. Secondly, we take advantage of a resource efficient implementation of maximum finder logic as shown by [53] based on parallel tree structure for calculating the  $MaxE_n$ . Earlier we claimed that maximum finder unit was a critical factor on throughput performance of the GDBF. When we replaced the "Maximum Finder" logic with a hard coded maximum value in our version of the GDBF implementation, we observed a reduction in logic block resource usage by 14.7% and an increase in the maximum clock rate by a factor of 2.99x for this hypothetical implementation. Nevertheless, with our implementation by reducing the resource usage for GDBF and PGDBF significantly with a slight improvement in the maximum clock rate, we are setting a tighter constraint on measuring the hardware performance in terms of resource usage and throughput for the PGaB implementation.

#### 4.2 Simulation Environment