# **OPTIMIZATION METHODS IN HIGH-LEVEL SYNTHESIS**

# YÜKSEK SEVİYEDE SENTEZLEMEDE ENİYİLEME YÖNTEMLERİ

#### SELMA DİLEK

# PROF. DR. SÜLEYMAN TOSUN Supervisor

#### Submitted to

Graduate School of Science and Engineering of Hacettepe University

as a Partial Fulfillment to the Requirements

for the Award of the Degree of Doctor of Philosophy

in Computer Engineering

June 2022

#### **ABSTRACT**

#### **OPTIMIZATION METHODS IN HIGH-LEVEL SYNTHESIS**

#### Selma DİLEK

Doctor of Philosophy, Computer Engineering Supervisor: Prof. Dr. Süleyman TOSUN June 2022, 191 pages

Continuous decrease in the transistor technology sizes has enabled much denser packaging of electronic components on chips, which has resulted in integrated circuits with more functionalities and lower costs. However, it has also given rise to new issues and challenges in the integrated circuit design process, including higher vulnerability to soft errors. Modular hardware redundancy is a popular method for improving the reliability of a system against errors at the cost of increasing area and energy consumption. Voltage scaling methods can be employed to tackle high energy costs; however, these approaches also negatively affect a circuit's reliability and performance. Therefore, designing circuits with all these conflicting parameters is a very challenging task. In this study, we employ two optimization approaches: mathematical programming and metaheuristic algorithms for designing integrated circuits with several conflicting parameters. Mathematical programming approaches guarantee the generation of the optimal solutions; however, they are usually highly impractical for complex real-life problems due to their high computational complexity and unrealistically long running times. Nevertheless, the optimal solutions obtained for relatively small problem sizes are useful for testing the performance of other (meta)heuristic methods that solve the same problem in much faster execution times, although without any guarantees about solution optimality.

In this thesis, we propose integer linear programming (ILP)-based and simulated annealing (SA)-based high-level synthesis (HLS) methods to optimize both reliability and energy of the final circuit designs under the area and latency constraints. Our models employ full and partial resource duplication (modular redundancy) to improve the system reliability as long as the area constraint permits. They also utilize voltage islands as the energy reduction method of choice. This problem is even more interesting and complex because our resource library is characterized under multiple supply voltages. We use different versions of the same resources with different area, latency, reliability, and energy values. Although this affects the execution time of the proposed methods, it also gives us more design options. We compared and showed the effectiveness of our methods against a genetic algorithm (GA)-based method on several HLS benchmarks. The ILP-based methods return the optimum results for smaller problem sizes and most of the time for larger problem sizes under the given time limits. In contrast, the SA-based methods outperform the GA-based methods and generate optimal or acceptably near-optimal results for all benchmarks in much faster running times.

**Keywords:** High-level synthesis, application specific integrated circuits, soft errors, reliability, energy, voltage islands, optimization, metaheuristic algorithms, integer linear programming, simulated annealing.

## ÖZET

## YÜKSEK SEVİYEDE SENTEZLEMEDE ENİYİLEME YÖNTEMLERİ

#### Selma DİLEK

Doktora, Bilgisayar Mühendisliği Danışman: Prof. Dr. Süleyman TOSUN Haziran 2022, 191 sayfa

Transistor boyutlarındaki sürekli azalma, elektronik bileşenlerin yongalar üzerinde çok daha yoğun bir şekilde paketlenmesini sağlarken, daha fazla fonksiyon içeren ve maliyeti daha düşük tümleşik devrelerin geliştirilmesine yol açmaktadır. Bununla birlikte, teknolojideki bu gelişmeler tümleşik devre tasarımı sürecinde geçici hatalara karşı daha korumasız olunması gibi yeni sorunlar ve zorluklar da doğurmuştur. Bileşenlerin yedeklenmesi bir sistemin hatalara karşı dayanıklılığını artırmak için popüler bir yöntem olsa da alan ve enerji tüketimi artışına neden olmaktadır. Artan enerji tüketiminin üstesinden gelmek için gerilim ölçeklendirme yöntemi kullanılabilir, ancak bu yöntem devrenin güvenilirliğini ve performansını da olumsuz etkilemektedir. Bu nedenle, tüm bu çelişen değişkenlerle devre tasarlamak çok zorlu bir iştir. Bu çalışmada devre tasarlanırken birbirleriyle çelişen parametreleri göz önüne alan matematiksel programlama ve metasezgisel algoritmalar olmak üzere iki optimizasyon yaklaşımı kullanılmıştır. Matematiksel programlama yaklaşımları, optimum çözümlerin üretilmesini garanti eder. Fakat yüksek hesaplama karmaşıklıkları ve gerçekçi olmayan uzun çalışma süreleri nedeniyle, genellikle gerçek hayattaki karmaşık problemler için pratik değildirler. Bununla birlikte, nispeten küçük problem boyutları için elde edilen optimum çözümler, aynı problemi çok daha hızlı yürütme sürelerinde çözen diğer metasezgisel yöntemlerin performansını ölçmek için faydalıdır. Bunun yanında metasezgisel yöntemler çözümün en iyi çözüm olup olmadığı hakkında herhangi bir garanti vermezler.

Bu çalışmada, alan ve gecikme kısıtlamaları altında nihai devre tasarımlarının hem güvenilirliğini hem de enerjisini optimize etmek için tam sayı doğrusal programlama (ILP) tabanlı ve benzetimli tavlama (SA) tabanlı yüksek seviyede sentezleme (HLS) yöntemleri sunulmuştur. Modellerimizde sistem güvenilirliğini geliştirmek için alan kısıtlaması izin verdiği sürece tam ve kısmi kaynak çoğaltılması (modül yedekleme) kullanılmaktadır. Ayrıca, tercih edilen enerji azaltma yöntemi olarak gerilim adaları kullanılmaktadır. Bu sorunu daha da ilginç ve karmaşık yapan şey, çoklu besleme gerilimi altında kaynak kütüphanesinin tanımlanmasıdır. Kütüphanede aynı donanım kaynaklarının farklı alan, gecikme, güvenilirlik ve enerji değerlerine sahip farklı versiyonları kullanılmaktadır. Bu, önerilen yöntemlerin uygulama süresini etkilese de, daha fazla tasarım seçeneği de sunmaktadır. Sunulan yöntemlerin etkinliğini ölçmek için bazı HLS denektaşları kullanarak genetik algoritmaya (GA) dayalı bir yöntemle karşılaştırılmıştır. ILP tabanlı yöntemler küçük boyutlu problemler için optimum sonuçları verirken, çoğu zaman daha büyük çizge boyutları için verilen zaman sınırlarının altında optimum çözümleri bulabilmiştir. tabanlı yöntemler GA tabanlı yöntemlerden daha iyi performans göstermiş ve optimum veya optimuma yakın sonuçları çok daha hızlı bir şekilde elde etmiştir.

**Anahtar kelimeler:** Yüksek seviyede sentezleme, uygulamaya yönelik tümleşik devreler, geçici hatalar, güvenilirlik, enerji, gerilim adaları, eniyileme, metasezgisel algoritmalar, tam sayı doğrusal programlama, benzetimli tavlama.

#### **ACKNOWLEDGEMENTS**

In the name of God, the Most Gracious, the Most Merciful.

I would like to convey my deep appreciation to my advisor **Prof. Dr. Süleyman Tosun** for his invaluable guidance, wisdom, patience, and particularly his understanding and support, without which this endeavor would not have been possible. Words cannot express my gratitude to all my professors, the members of my thesis committee, the chair **Prof. Dr. Suat Özdemir** and the member of the committee **Prof. Dr. Özcan Öztürk**, for their invaluable feedback and generously provided knowledge and expertise.

Furthermore, this journey would not have been possible without the love and support of my beloved family, my mother **Amra Bjelanović**, my father **Husein Pilav** who gave me my first computer Commodore 64 that set me on this path, and my brothers **Semir** and **Omer**. I also thank **Dr. Alma Osmanović Salman**, **Amra Erdić**, and **Asma Aiouez** for being the sisters I never had, and my source of strength, as well as my true 'brother-from-another-mother' friends **Adnan** and **Tarik Kraljić**. Whenever I hit a rough patch throughout this journey, the thought of my late grandparents and uncle, who were such a great source of motivation and people to look up to, kept me going. **Mr. Ramo Krivdić** has been a loving and supportive 'grandpa' in their stead. Their love and boundless support have kept my spirits and motivation high during this process.

I would also like to extend my sincere thanks to my colleagues at Hacettepe Computer Engineering Department for their support and understanding, especially during the trying times of pandemics. I am deeply indebted to research assitants Necva Bölücü, Alperen Çakın, Burçak Asal, Burcu Yalçıner, Dr. Tuğba Gürgen Erdoğan, Zeynep Bala, Bahar Gezici, Merve Özdeş, Feyza Nur Kılıçaslan, Nebi Yılmaz, Asst. Prof. Dr. Alaettin Uçan, Asst. Prof. Dr. Pelin Canbay, and all other research assistants at our department for their invaluable support throughout this journey.

Special thanks are due to my dear professors and role models **Dr. Douglas Van Wieren**, **Prof. Dr. Ahmed Moosajee Patel**, **Assoc. Prof. Dr. Željko Jurić**, and **Mr. Nedim Mašić** who instilled in me appreciation and love for computer science and academia, and showed me what it means to be an excellent educator, and to my doctors **Prof. Dr. Murat Tuncer**, **Prof. Dr. Alper Demirbas**, and **Prof. Dr. Sabri Tekin**.

Finally, I would like to thank the Scientific and Technological Research Council of Turkey (TÜBİTAK) for supporting this research in part under project number 116E095, and Fair Isaac Corporation (FICO) for granting us an academic license for FICO Xpress optimizer that we used to run our ILP models.

I dedicate this work to my hero, my selfless brother **Semir Pilav**, who risked his life to save mine without forethought. I owe him my health and everything I have accomplished since he donated his kidney to save my life.

# **Contents**

| <u>P</u>                                                                         | age |

|----------------------------------------------------------------------------------|-----|

| ABSTRACT                                                                         | i   |

| ÖZET                                                                             | iii |

| ACKNOWLEDGEMENTS                                                                 | V   |

| CONTENTS                                                                         | vi  |

| TABLES                                                                           | ix  |

| FIGURES                                                                          | xii |

| ABBREVIATIONS                                                                    | XV  |

| 1. INTRODUCTION                                                                  | 1   |

| 1.1. Scope of the Thesis                                                         | 2   |

| 1.2. Contributions                                                               | 3   |

| 1.3. Organization                                                                | 5   |

| 2. BACKGROUND OVERVIEW                                                           | 6   |

| 2.1. Optimization Fundamentals                                                   | 6   |

| 2.2. Optimization Algorithms                                                     | 9   |

| 2.2.1. Linear Programming                                                        | 9   |

| 2.2.2. Metaheuristic Approaches for Discrete Optimization                        | 11  |

| 2.3. Reliability, Energy, and Latency Considerations for Optimization in Digital |     |

| Electronic System Design                                                         | 14  |

| 2.3.1. Soft Errors, Reliability, and Modular Redundancy                          | 14  |

| 2.3.2. Effects of Multi-Supply Voltages on Energy and Latency                    | 17  |

| 2.3.3. Effects of Multi-Supply Voltages on Reliability                           | 18  |

| 3. RELATED WORK                                                                  | 19  |

| 3.1. ILP-Based HLS Studies                                                       | 19  |

| 3.2. SA-Based HLS Studies                                                        | 23  |

| 3.3. HLS Studies With Modular Redundancy                                         | 29  |

| 3.4. HLS Under Multi-Supply Voltages and Other Energy-Aware Approaches           | 30  |

| 3.5. Other HLS-Related Studies                                                   | 31  |

| 4. | PROBLE    | EM DEFINITION                                                      | 33 |

|----|-----------|--------------------------------------------------------------------|----|

|    | 4.1. High | h-Level Synthesis                                                  | 33 |

|    | 4.2. Beh  | avioral Description of a Target Design                             | 36 |

|    | 4.3. Res  | ource Library Under Multi-Supply Voltages                          | 38 |

|    | 4.4. Mod  | dular Redundancy Considerations                                    | 39 |

| 5. | PROPOS    | SED METHODS                                                        | 42 |

|    | 5.1. Inte | ger Linear Programming Formulations                                | 42 |

|    | 5.1.1.    | Constraints                                                        | 47 |

|    | 5.1.2.    | Objective Functions                                                | 48 |

|    | 5.2. Sim  | ulated Annealing-Based HLS Method                                  | 50 |

|    | 5.2.1.    | Task Scheduling Algorithms                                         | 50 |

|    | 5.2.2.    | Initial and Neighbor Solution Generation with Resource Allocation  | 55 |

|    |           | Computing the Initial Temperature                                  |    |

|    | 5.2.4.    | Annealing Schedule                                                 | 63 |

|    |           | Additional Considerations for SA-Based HLS With Partial DMR        |    |

|    | 5.2.6.    | SA-Based HLS Algorithm                                             | 67 |

| 6. | EXPERI    | MENTAL RESULTS AND DISCUSSION                                      | 71 |

|    | 6.1. Con  | nparison of ILP and GA-Based Methods With DMR                      | 72 |

|    | 6.1.1.    | Reliability Optimization Results Discussion                        | 73 |

|    | 6.1.2.    | Energy Optimization Results Discussion                             | 75 |

|    | 6.1.3.    | Joint Reliability and Energy Optimization Results Discussion       | 77 |

|    | 6.2. Con  | nparison of SA-Based Method With ILP and GA-Based HLS Methods      | 79 |

|    | 6.2.1.    | Reliability Optimization Results Discussion                        | 80 |

|    | 6.2.2.    | Energy Optimization Results Discussion                             | 82 |

|    | 6.2.3.    | Joint Reliability and Energy Optimization Results Discussion       | 84 |

|    | 6.3. Con  | nparison of SA-Based Partial DMR HLS Method With the Corresponding |    |

|    | ILP       | and GA-Based Methods                                               | 86 |

|    | 6.3.1.    | Reliability Optimization Results Discussion                        | 87 |

|    | 6.3.2.    | Energy Optimization Results Discussion                             | 87 |

|    | 6.3.3.    | Joint Reliability and Energy Optimization Results Discussion       | 89 |

|    | 6.4. Effe | ects of Multiple Supply Voltages on Reliability and Energy Consumption  | 92 |

|----|-----------|-------------------------------------------------------------------------|----|

|    | 6.5. Exe  | cution Time Analysis                                                    | 97 |

| 7. | CONCL     | USION                                                                   | 02 |

| 8. | APPENI    | DICES                                                                   | 21 |

|    | APPENI    | OIX A - Mosel and C Implementations Source Code                         | 21 |

|    | A.1       | Mosel Code For ILP Formulation of the HLS Problem                       | 21 |

|    | A.2       | Mosel Code For ILP Formulation of the HLS Problem With Partial DMR . 12 | 26 |

|    | A.3       | Mosel Code For ILP Formulation of the HLS Problem With Full DMR 13      | 31 |

|    | A.4       | C Source Code For SA-Based HLS Method                                   | 36 |

|    | APPENI    | DIX B - Directed Acyclic Graphs for Benchmarks                          | 59 |

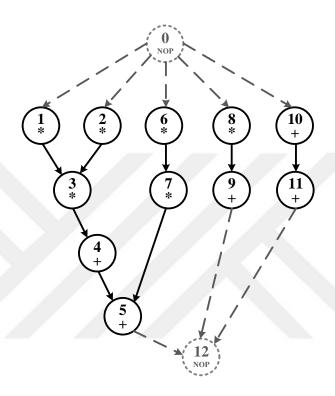

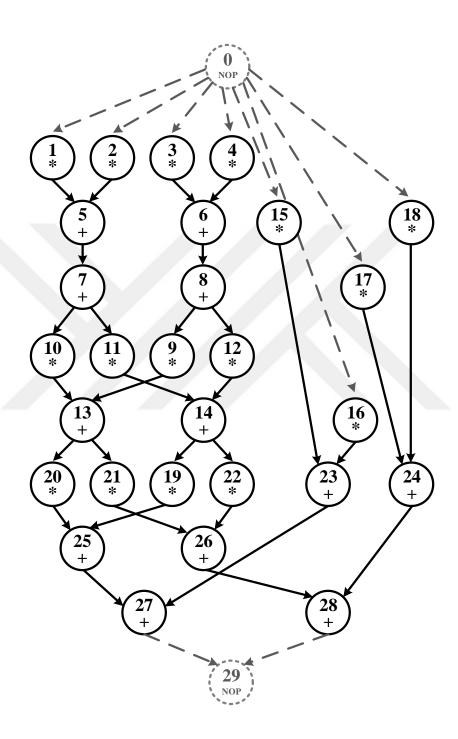

|    | B.1       | DAG of the Differential Equation Solver Benchmark                       | 59 |

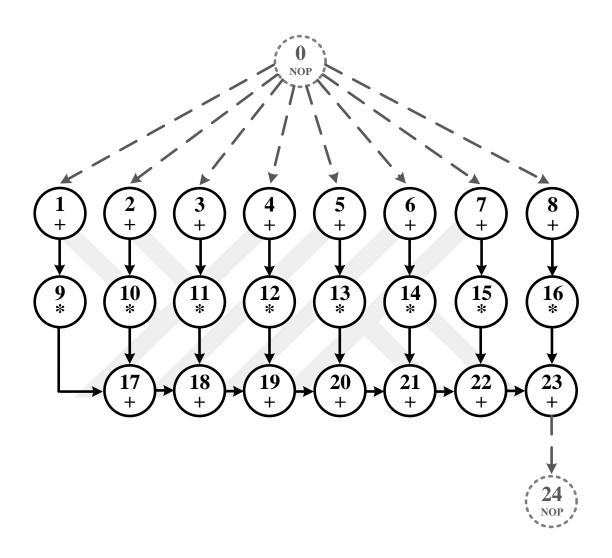

|    | B.2       | DAG of the Finite Impulse Response Filter Benchmark                     | 60 |

|    | B.3       | DAG of the Elliptic Wave Filter Benchmark                               |    |

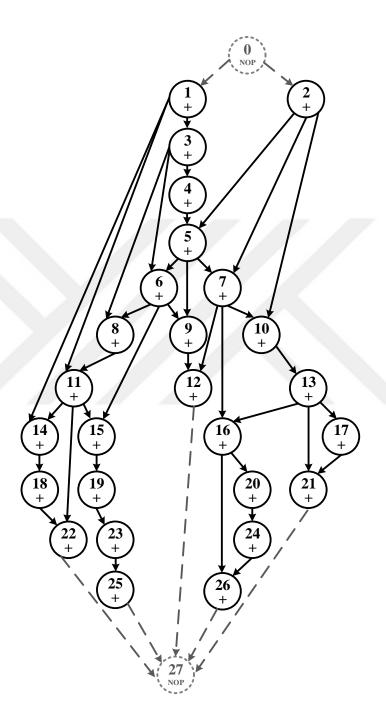

|    | B.4       | DAG of the Auto-Regressive Filter Benchmark                             |    |

|    | APPENI    | OIX C - Additional Experimental Results                                 | 63 |

|    | C.1       | Additional Experimental Results for Section 6.1                         | 63 |

|    | C.2       | Additional Experimental Results for Section 6.2                         | 68 |

|    | C.3       | Additional Experimental Results for Section 6.4.                        | 70 |

# **TABLES**

|           | $\underline{\mathbf{P}}$                                                | age |

|-----------|-------------------------------------------------------------------------|-----|

| Table 3.1 | A summary of related ILP-based HLS studies                              | 21  |

| Table 3.2 | A summary of related SA-based HLS studies                               | 28  |

| Table 4.1 | Resource library used in this study                                     | 38  |

| Table 5.1 | ILP notations                                                           | 43  |

| Table 5.2 | Notations used in SA-based HLS method equations                         | 50  |

| Table 6.1 | Benchmark specifications: the number of nodes, edges and, types of      |     |

|           | operations in their respective dataflow graphs.                         | 71  |

| Table 6.2 | Comparison of the reliability results of ILP and GA duplication         |     |

|           | methods for all benchmarks when $\alpha=1.0$                            | 74  |

| Table 6.3 | Average percentage change in the energy results of ILP-based models     |     |

|           | compared to GA duplication method for all benchmarks when $\alpha=1.0.$ | 75  |

| Table 6.4 | Comparison of the energy results of ILP and GA duplication methods      |     |

|           | for all benchmarks when $\alpha=0.0$                                    | 76  |

| Table 6.5 | Average change in the reliability results of ILP-based models           |     |

|           | compared to GA duplication method for all benchmarks with $\alpha=0.0.$ | 77  |

| Table 6.6 | Comparison of the reliability and energy results of ILP and GA-based    |     |

|           | partial duplication methods for all benchmarks with $\alpha=0.5$        | 78  |

| Table 6.7 | Comparison of the reliability and energy results of ILP full            |     |

|           | duplication method with GA-based partial duplication method for all     |     |

|           | benchmarks with $\alpha=0.5.$                                           | 78  |

| Table 6.8 | Comparison of the reliability results of SA-based method with ILP       |     |

|           | and GA-based methods for all benchmarks when $\alpha=1.0.$              | 81  |

| Table 6.9 | Average percentage change in the energy results of SA-based method      |     |

|           | compared to ILP and GA-based methods for all benchmarks when            |     |

|           | $\alpha = 1.0$                                                          | 82  |

| Table 6 | 5.10 | Comparison of the energy results of SA-based method with ILP and       |

|---------|------|------------------------------------------------------------------------|

|         |      | GA-based methods for all benchmarks when $\alpha = 0.0.$ 83            |

| Table 6 | 5.11 | Average percentage change in the reliability results of SA-based       |

|         |      | method compared to ILP and GA-based methods for all benchmarks         |

|         |      | when $\alpha = 0.0$ . 84                                               |

| Table 6 | 5.12 | Comparison of the reliability and energy results of SA-based method    |

|         |      | with ILP and GA-based methods for all benchmarks when $\alpha=0.5.$ 85 |

| Table 6 | 5.13 | Comparison of the reliability results of SA-based partial DMR          |

|         |      | method with the corresponding ILP and GA-based methods for all         |

|         |      | benchmarks when $\alpha=1.0.$ 88                                       |

| Table 6 | 5.14 | Comparison of the energy results of SA-based partial DMR               |

|         |      | method with the corresponding ILP and GA-based methods for all         |

|         |      | benchmarks when $\alpha=0.0.$ 90                                       |

| Table 6 | 5.15 | Comparison of the reliability and energy results of SA-based partial   |

|         |      | DMR method with the corresponding ILP and GA-based methods for         |

|         |      | all benchmarks when $\alpha = 0.5$ 91                                  |

| Table 6 | 5.16 | DES benchmark reliability and energy results of full DMR solutions     |

|         |      | for a different number of supply voltages                              |

| Table 6 | 5.17 | FIR benchmark reliability and energy results of full DMR solutions     |

|         |      | for a different number of supply voltages                              |

| Table C | C.1  | Comparison of the energy results of ILP and GA duplication methods     |

|         |      | for all benchmarks when $\alpha=1.0.$                                  |

| Table C | C.2  | Comparison of the reliability results of ILP and GA duplication        |

|         |      | methods for all benchmarks when $\alpha=0.0$ 164                       |

| Table C | C.3  | Comparison of the energy results of SA-based method with ILP and       |

|         |      | GA-based methods for all benchmarks when $\alpha=1.0$ 168              |

| Table C | C.4  | Comparison of the reliability results of SA-based method with ILP      |

|         |      | and GA-based methods for all benchmarks when $\alpha=0.0.\dots$ 169    |

| Table C | C.5  | EWF benchmark reliability and energy results of full DMR solutions     |

|         |      | for a different number of supply voltages                              |

| Table C.6 | AR benchmark reliability and energy results of full DMR solutions |     |

|-----------|-------------------------------------------------------------------|-----|

|           | for a different number of supply voltages                         | 171 |

# **FIGURES**

|            | <u>I</u>                                                                  | Page |

|------------|---------------------------------------------------------------------------|------|

| Figure 2.1 | Occurrence of a soft error in an n-type CMOS transistor                   | 15   |

| Figure 2.2 | An n-modular redundancy illustration for a fault tolerant component       | 16   |

| Figure 3.1 | ILP-based studies for HLS: times cited and publications over time         |      |

|            | on Web of Science.                                                        | 22   |

| Figure 3.2 | ILP-based studies for HLS: literature record count percentages based      |      |

|            | on Web of Science categories.                                             | 22   |

| Figure 3.3 | SA-based studies for HLS: times cited and publications over time on       |      |

|            | Web of Science.                                                           | 28   |

| Figure 3.4 | SA-based studies for HLS: literature record count percentages based       |      |

|            | on Web of Science categories.                                             | 29   |

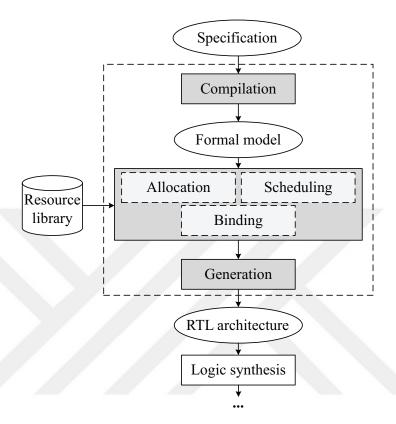

| Figure 4.1 | HLS design steps.                                                         | 34   |

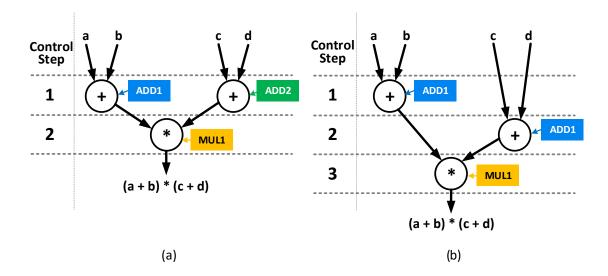

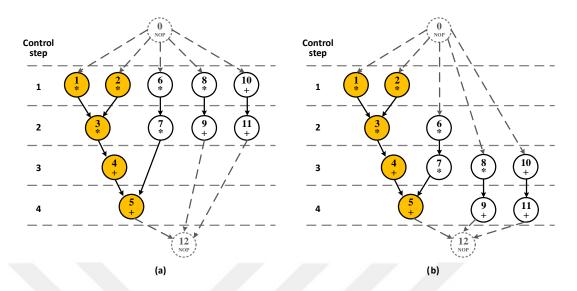

| Figure 4.2 | (a) A faster schedule with larger area, (b) A slower schedule with        |      |

|            | smaller area.                                                             | 35   |

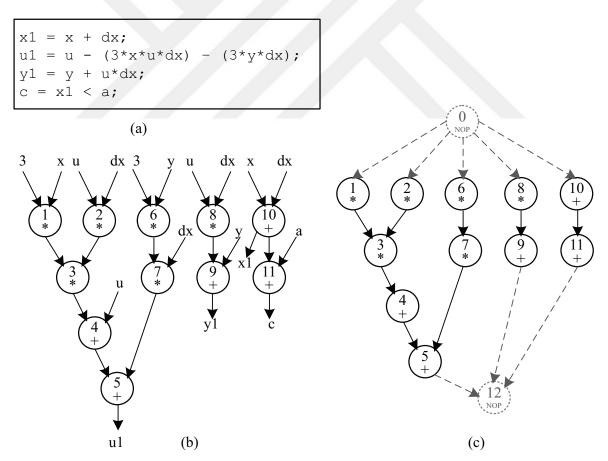

| Figure 4.3 | (a) An example design specification for differential equation             |      |

|            | solver, (b) Data-flow representation with dependencies (precedence        |      |

|            | constraints), and (c) DAG of the design specification                     | 37   |

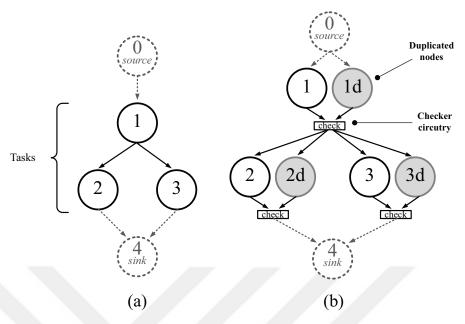

| Figure 4.4 | (a) An example task graph, (b) its fully duplicated version               | 40   |

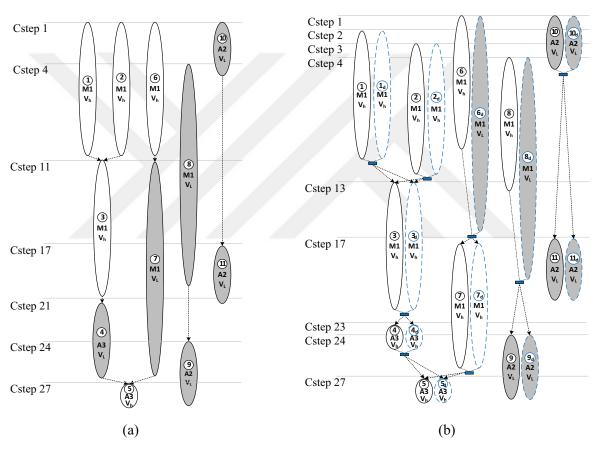

| Figure 4.5 | (a) HLS result without duplication, (b) HLS result with full DMR          |      |

|            | under the specified constraints                                           | 41   |

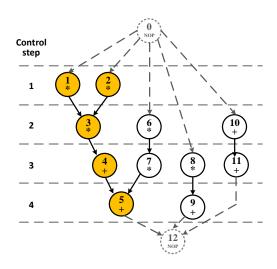

| Figure 5.1 | (a) ASAP schedule of DES, (b) ALAP schedule of DES                        | 53   |

| Figure 5.2 | An alternative schedule of DES with smaller area                          | 54   |

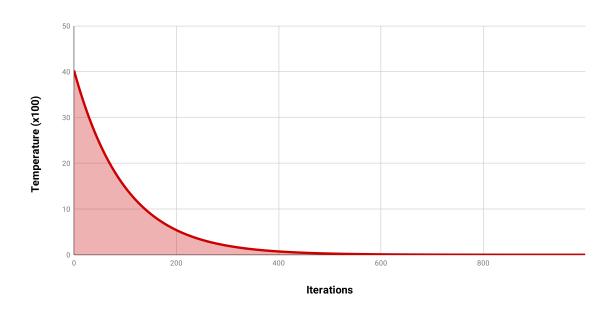

| Figure 5.3 | Temperature cooling rate for $\alpha_c = 0.99$                            | 67   |

| Figure 6.1 | Changes in reliability over different $\alpha$ values for DES benchmark   |      |

|            | (A = 30, L = 28) under different numbers of supply voltages               | 95   |

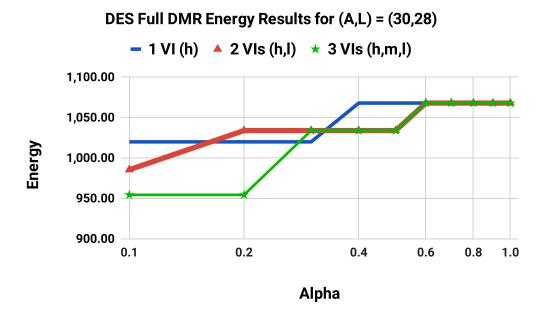

| Figure 6.2 | Changes in energy over different $\alpha$ values for DES benchmark ( $A=$ |      |

|            | 30, L = 28) under different numbers of supply voltages                    | 95   |

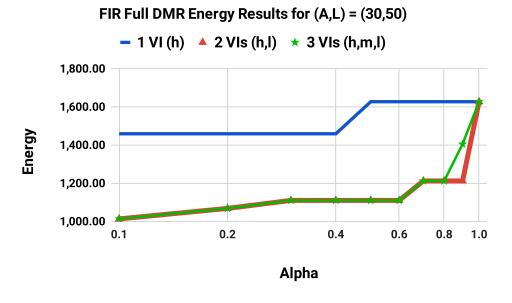

| Figure 6.3 | Changes in reliability over different $\alpha$ values for FIR benchmark   |

|------------|---------------------------------------------------------------------------|

|            | (A=30, L=50) under different numbers of supply voltages 96                |

| Figure 6.4 | Changes in energy over different $\alpha$ values for FIR benchmark ( $A=$ |

|            | 30, L = 50) under different numbers of supply voltages                    |

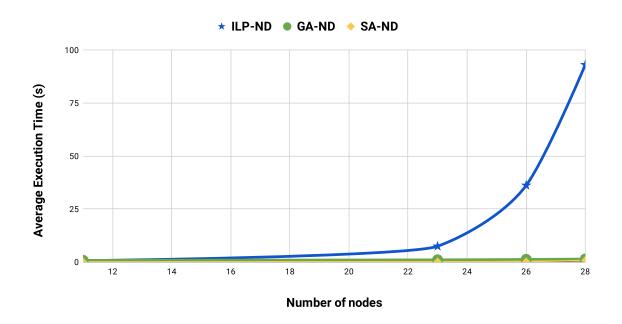

| Figure 6.5 | Average execution times of ILP, GA, and SA-based HLS methods              |

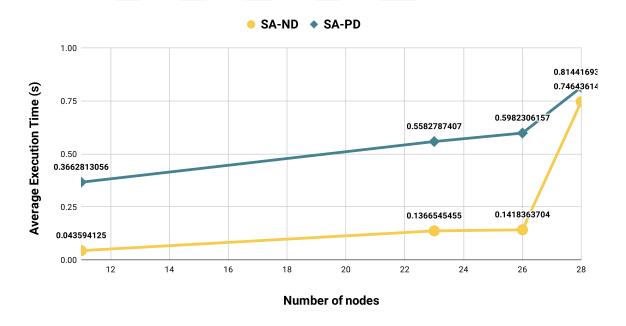

|            | without duplication for varying number of benchmark nodes 98              |

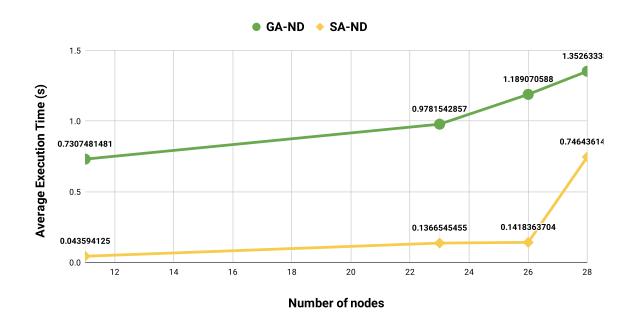

| Figure 6.6 | Average execution times of GA and SA-based HLS methods without            |

|            | duplication for varying number of benchmark nodes                         |

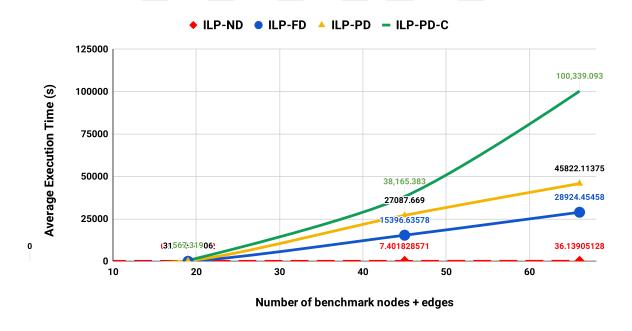

| Figure 6.7 | Average execution times of ILP models for varying number of               |

|            | benchmark nodes and edges                                                 |

| Figure 6.8 | Average execution times of the SA-ND and SA-PD methods for                |

|            | varying number of benchmark nodes                                         |

| Figure B.1 | DAG representation of the DES design specification                        |

| Figure B.2 | DAG representation of the FIR design specification                        |

| Figure B.3 | DAG representation of the EWF design specification                        |

| Figure B.4 | DAG representation of the AR design specification                         |

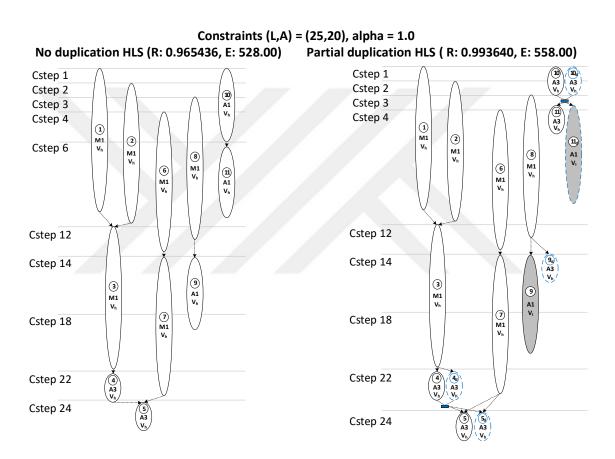

| Figure C.1 | Solutions without and with partial DMR obtained from the ILP              |

|            | models for the DES benchmark when $\alpha=1.0$ under the constraints      |

|            | A = 20, L = 25 165                                                        |

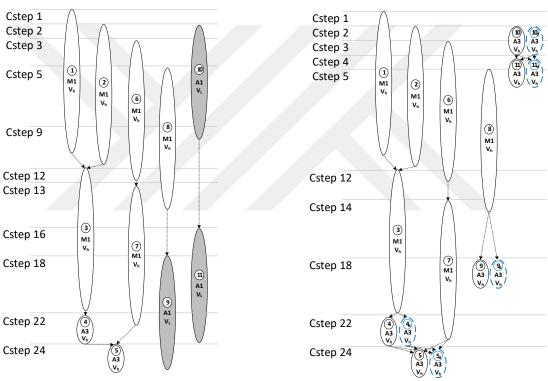

| Figure C.2 | Solutions without and with partial DMR obtained from the ILP              |

|            | models for the DES benchmark when $\alpha=0.5$ under the constraints      |

|            | A = 20, L = 25 166                                                        |

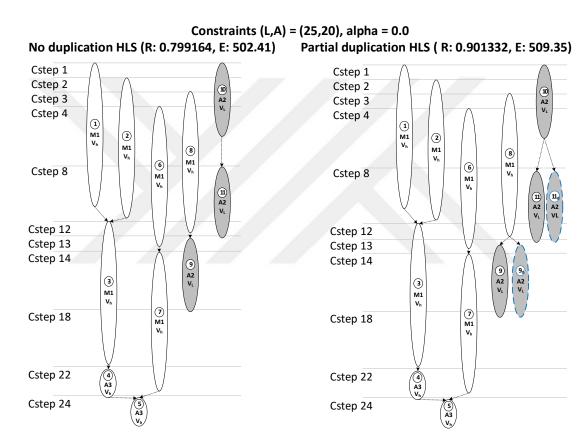

| Figure C.3 | Solutions without and with partial DMR obtained from the ILP              |

|            | models for the DES benchmark when $\alpha=0.0$ under the constraints      |

|            | A = 20, L = 25 167                                                        |

| Figure C.1 | Changes in reliability over different $\alpha$ values for EWF benchmark   |

|            | (A = 30, L = 40) under different numbers of supply voltages 172           |

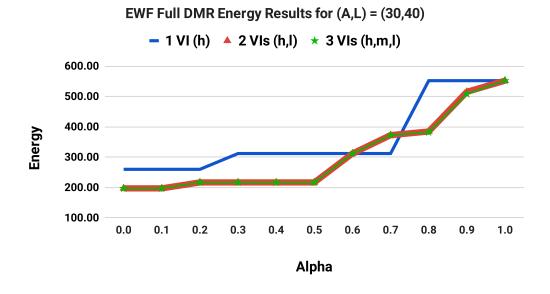

| Figure C.2 | Changes in energy over different $\alpha$ values for EWF benchmark ( $A=$ |

|            | 30, L = 40) under different numbers of supply voltages                    |

| Figure C.3 | Changes in reliability over different $\alpha$ values for AR benchmark   |

|------------|--------------------------------------------------------------------------|

|            | (A = 30, L = 50) under different numbers of supply voltages              |

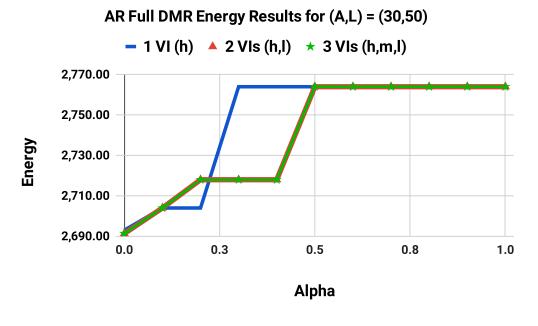

| Figure C.4 | Changes in energy over different $\alpha$ values for AR benchmark ( $A=$ |

|            | 30, L = 50) under different numbers of supply voltages                   |

#### **ABBREVIATIONS**

ACO : Ant-Colony Optimization

ADRS : Average Distance to Reference Set

**AR** : Auto-Regressive Filter

**ASAP** : As Soon As Possible

ASIC : Application-Specific Integrated Circuit

**CAD** : Computer Aided Design

**CMOS**: Complementary Metal-Oxide Semiconductor

**CPU**: Central Processing Unit

DAG : Directed Acyclic Graph

**DES**: Differential Equation Solver

**DMR** : **D**ual Modular **R**edundancy

**DSE** : **D**esign **S**pace **E**xploration

**DSP**: Digital Signal Processing

**DVS** : **D**ynamic **V**oltage **S**caling

**EWF** : Elliptic Wave Filter

FCCM: FPGA Custom Computing Machine

FIR : Finite Impulse Response Filter

FPGA : Field Programmable Gate Array

FU : Functional Unit

GA: Genetic Algorithm

**HDL** : Hardware Description Language

**HLS**: **H**igh-**L**evel **S**ynthesis

**HW** : **H**ardware

IC : Integrated Circuit

ILP : Integer Linear Programming

MHSP : Meta-Heuristic Specific Parameters

MILP : Mixed-Integer Linear Programming

ML: Machine Learning

MOOP : Multi-Objective Optimization Problem

MTBF : Mean Time Between Failures

MUX : Multiplexer

nm : Nanometer

**NOP** : No Operations

NP : Nondeterministic Polynomial

RTL : Register-Transfer Level

SA : Simulated Annealing

SE : Soft Error

**SER** : **S**oft **E**rror **R**ate

SRAM : Static Random Access Memory

SSA : Spurious Switching Activity

SW : Software

TMR : Triple Modular Redundancy

VI : Voltage Island

VLSI : Very Large Scale Integration

WCET: Worst-Case Execution Time

#### 1. INTRODUCTION

Continuous decrease in the transistor technology sizes due to ever-increasing demands for higher performance of computer applications has facilitated packing a considerably higher number of electronic components on chips. While 7-nm and 5-nm technology sizes are the current industry standard, the shift towards 3-nm technology has already been set into motion [1, 2]. The resulting increase in circuit densities has caused a decrease in the integrated circuit costs and area. However, at the same time, it has brought about new challenges in the process of integrated circuit design, such as higher vulnerability to transient (soft) errors due to radiation effects and lower supply and threshold voltage levels [3]. This increase in soft error rates (SER) is particularly evident in combinational circuits, which necessitates novel reliability-oriented design methods. There are certain error detection techniques for combinational circuits and memory elements; however, they usually increase the circuit area and cost (e.g., redundancy-based error detection and error correction codes). Furthermore, energy-aware designs face yet another negative effect on their reliability caused by energy reduction methods such as dynamic voltage scaling (DVS) or voltage islands (VIs) because a decrease in the supply voltage also decreases a circuit's reliability [4, 5]. Modular redundancy, i.e., replication of the system components, can improve the reliability of a system, but at the cost of increasing the resulting area and energy consumption.

Several parameters and system requirements may need to be considered during hardware design, such as area, performance, energy consumption and reliability. High-level synthesis (HLS) has multiple advantages compared to traditional register-transfer level (RTL)-based hardware design, including raising the abstraction level, accelerated verification, faster design space exploration, portability to new platforms, and accessibility to software engineers [6]. A major benefit of HLS is enabling the exploration of unique trade-offs for the generation of diverse microarchitectures that stem from the same behavioral specification but are obtained through different synthesis options, also called knobs [7, 8]. During the high-level synthesis (HLS) step of the application-specific integrated circuit (ASIC) design, it is possible to consider multiple system constraints (e.g., area and latency) and

optimization parameters (e.g., reliability and energy consumption) at a higher level of abstraction, and unify them to alleviate the burdensome design process that must consider all system requirements and constraints simultaneously. Automation tools that would facilitate the design process are particularly crucial in the design of integrated circuits with a large number of components.

In HLS design space exploration, several design parameters often opposing each other are considered for optimization (e.g., minimizing energy consumption negatively affects reliability). Thus, we can categorize it as a multi-objective optimization problem (MOOP) in which the goal is to look for a set of solution designs that are Pareto-optimal, meaning that any improvement in one of the parameters would cause a deterioration in another. Having several Pareto-optimal designs allows designers to choose the ones that fit best to the project's requirements by controlling the HLS synthesis process through synthesis options settings. The major issue with this is that the number of synthesis options superlinearly affects the growth of the search space [8]. Therefore, optimization methods for efficiently searching the space need to be proposed.

## 1.1. Scope of the Thesis

Traditional HLS methods usually consider only area and latency along with either energy or reliability. It is evident that there is a need for new systematic design methods that will consider all these requirements on a higher level of abstraction. This research has explored novel HLS optimization methods that can integrate all system requirements on a higher level of abstraction and relieve integrated circuit designers from lower-level design burdens.

Furthermore, there has been an exponential growth in the complexity of very-large-scale integration (VLSI) systems, which poses a great productivity bottleneck for the processes of design and verification in RTL as the prevalent method that has been used for decades to characterize VLSI systems. The reason is that RTL tools have not improved in proportion to the increase in VLSI system complexity. HLS contributes greatly to the hardware design process with many benefits it provides over the traditional RTL-based approach, as discussed

above. Nevertheless, there is still a non-trivial productivity gap between these two design flows, which is an important current issue in hardware design. Modern HLS tools still trail behind the RTL design flows in terms of results' quality, and should this productivity and quality gap close, HLS would become the new standard approach for hardware design [9]. Hence, another goal of this research was to propose novel HLS optimization methods that will contribute to closing that gap.

To the best of our knowledge, no prior research has proposed an optimization method that considers both area and latency as constraints while considering energy consumption and reliability as multi-objective optimization parameters. Moreover, the previous studies have neglected to thoroughly investigate the effect of multiple supply voltage levels on reliability and energy efficiency.

#### 1.2. Contributions

In this research, we address the mentioned deficiencies and propose novel and efficient ILP and SA-based HLS methods that also employ dual modular redundancy (DMR) for ASIC design with the objectives of minimizing energy consumption and maximizing reliability under the given area and latency constraints. In our study, we use different versions of the same resources in terms of varying area, performance, energy, and reliability characteristics, depending on the supply voltages at which they operate. Since we have two parameters in our optimization function, we blend the energy and reliability values by assigning weights to each of them to handle our multi-optimization problem. For the mapping and scheduling steps of the HLS, we use the ILP and SA-based optimization methods. The main contributions of this research can be summarized as follows:

We propose bi-objective ILP-based HLS methods that employ dual modular redundancy for increasing reliability in ASIC design, with the objectives of minimizing energy consumption and maximizing reliability under the given area and latency constraints.

- We formulate the mapping and scheduling steps of our duplication-based HLS design flow with two ILP-based methods (partial and full duplication) that obtain the optimum results in short times for smaller-scale benchmark applications due to their computational complexity. ILP-based methods are unsuitable for problems with many variables due to their undesirable CPU times. Nevertheless, they are important as they provide optimal results that can be used for testing other heuristic or metaheuristic methods designed to solve the same problems for larger-scale applications within more acceptable running times.

- We present an extended resource library with the varying area, delay, energy, and reliability parameters based on multiple supply voltage levels. We believe our resource library will also benefit future studies in HLS.

- We test and discuss the effects of utilizing voltage islands (VIs) on reliability and energy consumption in circuit design that employs modular redundancy.

- We illustrate the effectiveness of our ILP duplication models over the genetic algorithm (GA)-based selective duplication method in terms of energy and reliability results on several benchmarks by conducting a thorough experimental analysis.

- We also propose SA-based metaheuristic methods that tackle the same HLS problem

and obtain optimal or near-optimal solutions in acceptable polynomial time, as

opposed to the ILP-based methods whose running times increase exponentially as the

application size increases.

- By conducting a thorough experimental analysis, we demonstrate the effectiveness of our SA-based methods compared to the ILP-based models and their superiority over the genetic algorithm (GA)-based methods in terms of energy and reliability results on several benchmarks.

## 1.3. Organization

The organization of the thesis is as follows:

- Chapter 1 presents our motivation, contributions and the scope of the thesis.

- Chapter 2 provides background information on relevant topics, including optimization, high-level synthesis, soft errors, and the effects of modular hardware redundancy and multi-supply voltages on integrated circuits' reliability, latency, and energy consumption.

- Chapter 3 presents an overview, classification, and a comparative summary of the relevant related work.

- Chapter 4 gives a detailed problem definition.

- Chapter 5 introduces the proposed HLS optimization methodologies. First, we present the ILP-based mathematical optimization models. Then, we explain our metaheuristic SA-based methods.

- Chapter 6 demonstrates the effectiveness of the proposed methods by presenting and discussing the experimental results.

- Chapter 7 concludes this study with a summary of the thesis and possible future directions.

### 2. BACKGROUND OVERVIEW

In this section, we discuss some fundamental concepts about optimization, reliability, latency, and energy-related topics and issues in digital electronic systems, which are relevant to this research.

### 2.1. Optimization Fundamentals

The conventional engineering design process is generally an exhausting endeavor of iterations between the conceptual, preliminary, and detailed design steps that are usually also iterative processes within themselves, before reaching a desirable final design that meets all initial design requirements and specifications. Optimization has emerged as an alternative mechanism that can speed up the design cycle and generate better results while lowering the total design cost. Optimization entails finding the best solution from a set of possible alternative solutions for an optimization problem, which can be obtained via changing the controllable variables that define the problem based on some criteria, while usually subject to certain constraints [10, Chapter 1]. Optimization generally implies minimizing or maximizing a cost function or a set of functions, also known as the objective functions, which depends on selecting the appropriate input values for the function variables. Optimization goals may involve anything from maximizing metrics such as efficiency, profit, reliability, or performance, to minimizing metrics such as cost, delay, or energy consumption.

Optimization problems may be either linear or nonlinear depending on whether all constraints and objective functions can be formulated using linear functions or not. If a linear formulation of the constraints and objective functions is impossible, it leads to a much more complex nonconvex decision space. For nonlinear problems whose search space usually contains multiple locally optimal solutions, the main challenge is how to apply an approach that will avoid getting trapped in local minima or maxima while performing the search. Getting trapped in local minima or maxima would impede finding the globally optimum solution [11].

The optimization process necessitates that designers formulate a mathematical model of the problem at hand, which correctly describes the problem, defines the decision variables and the optimization objective, and specifies the constraints if any. Martins and Ning (2021) and Yang (2014) presented a general mathematical formulation that can be used as a common definition for a majority of continuous optimization problems [10, 12]. Let  $\vec{x}$  be a design vector defined in (1), where  $x_i$  elements represent d decision variables of a problem.

$$\vec{x} = (x_1, x_2, ..., x_d) \tag{1}$$

Let  $f_i(\vec{x})$ ,  $h_j(\vec{x})$ , and  $g_k(\vec{x})$  be functions of the design vector  $\vec{x}$ , and  $\mathcal{R}^d$  the search space within the scope of the decision variables. Then, an optimization problem can be defined as formulated in (2), where  $f_i(\vec{x})$  represents M objective functions, while  $h_j(\vec{x})$  and  $g_k(\vec{x})$  represent J and K equality and inequality constraint functions, respectively.

The formulation given in (2) defines a minimization problem. However, this formulation can also be used to define a maximization problem, given that it can easily be transformed into a minimization problem as given in (3). Furthermore, the inequality constraints can also be defined using  $\geq 0$  inequality if needed.

$$\max[f(x)] = -\min[-f(x)] \tag{3}$$

Nevertheless, an inequality constraint should never be expressed as a strict inequality since, in that case, the solution would not be properly mathematically defined as it would be

allowed to choose among solutions arbitrarily close to the equality. This consideration is particularly important for optimization attempts using computers as they use finite-precision arithmetic. Additionally, Martins and Ning (2021) argue that the optimization problem formulation should include as many independent decision variables as possible, although it may be desirable to begin with a smaller set that can later be broadened [10, Chapter 1].

Some problems may aim to optimize a single variable; hence, they have a single objective function. However, many problems in real life involve optimizing multiple metrics. Such problems are called multi-objective optimization problems (MOOPs). MOOPs frequently do not have an optimal solution that optimizes all of the objectives simultaneously, especially since some of those objectives may oppose each other and require designers to make trade-offs in search of an optimal solution based on the requirements. Such is the case with the problem of reliability and energy-oriented HLS addressed in this research. More reliable resources mostly require more power, while energy reduction techniques negatively affect the reliability of circuits. Therefore, when searching for the best solutions to MOOPs, designers need to make compromises that will produce Pareto-optimal results in the context of a conflicting multi-objective nature of the problem. A Pareto-optimal design is an efficient solution with the optimal objective function (no other feasible solution dominates it) such that the achieved trade-off between all objectives is optimal. *I.e.*, improving any objective function would come at the cost of worsening at least one other objective [13].

This compromise among different and often competing objectives may be achieved by reformulating the objective function for the given problem. One of the most commonly applied approaches is the weighted scalarization method which allows designers to assign a preference value to each objective function. The goal of weighted scalarization is to formulate a single scalar-valued objective function (i.e., a utility function)  $\mathcal{F}$  that incorporates all of the objectives simultaneously [14]. In Equation (4), the weighted scalarization of M objective functions  $f_i$  is formulated, where weights are assigned to each objective function through coefficients  $w_i$ .

$$\mathcal{F}(f_1(\vec{x}), f_2(\vec{x}), ..., f_M(\vec{x})) = \sum_{i=1}^{M} w_i \cdot f_i(\vec{x})$$

(4)

### 2.2. Optimization Algorithms

There exist many optimization algorithms that can be categorized based on several characteristics, including stochasticity (random or deterministic), time dependence (static or dynamic), order (zeroth, first, second), type of search performed (local or global), how the objective function is evaluated (directly or via a surrogate model), or depending on the algorithm nature (mathematical or heuristic) [10, Chapter 1]. Mathematical algorithms (e.g., linear programming) generate solutions based on the mathematical model of the problem, and they can provide optimal results. The major drawback is their inefficient complexity, especially for complex optimization problems and problems with many decision variables. Heuristic and metaheuristic algorithms (e.g., genetic algorithm, simulated annealing) are preferred in such scenarios as they can generate optimal or near-optimal (approximate but close enough) results in practical running times. However, they cannot guarantee the optimality of the solutions as they are not based on strict mathematical formulations.

None of the existing optimization algorithms is efficient for all optimization problems; hence, they should be chosen carefully based on the nature of the problem at hand. In this research, we have employed both mathematical and metaheuristic algorithms to optimize the problem at hand. The following sections briefly discuss the nature of the algorithms employed in this study and our reasoning for choosing them.

#### 2.2.1. Linear Programming

Linear programming is a subset of mathematical optimization and one of the most widely used approaches for the optimization of convex optimization problems that can be formulated using linear objective and constraint functions [10, Chapter 11]. It is a popular approach in

allocation problems optimization, which is one of the reasons it was our method of choice in this research because, in HLS, hardware resource allocation is one of the major tasks.

As the main focus of this research is the optimization of digital circuit design, our optimization problem consists of decision variables that fall under the integral domain and, more specifically, under the modular number system. Such problems can be modeled as integer linear programming problems, a subset of linear programming and the approach we adopted in this study. Scheduling and resource allocation are examples of discrete optimization problems. Optimization variables in discrete optimization can be binary, integer, and discrete, and all of them can be represented with integer values [10, Chapter 8].

One of the first approaches considered in linear programming optimization, and one of the most efficient ones in practice, is the simplex method, developed by George Dantzig in 1947, which operates by first discovering a simple, feasible solution such that all the constraints are met. Mathematically speaking, such a feasible solution is theoretically an extreme point on the edge of the feasible region, i.e., a convex polyhedron that spans the hyperspace  $\mathbb{R}^n$  bounded by n constraints expressed as linear functions. The simplex method then explores along the polyhedron edges in search of better objective function values to find the optimal solution. Nevertheless, the major drawback of this approach is its exponential worst-case complexity [15].

In this study, the primary approach used by the optimizer is a revised (primal) simplex method that is more computationally efficient than the original simplex method. This efficiency is achieved by constraining the simplex pivot operations to the inverse matrix only, hence, avoiding the execution of unnecessary tableau updates. As it is out of the scope of this study, we leave out the details of these methods. An interested reader can refer to [16] for detailed explanations of the inner workings of these methods. Another method employed by the optimizer used in this study, in addition to the simplex method, was the Newton Barrier method. Contrary to the simplex method, the Newton Barrier method searches through the interior region of the feasible region, looking for a close estimation of an optimal solution.

It usually takes a uniform number of iterations to complete, irrespective of the size of the optimization problem.

Discrete optimization is nondeterministic polynomial-time complete [10, Chapter 8], which means that there are no known efficient approaches that compute optimal solutions in polynomial time. ILP problems, in particular, are known to be polynomial-time hard [15]. We employed an ILP-based approach to obtain the optimal solutions for relatively small applications, which are then used for evaluating the performance of our heuristic methods that tackle the same optimization problem in practical running times.

#### 2.2.2. Metaheuristic Approaches for Discrete Optimization

A heuristic (from the Greek word 'heuriskō' for "I find, discover") is an algorithm in mathematical optimization which uses a trial and error approach to generate adequate (optimal or close enough) solutions for a complex optimization problem in acceptable running times, for which classical optimization methods cannot produce optimal results most often due to the huge computational complexity of those approaches. For some problems, the optimality and accuracy of the solution can be traded for speed if the goal is to obtain good enough (maybe even optimal but without any guarantees) solutions in reasonable running times. For such optimization problems, heuristic algorithms are a very efficient and sometimes the only practical alternative [12].

Metaheuristic algorithms emerged as more advanced heuristic approaches that can explore the search space more efficiently through higher-level considerations and trade-offs between local search versus randomization. These trade-offs enable metaheuristic approaches to break away from local search to a more global scale, and hence, to avoid getting stuck in local optima [12, 17]. Randomization is important as it enables more efficient exploration of the search space, specifically by either intensifying the search or diversifying it via random walks, while also using some deterministic process. Random walks guarantee that the candidate solutions generated along the way are diversified in their distribution over the search space on the global scale [18].

One of the popular metaheuristic optimization approaches developed for discrete optimization is a nature-inspired method called simulated annealing (SA). Simulated annealing was initially proposed in the early 80's as an optimization method analogous to the physical process of the annealing of solids. It was first proposed by Kirkpatrick et al. (1983) in [19], who coined the name and applied the approach to solving the traveling salesman problem, while Černý (1985) in [20] independently had the same idea of applying statistical thermodynamics principles to solving the same problem. These two works were pioneers in demonstrating how the analogy with statistical thermodynamics which states that large systems will spontaneously reach so-called state of equilibrium at a given temperature, can be applied as a generic method to solving large combinatorial optimization problems [21].

A strong feature of simulated annealing is its aptitude to avoid getting stuck in local optima as opposed to other deterministic approaches, as it can converge to the global optimum when its randomness and cooling schedule are properly arranged. The fundamental concept of SA is the use of random search as a Markov chain in such a way that better solutions are always accepted, while some candidate solutions that have a worse cost in terms of the objective function may still get accepted based on a transition probability [22].

The transition probability p is defined in Equation (5), in which  $\Delta f$  represents the change in the cost of the objective function  $f(x_j) - f(x_i)$  where  $x_i$  is the current best solution and  $x_j$  the candidate solution,  $k_B$  represents the Boltzmann constant, and T represents the current temperature that manages the annealing operation. The calculation of the transition probability can be adjusted (e.g., taking the Boltzmann constant to be 1). However, it must be in correlation with the annealing temperature and the objective function costs of the current and candidate solutions.

$$p = \exp\left(-\frac{\Delta f}{K_b T}\right) \tag{5}$$

In SA, a worse candidate will be kept if p > r, where r is a random real number selected from a uniform distribution in the range [0,1]. Temperature plays a crucial role in efficient search space exploration as the desired outcome is slowly decreasing the probability of a worse

solution getting accepted as the process cools down. A higher probability of accepting worse solutions at the beginning of the annealing process is desirable as it allows for more random exploration of the search space and guarantees that the algorithm will not get trapped in local optima. However, as the annealing process nears its end, this probability should become lower to enable intensified search for the optimum solution.

The most important concepts in SA-based optimization include (i) selection of good initial temperature, (ii) an efficient annealing (cooling) schedule that gradually decreases the temperature, (iii) a random neighboring design that ensures that all neighboring states (solutions) are not equally probable, and (iv) obtaining an acceptance probability contingent on a probability function that is positively correlated with the temperature. Pseudocode given in Alg. 1 shows the basic steps of the SA process. The decisions about the implementation details, such as selection of the starting state, initial temperature, neighbor states, and the appropriate cooling schedule, must be made for each specific problem.

#### Algorithm 1 A General Simulated Annealing Pseudocode

```

Inputs: s_0 starting state, T_0 initial temperature, numIterations.

Output: s the final optimal state.

s \leftarrow s_0

\triangleright Pick the starting state s_0 as the current solution s.

T \leftarrow T_0

> Start with the initial temperature.

for i = 1... numIterations do

Pick a neighboring candidate state s^*

if f(s^*) > f(s) then

s \leftarrow s^*

> Accept the better candidate.

else if P(f(s), f(s^*), T) \ge rand(0, 1) then

s \leftarrow s^*

▶ Accept the worse candidate anyway.

end if

T \leftarrow coolingSchedule(T)

▶ Reduce the temperature.

end for

return s

```

Several different methods for computing the initial temperature have been proposed in the literature [19, 21, 23–26], as well as several cooling (annealing) schedule approaches [19, 21, 27, 28]. Cooling rate selection should be performed carefully to match the problem complexity as a slower cooling rate will guarantee more optimal search space exploration [29]. Moreover, theoretical studies show that the number of iterations required to guarantee

that the obtained results are close enough to the optimum solutions is exponential based on the size of the problem; hence, starting and stopping criteria should be thoughtfully selected [27]. The starting conditions and cooling schedule adopted in this study are presented in detail in Section 5...

# 2.3. Reliability, Energy, and Latency Considerations for Optimization in Digital Electronic System Design

In this section, we discuss reliability, latency, and energy-related topics and issues in digital electronic systems design, which have been taken into consideration during this research. Since we employ VIs as an energy reduction technique in our study, we specifically focus on the effect of multi-supply voltages on each of these metrics.

#### 2.3.1. Soft Errors, Reliability, and Modular Redundancy

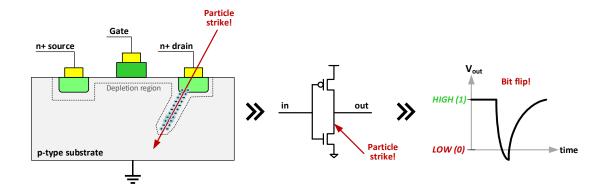

Transient or soft errors (SEs) in digital systems are non-persistent errors that do not cause permanent or fatal damage to a system. A system or a part of it will be affected only while the fault is present and its value is used. Thus, a digital system can resume its normal operation once it is restarted or when the erroneous value is rewritten. SEs can be caused by several external factors but mainly by radiation rays, either cosmic or resulting from the product packaging, which may cause a bit flip in semiconductor fabrics. Generally, the incident of SEs happens when the energy accumulated in a transistor surpasses its critical energy. Figure 2.1 illustrates the occurrence of a soft error in the silicon view and the transistor view for an n-type CMOS transistor.

The reliability of an electronic circuit is essentially the probability that the circuit will operate (perform the required function) correctly for a specified time interval. The failure rate, also known as soft error rate (SER), is the most commonly used metric for estimating the reliability of electronic circuits [30]. It is obtained using Equation (6), where MTBF

Figure 2.1 Occurrence of a soft error in an n-type CMOS transistor.

represents the mean time between failures (MTBF) which can be defined as the mean operating (up) time between recoverable failures in a circuit.

$$\lambda = \frac{1}{MTBF} \tag{6}$$

A high SER of a system has a negative effect on the system's reliability. The reliability of a system can be obtained using Equation (7), where  $\lambda$  represents the SER of the system, while t represents the operating time. From Equation (7), we can observe that the reliability of a system is inversely proportional to its SER: the higher the SER, the lower the reliability.

$$R(t) = e^{-\lambda t} \tag{7}$$

The resulting reliability of a circuit depends on the reliability, number, and placement of the individual elements in the circuit. Arrangement of the circuit elements can be in series, parallel, or a combination of both [31]. For example, when operations execute in series in a circuit, the overall reliability will be calculated as the product of all individual reliability values. Hence, the low reliability of one individual element will negatively affect the overall circuit reliability.

One of the popular techniques to increase a system's reliability is to use modular redundancy (i.e., duplicate components and make their backups). When a component is duplicated in parallel, its new boosted reliability value can be obtained through Equation (8), where  $R_c$  represents the total reliability of the component after duplication, while  $R_i$  and  $R_{i'}$  represent the individual reliability values of the original instance of the system component and its duplicated backup, respectively.

$$R_c = R_i + R_{i'} - R_i R_{i'} \tag{8}$$

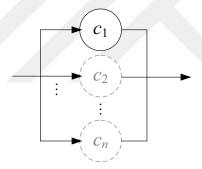

Dual and triple modular redundancy with checker circuits (e.g., a majority voting circuitry in TMR) are popular hardware redundancy approaches. Nonetheless, in general, a parallel n-modular redundancy solution for a fault-tolerant circuit can be used (see Figure 2.2) [32].

Figure 2.2 An n-modular redundancy illustration for a fault tolerant component.

The overall improved reliability of such a design can be obtained with Equation (9) where  $R_{c_i}$  represents the reliability of the  $i^{th}$  replica of the component c.

$$R_c = 1 - \prod_{i=1..n} (1 - R_{c_i}) \tag{9}$$

Several points should be considered when deciding which components to duplicate (full or partial duplication) and which resources to use for modular redundancy. In terms of complying with the area and latency constraints, a system with duplicated components should still meet the given area and latency requirements. Usually, backups are created using the

same circuit elements used for the original components. However, sometimes using different implementations of those circuit elements may result in a more optimal solution because the behavior against SEs manifests differently in varying implementations of the same circuit element (e.g., a slow circuit element may demonstrate higher reliability than a fast one) [33]. Finally, modular redundancy will inevitably add to the system's energy consumption, which is a crucial design consideration in energy-aware systems.

#### 2.3.2. Effects of Multi-Supply Voltages on Energy and Latency

While reliability and/or performance (application runtime or latency) are the first and foremost design considerations in safety-critical systems, efficient energy consumption is usually the main design consideration in battery-powered systems. Therefore, varying integrated systems may require different design trade-offs to achieve the desired system requirements. In this study, we employ one of the popular energy reduction approaches for digital systems; namely voltage islands [34]. In digital systems that use voltage islands, different parts of the circuit may operate under different supply voltages to lower the system's overall energy consumption.

Energy reduction techniques are beneficial because lowering the supply voltage does not affect the worst-case execution time (WCET) in the same proportion it affects the overall energy consumption of a system. A change in energy consumption is directly proportional to the square of the change in the supply voltage. This is formulated in Equation (10), where  $E_{v_h}$  and  $E_{v_l}$  are the energy consumption amounts of the circuit at a high and low voltage levels  $v_h$  and  $v_l$ , respectively.

$$E_{v_l} = E_{v_h} \left(\frac{v_l}{v_h}\right)^2 \tag{10}$$

On the other hand, a reduction in the supply voltage will only result in a proportional increase of the worst-case execution time (WCET) of a system. This is formulated in Equation (11),

where  $v_l$  is a threshold voltage, while  $t_{v_h}$  and  $t_{v_l}$  are the WCETs of a circuit at a high and low voltage levels, respectively.

$$t_{v_l} = t_{v_h} \left(\frac{v_l}{v_h}\right) \left(\frac{v_h - v_t}{v_l - v_t}\right)^2 \tag{11}$$

Therefore, having a part of a circuit whose operation at a lower voltage will not cause an unacceptable increase in the circuit's WCET, while coincidentally resulting in a notable decrease in the overall energy consumption of the circuit may be a desirable design objective.

### 2.3.3. Effects of Multi-Supply Voltages on Reliability

As discussed in the previous subsection, energy reduction techniques in general, and VIs in particular, may provide an efficient way to reduce energy consumption in a system without introducing too much extra latency. Nevertheless, another crucial consideration when using multi-supply voltages in a circuit is the effect of this approach on the circuit's reliability.

As already mentioned, SEs will inevitably occur when the energy accumulated in a transistor surpasses its critical energy. When a circuit operates under lower voltages, the critical energy can be much more easily exceeded. Hence, lowering the supply voltage will also negatively affect a system's reliability. This relation is formulated in Equation (12), where  $\lambda$  refers to the SER, d > 0 is a constant, and  $\lambda_0$  refers to the average error rate at frequency f [35].

$$\lambda(f) = \lambda_0 10^{\frac{d(1-f)}{(1-f_{min})}} \tag{12}$$

## 3. RELATED WORK

In this section, we categorize the related work based on four approaches employed in this research: (i) ILP-based HLS solutions; (ii) SA-based HLS solutions; (iii) HLS with modular redundancy for improved reliability; and (iv) HLS solutions that employ multi-supply voltages for energy-oriented designs.

### 3.1. ILP-Based HLS Studies

Several studies have employed ILP-based methods for tackling the HLS problem with different objectives, but mainly to increase reliability. In [36], the authors proposed a 0-1 ILP formulation for reliability-oriented HLS under the given area and latency constraints. This study did not consider energy awareness during the HLS process.

In [37], the authors focused on the aging of the functional units (FUs) to maximize the reliability and lifetime of both data-flow intensive and control-flow intensive designs. They proposed an ILP-based scheduling technique that employs task chaining and multicycling to mitigate aging traits of the FUs to achieve more than a double lifetime with an acceptable added latency overhead. This study considered control-flow intensive designs as well, as opposed to this study; however, energy considerations were completely neglected.

Another study that also focused on optimizing reliability is [38], in which authors proposed both an ILP formulation and a heuristic allocation and binding method for optimizing reliability in control-flow intensive systems under the area and latency constraints. Their methods are based on a prior vulnerability analysis of variables and tasks in the behavioral description, which was proved to enhance system reliability significantly compared to the vulnerability-unaware HLS. Although the proposed method achieves a significant improvement of up to 85% in terms of reliability without adding extra area overhead, the authors did not consider its effect on energy consumption.

The authors of [39] also studied scheduling in HLS, focusing on optimizing circuit datapath reliability under the latency and area constraints. They proposed an ILP formulation that considers tasks and their active times in scheduling for maximum reliability. However, energy considerations were again ignored in this study.

In [40], different objectives of minimizing the latency and area of the resulting integrated circuit are investigated. The authors did not focus on either reliability or energy consumption optimization; however, they proposed a novel multi-objective MILP model considering multiplexers along with FUs during the HLS design step. The experiments showed that the circuits which result from a design process that incorporates multiplexer usage considerations have more optimal latency and area values on average than the circuits when they are ignored.

Circuit area minimization was also studied in [41]. The authors proposed a novel ILP formulation and an ILP-based heuristic for the resource allocation and binding steps of HLS under the given latency constraint. They considered FUs, registers, and multiplexers for control and datapath circuits in their proposed methods. However, reliability and energy considerations were left out in this study. In [42], the authors presented an ILP model for HLS of DSP algorithms with the goal of area cost minimization under latency constraints. Energy and reliability considerations were again left out.

Another study that focused on latency minimization is [43]. The authors proposed a MILP-based approach to solving HLS with a built-in programmable duty cycle mechanism for designs that use dual-edge-triggered flip-flops as memory elements. Their approach was able to improve latency for several benchmarks. The proposed method, however, did not consider any area, reliability, or energy issues.

[44] also studied delay and performance yield optimization for scheduling and resource binding in HLS. The authors presented an ILP formulation that considers timing variations of different resources and employs successive tasks and resource chaining for improved latency and performance yield, which can be defined as the probability that the design can operate efficiently at a specific clock frequency. This method, however, also does not tackle reliability or energy considerations.

In [45], the authors proposed an ILP-based HLS approach for designs that use VIs with dual supply voltage to minimize energy consumption. Unlike this study, they do not consider the effect of energy reduction on reliability. Another study that employed multiple supply voltages approach for energy minimization is [46], in which the authors presented an ILP-based HLS method for optimizing energy but also neglected its effects on reliability.

Optimization of energy consumption was also tackled in [47]. The authors presented an ILP model for energy-aware HLS under the constraints of area and latency. Nevertheless, they also ignored the effect of energy savings on circuit reliability. Another study that focused on energy optimization under latency constraints is [48]. Similarly to our study, they used pipelined resources in their designs; however, reliability considerations were again disregarded.

In [49], the authors focused on both energy and task delay minimization under latency constraints. They proposed an ILP model that minimizes the total energy consumption through optimizing task scheduling. The reliability concerns were not discussed in the study.

In Table 3.1, we present a summary of the relevant related work that employed the ILP-based approaches to optimization in HLS. We note the optimization metrics considered, as well as design constraints, if any.

Table 3.1 A summary of related ILP-based HLS studies.

| Study      | <b>Optimization Metrics</b>   | Constraints       | Target Systems                                |

|------------|-------------------------------|-------------------|-----------------------------------------------|

| [36]       | Reliability                   | Area, latency     | ASIC                                          |

| [37]       | Reliability, circuit lifetime | Latency           | Data-flow and control-flow intensive circuits |

| [38]       | Reliability, area             | -                 | Data-flow and control-flow intensive circuits |

| [39]       | Reliability                   | Area, latency     | ASIC                                          |

| [40]       | Area, latency                 | -                 | ASIC                                          |

| [41]       | Area                          | Latency           | Data-flow and control-flow intensive circuits |

| [42]       | Area                          | Latency           | DSP algorithms with blocked schedules         |

| [43]       | Latency                       | -                 | Circuits with dual-edge-triggered flip-flops  |

| [44]       | Area, Latency                 | Performance yield | ASIC                                          |

| [45]       | Energy                        | -                 | Dual supply voltage circuits                  |

| [46]       | Energy                        | -                 | Multi-supply voltage ASIC                     |

| [47]       | Energy                        | Area, latency     | ASIC                                          |

| [48]       | Energy                        | Latency           | Pipelined ASIC                                |

| [49]       | Energy, task delay            | Latency           | ASIC                                          |

| This study | Reliability, energy           | Area, latency     | Pipelined multi-supply voltage ASIC           |

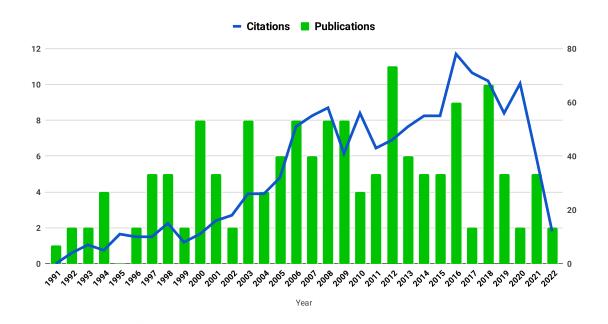

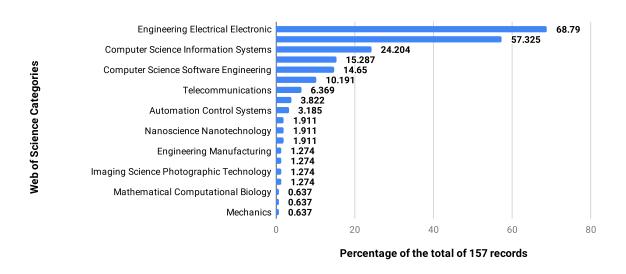

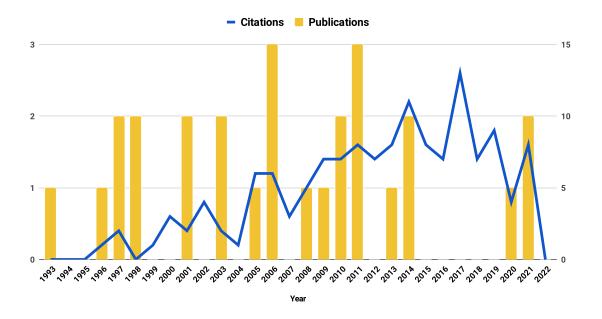

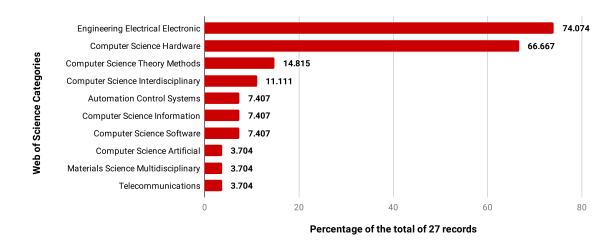

Figure 3.1 presents the citation and publication statistics on ILP-based HLS studies in the literature indexed on the Web of Science over the last three decades. Furthermore, Figure 3.2 shows the percentages of the total number of ILP-based HLS studies in the literature classified according to the Web of Science categories.

Figure 3.1 ILP-based studies for HLS: times cited and publications over time on Web of Science.

Figure 3.2 ILP-based studies for HLS: literature record count percentages based on Web of Science categories.

#### 3.2. SA-Based HLS Studies

Simulated annealing has been a popular metaheuristic method of choice for several HLS studies in the literature. In [50], an SA-based HLS algorithm for pipelined datapath synthesis was proposed. The algorithm optimizes the latency and resource cost and can also take those metrics as design constraints. In [51], the authors focused on optimizing the design area for the HLS process in FPGAs. Their SA-based method employs rescheduling and switching the tasks between resources to look for better solutions in terms of area. The experimental results showed that the proposed approach outperforms the conventional HLS flow in terms of optimizing the exploration of search space up to 37% and achieving more than 11% reduction in the overall design area. However, these studies did not focus on reliability or energy optimization, and no design constraints were considered in the proposed method in [51].

In [52], the authors focused on the area optimization problem in HLS of multiple word-length DSP algorithms on heterogeneous-resource FPGAs. They used different variations of resources, as we did in this study, to achieve area improvements of up to 60% compared to logic-based approaches. Their SA-based HLS method takes latency as a constraint while minimizing the area; however, no reliability or energy considerations are taken during the HLS process.

SALSA, a scheduling method in HLS for optimizing HW resource cost under the latency constraint, was proposed in [53]. It employs an SA-based approach for improving the initial schedule that satisfies the timing constraint by exploring alternative schedules to minimize resource cost. Again, the energy and reliability considerations were left out of the HLS process.

The authors in [54] focused on the area and latency optimization in performance yield-guaranteed HLS. They proposed an SA-based HLS algorithm with statistical static timing analysis. They employed a similar approach to their multi-objective problem in this study, namely the weighted scalarization method that is also employed in our

study. The experimental results showed an average area reduction of 14% under the 95% performance yield constraint. This method, however, also does not tackle reliability or energy considerations.

In [55], the authors presented a unified method for HW/SW codesign, incorporating an SA-based HLS approach for multi-FPGAs. Their objective was to minimize resource utilization under the latency constraint. This study did not include reliability or energy considerations in the proposed HLS method. Another study that employed an SA-based approach to HW/SW codesign and HLS for low-power embedded systems is [56]. The authors proposed an HLS method intending to minimize overall power consumption under the given latency constraint. The experiment results showed that the proposed method achieves more effective performance trade-offs than the task-level codesign. However, this study did not investigate the effect of the power savings on the final design reliability.

Apart from the area and latency considerations, testability of the final RTL designs was also considered as an objective in [57]. The authors proposed an enhanced SA-based algorithm for HLS of digital systems, which optimizes the area, latency, and testability metrics. The experimental results showed that the proposed enhanced SA-based algorithm achieves better than the conventional SA-based approach. Nevertheless, this study did not focus on the energy or reliability of the final designs.

In [58], the authors tackled the problem of HLS for digital systems targeted for high-density FPGAs with run-time reconfigurable HW resources with pipelined execution. They proposed an SA-based optimization algorithm that optimizes area and latency but disregards the reliability or energy considerations.