REAL TIME IMPLEMENTATION OF AN ACOUSTIC RADAR ON FIELD

PROGRAMMABLE GATE ARRAYS

A THESIS SUBMITTED TO

THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

OF

MIDDLE EAST TECHNICAL UNIVERSITY

BY

MURAT ARSLAN

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

ELECTRICAL AND ELECTRONICS ENGINEERING

DECEMBER 2012

Approval of the thesis:

**REAL TIME IMPLEMENTATION OF AN ACOUSTIC RADAR ON FIELD

PROGRAMMABLE GATE ARRAYS**

submitted by **MURAT ARSLAN** in partial fulfillment of the requirements for the degree of **Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University** by,

Prof. Dr. Canan Özgen \_\_\_\_\_

Dean, Graduate School of **Natural and Applied Sciences**

Prof. Dr. İsmet Erkmen \_\_\_\_\_

Head of Department, **Electrical and Electronics Engineering**

Prof. Dr. Temel Engin Tuncer \_\_\_\_\_

Supervisor, **Electrical and Electronics Engineering Department**

**Examining Committee Members:**

Prof. Dr. Temel Engin Tuncer \_\_\_\_\_

Electrical and Electronics Engineering Dept., METU

Prof. Dr. Buyurman Baykal \_\_\_\_\_

Electrical and Electronics Engineering Dept., METU

Prof. Dr. Gözde Akar \_\_\_\_\_

Electrical and Electronics Engineering Dept., METU

Assoc. Prof. Dr. Çağatay Candan \_\_\_\_\_

Electrical and Electronics Engineering Dept., METU

Dr. Güzin Kurnaz, PhD. \_\_\_\_\_

HBT SKTM, ASELSAN

**Date:** \_\_\_\_\_

**I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.**

Name, Last Name: MURAT ARSLAN

Signature :

## ABSTRACT

### REAL TIME IMPLEMENTATION OF AN ACOUSTIC RADAR ON FIELD PROGRAMMABLE GATE ARRAYS

Arslan, Murat

M.S., Department of Electrical and Electronics Engineering

Supervisor : Prof. Dr. Temel Engin Tuncer

December 2012, 133 pages

Radar is a system which uses electromagnetic waves to determine the range, direction and velocity of objects. In this thesis, an Acoustic Radar system is designed and implemented. Acoustic Radar uses sound waves to localize objects. While such a system has several limitations compared to its electromagnetic counterpart, the simplicity and low cost of its front-end makes it a good testbed for realizing the functions of a radar system. In this thesis, a six element transmit-receive array is constructed using loudspeakers and microphones. Six channel A/D and D/A converter boards are integrated with an FPGA unit where all the processing for transmit and receive functions are implemented. Signal processing is composed of filtering, beamforming, cross correlation and decision processes. The hardware platform is controlled by a computer through an ethernet connection. A user interface is provided where the radar functions can be controlled and changed. The tests for the acoustic radar are performed in an uncontrolled laboratory environment where there are several objects which generate multipaths. It is shown that the system works consistently and can localize objects accurately.

Keywords: acoustic radar, acoustic imaging, phased arrays, delay-and-sum beamformer

## ÖZ

### ALANDA PROGRAMLANABİLİR KAPI DİZİLERİİNDE GERÇEK ZAMANLI BİR AKUSTİK RADAR UYGULAMASI

Arslan, Murat

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü

Tez Yöneticisi : Prof. Dr. Temel Engin Tuncer

Aralık 2012, 133 sayfa

Radar; nesnelerin uzaklıklarını, yönlerini ve hızlarını belirlemek için elektromanyetik dalgalar kullanan bir sistemdir. Bu tez çalışmasında akustik bir radar sistemi tasarlanmış ve gerçeklenmiştir. Akustik Radar nesnelerin yerlerini belirlemek için ses dalgaları kullanır. Böyle bir sistem, elektromanyetik emsali ile karşılaştırıldığında birçok sınırlamaya sahip olmasına rağmen basit ve düşük maliyetli ön ucu onu radar fonksiyonlarının gerçeklenmesi için uygun bir sinama ortamı haline getirmektedir. Bu tez çalışmasında altı elemanlı bir alıcı-verici dizisi hoparlör ve mikrofonlar kullanılarak oluşturulmuştur. Altı kanallı A/D ve D/A çevirici devre kartları bütün gönderme ve alma işaret işleme fonksiyonlarının gerçekleştiği bir FPGA birimi ile entegre edilmiştir. İşaret işleme fonksiyonları süzme, hüzmeleme, çapraz korelasyon ve karar verme işlemlerinden oluşur. Donanım platformu bir bilgisayar tarafından ethernet bağlantısı aracılığıyla kontrol edilmektedir. Radar fonksiyonlarının kontrol edilebileceği ve değiştirilebileceği bir kullanıcı arayüzü sunulmaktadır. Akustik radar testleri çok-yolluluk etkileri yaratan birçok nesnenin yer aldığı kontrolsüz bir laboratuvar ortamında yürütülmüştür. Sistemin tutarlı bir biçimde çalıştığı ve nesnelerin yerlerini doğru olarak tespit edebildiği ispatlanmıştır.

Anahtar Kelimeler: akustik radar, akustik görüntüleme, fazlı diziler, geciktir-ve-topla hüzme şekillendirici

*To my family*

## ACKNOWLEDGMENTS

I would like to express my deepest gratitude to my supervisor Prof. Dr. Temel Engin Tuncer for his precious support, ideas and trust throughout my thesis work. Without his everlasting patience, excellent guidance, motivating attitude and practical approach to the problem, I could not complete this thesis work.

I would like to thank my colleague Soner Yeşil for his support, motivating discussions, precious ideas and suggestions on the implementation of the system. He has obvious effects on my fundamental decisions throughout the thesis study.

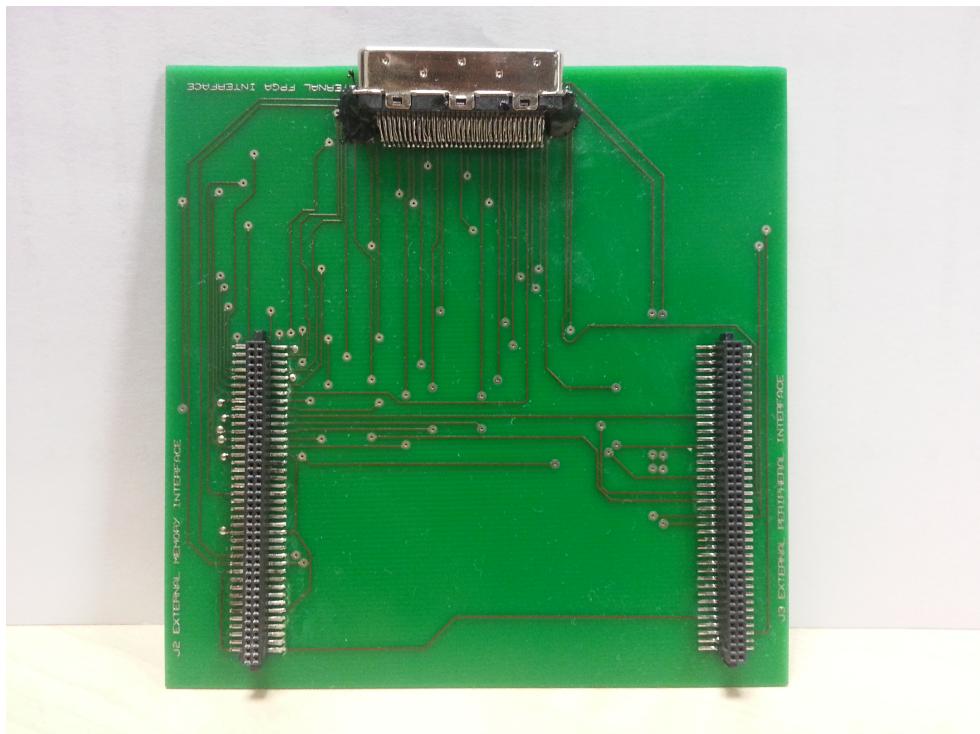

I would like to thank my colleague Barış Bölükbaşı for helping me in designing the PCB which connects two fundamental hardware units in the system and for always having time for my questions about hardware issues of the system.

I would like to thank Barış Tanyeri (accounts manager in Texas Instruments Inc., Turkey) and Texas Instruments Inc. for donating one of the main hardware units of the system, which is PCM1602 DAC Evaluation Module.

I would like to thank my colleague Ersin Karatop for taking time and helping me in cabling, soldering and other hardware modifications despite his heavy work load.

I would like to thank Aselsan Inc. for supporting my graduate study. I would like to thank my close friends Hakan Erkal, Önder Bilgiç and all the others whom I cannot state individually here for their motivating support.

I would like to thank the METU SAM (Sensor Array and Multichannel Signal Processing) Research Laboratory People Yılmaz Kalkan and Ahmet Musab Elbir for their good company and support.

Last but not the least; I would like to thank my family. Not only this thesis work, nothing would be possible without them.

## TABLE OF CONTENTS

|                                                                  |      |

|------------------------------------------------------------------|------|

| ABSTRACT . . . . .                                               | iv   |

| ÖZ . . . . .                                                     | v    |

| ACKNOWLEDGMENTS . . . . .                                        | viii |

| TABLE OF CONTENTS . . . . .                                      | ix   |

| LIST OF TABLES . . . . .                                         | xii  |

| LIST OF FIGURES . . . . .                                        | xiii |

| CHAPTERS                                                         |      |

| 1    INTRODUCTION . . . . .                                      | 1    |

| 2    BACKGROUND . . . . .                                        | 3    |

| 2.1    Array Signal Processing . . . . .                         | 3    |

| 2.1.1    Spatial Signals . . . . .                               | 4    |

| 2.1.2    Near and Far Field Concept . . . . .                    | 5    |

| 2.1.3    Array Model Representation . . . . .                    | 7    |

| 2.2    Array Beamforming . . . . .                               | 13   |

| 2.2.1    Delay and Sum Technique . . . . .                       | 14   |

| 2.2.2    Designing the Maximum SNR Spatial Filter [15] . . . . . | 19   |

| 3    ACOUSTIC RADAR . . . . .                                    | 22   |

| 3.1    System Structure . . . . .                                | 22   |

| 3.1.1    Radar System Controller . . . . .                       | 23   |

| 3.1.2    Transmitter . . . . .                                   | 24   |

| 3.1.3    Receiver . . . . .                                      | 25   |

| 3.1.4    System Configuration and Display Unit . . . . .         | 25   |

| 3.1.5    Memory Unit . . . . .                                   | 26   |

| 3.1.6    Transmit and Receive Arrays . . . . .                   | 27   |

|          |                                                      |    |

|----------|------------------------------------------------------|----|

| 3.1.7    | Acoustic Radar System Parameters . . . . .           | 27 |

| 3.1.7.1  | The Radar Equation . . . . .                         | 28 |

| 3.1.7.2  | Pulse Width . . . . .                                | 29 |

| 3.1.7.3  | Wavelength . . . . .                                 | 30 |

| 3.1.7.4  | Pulse Repetition Period . . . . .                    | 30 |

| 3.1.7.5  | Pulse Shape . . . . .                                | 31 |

| 4        | FPGA IMPLEMENTATION OF RADAR PROCESSING . . . . .    | 34 |

| 4.1      | Hardware Description . . . . .                       | 35 |

| 4.1.1    | DIGILENT ATLYS Spartan-6 FPGA Board . . . . .        | 35 |

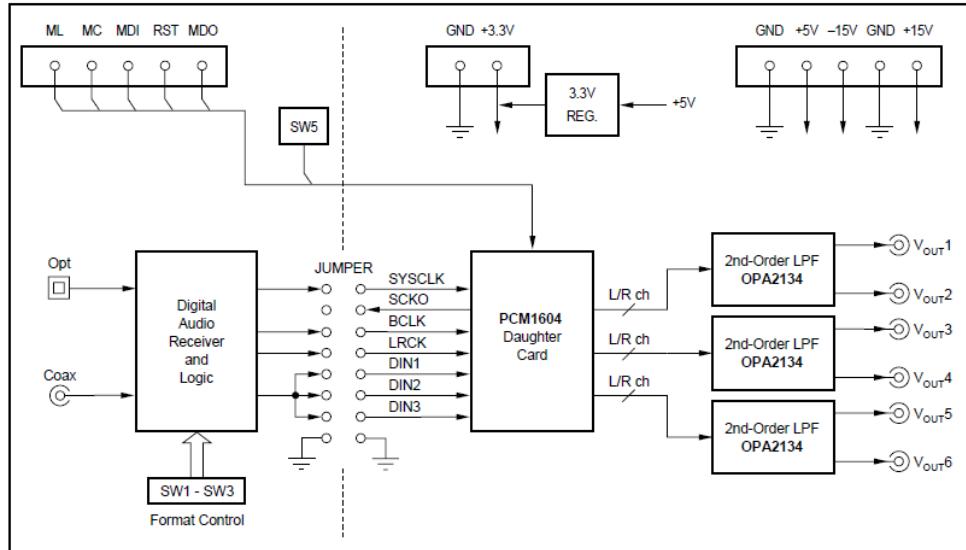

| 4.1.2    | TI PCM1602 DAC Evaluation Module . . . . .           | 37 |

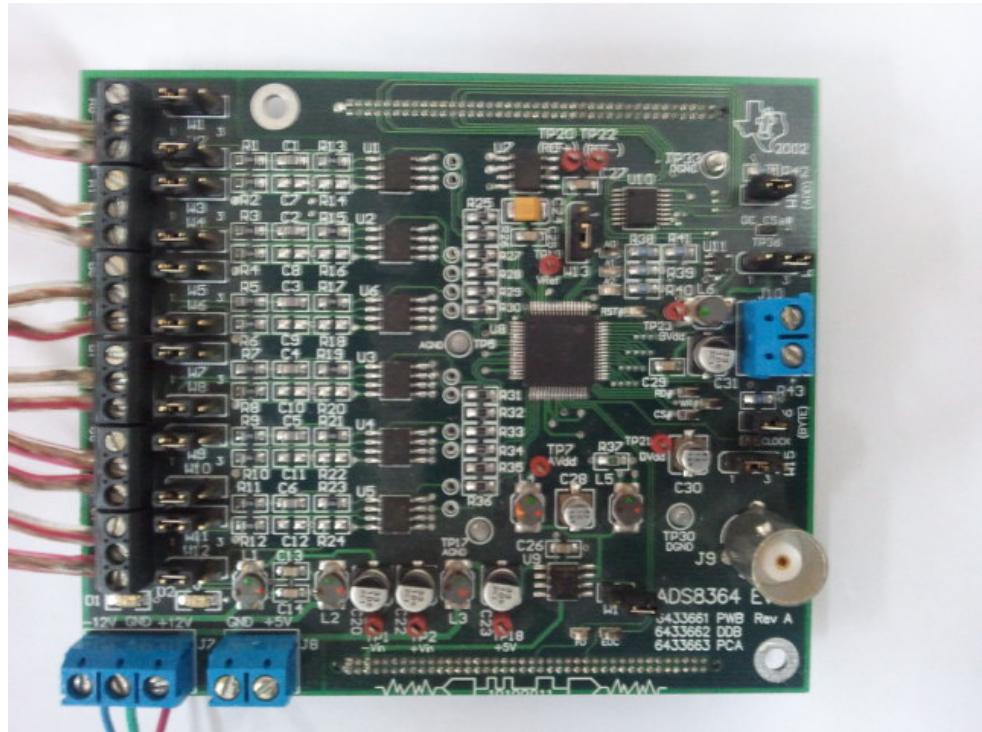

| 4.1.3    | TI ADS8364 ADC Evaluation Module . . . . .           | 39 |

| 4.2      | Description of FPGA Building Blocks . . . . .        | 40 |

| 4.2.1    | Transmit Pulse Generator Module . . . . .            | 40 |

| 4.2.2    | PCM1602 DAC Controller Module . . . . .              | 43 |

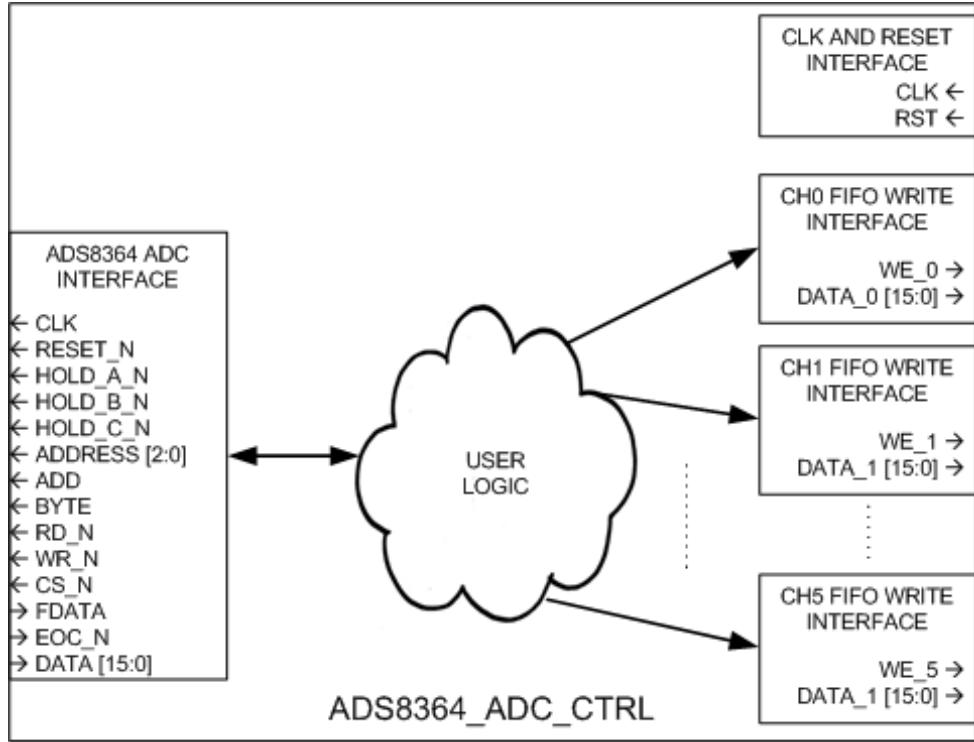

| 4.2.3    | ADS8364 ADC Controller Module . . . . .              | 45 |

| 4.2.4    | DC Offset Remover . . . . .                          | 47 |

| 4.2.5    | 6-Channel FIR Low-Pass Filter Module . . . . .       | 50 |

| 4.2.6    | Receive Delay and Sum Beamformer Module . . . . .    | 54 |

| 4.2.7    | Correlator Module . . . . .                          | 57 |

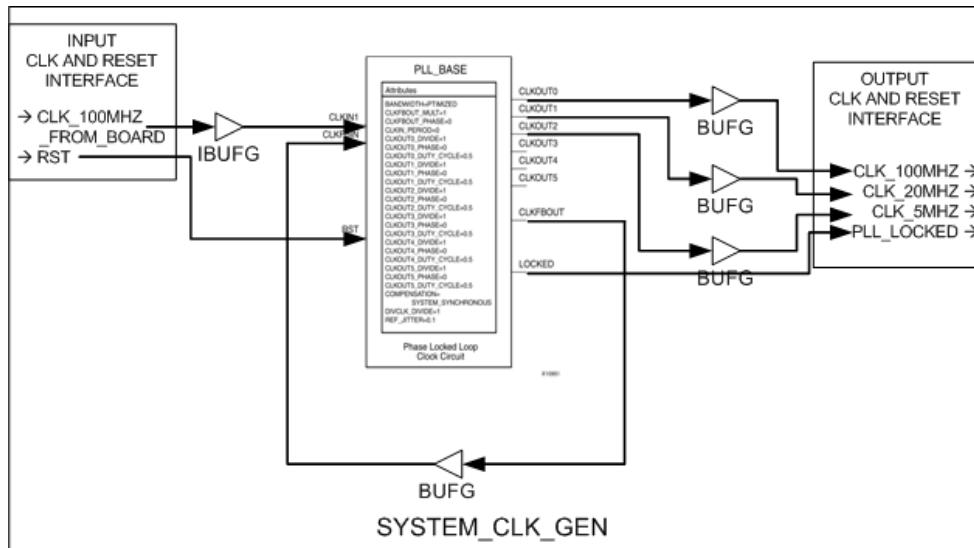

| 4.2.8    | Clock Generation Module . . . . .                    | 61 |

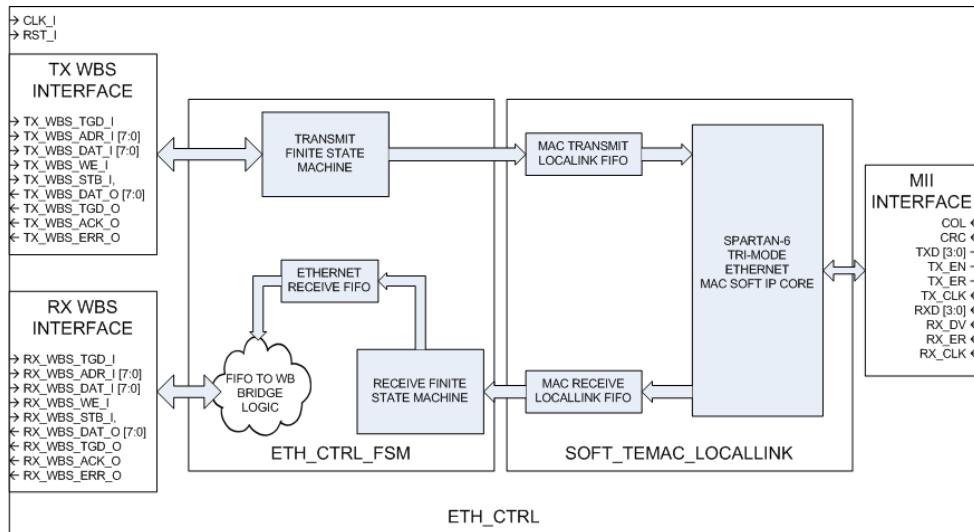

| 4.2.9    | Ethernet Controller Module . . . . .                 | 62 |

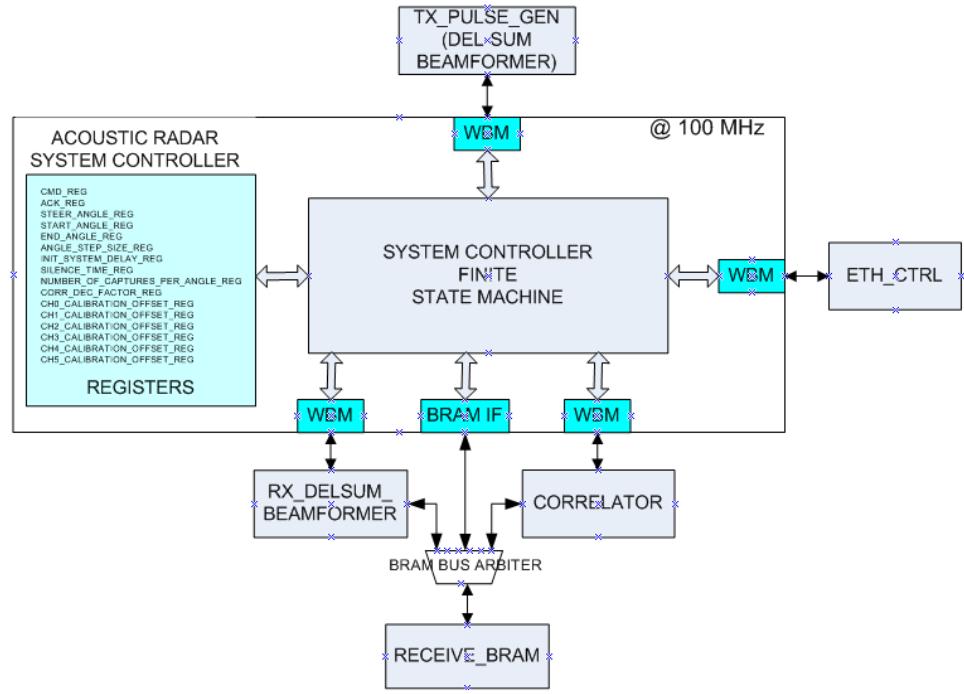

| 4.2.10   | Acoustic Radar System Controller Module . . . . .    | 65 |

| 4.2.10.1 | System Registers . . . . .                           | 66 |

| 4.2.10.2 | Description of System Operation . . . . .            | 68 |

| 5        | EXPERIMENTAL RESULTS . . . . .                       | 77 |

| 5.1      | PC Controlled Transmit Beamformer . . . . .          | 77 |

| 5.1.1    | 5.1.1 Description of the System Parameters . . . . . | 78 |

| 5.1.2    | Description of System Operation . . . . .            | 79 |

| 5.1.2.1  | UART_TO_PULSE_GEN_FSM MODULE . . . . .               | 79 |

| 5.1.2.2  | UART_CTRL . . . . .                                  | 81 |

|                      |                                                              |     |

|----------------------|--------------------------------------------------------------|-----|

| 5.1.3                | Results . . . . .                                            | 82  |

| 5.2                  | Acoustic Radar Experiments . . . . .                         | 88  |

| 5.2.1                | Experiment 1: ADC Capture over UDP . . . . .                 | 88  |

| 5.2.2                | Experiment 2: Acoustic Radar System Evaluation . . . . .     | 91  |

| 6                    | CONCLUSIONS . . . . .                                        | 115 |

| REFERENCES . . . . . |                                                              | 117 |

| APPENDICES           |                                                              |     |

| A                    | MODULE PORT DESCRIPTIONS . . . . .                           | 119 |

| A.1                  | TRANSMIT PULSE GENERATOR PORT DESCRIPTIONS . . . . .         | 119 |

| A.2                  | PCM1602 DAC CONTROLLER PORT DESCRIPTIONS . . . . .           | 120 |

| A.3                  | ADS8364 ADC CONTROLLER PORT DESCRIPTIONS . . . . .           | 122 |

| A.4                  | DC OFFSET REMOVER PORT DESCRIPTIONS . . . . .                | 124 |

| A.5                  | 6-CHANNEL FIR LOW-PASS FILTER PORT DESCRIPTIONS . . . . .    | 125 |

| A.6                  | RECEIVE DELAY AND SUM BEAMFORMER PORT DESCRIPTIONS . . . . . | 125 |

| A.7                  | CORRELATOR PORT DESCRIPTIONS . . . . .                       | 128 |

| A.8                  | CLOCK GENERATOR PORT DESCRIPTIONS . . . . .                  | 130 |

| A.9                  | ETHERNET CONTROLLER PORT DESCRIPTIONS . . . . .              | 131 |

## LIST OF TABLES

### TABLES

|                                                                           |     |

|---------------------------------------------------------------------------|-----|

| Table 4.1 Implemented Low-Pass Filter Specifications . . . . .            | 50  |

| Table A.1 Transmit Pulse Generator Module Port Description . . . . .      | 120 |

| Table A.2 PCM1602 DAC Controller Port Description . . . . .               | 122 |

| Table A.3 ADS8364 ADC Controller Port Description . . . . .               | 124 |

| Table A.4 DC Offset Remover Port Description . . . . .                    | 125 |

| Table A.5 6-Channel FIR Low-Pass Filter Module Port Description . . . . . | 125 |

| Table A.6 Receive Delay and Sum Beamformer Port Description . . . . .     | 128 |

| Table A.7 Correlator Port Description . . . . .                           | 130 |

| Table A.8 Clock Generator Port Description . . . . .                      | 131 |

| Table A.9 Ethernet Controller Port Description . . . . .                  | 133 |

## LIST OF FIGURES

### FIGURES

|                                                                                                                                                      |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1 Single antenna vs. array of antennas . . . . .                                                                                            | 4  |

| Figure 2.2 Three dimensional space in spherical coordinates . . . . .                                                                                | 5  |

| Figure 2.3 A sensor array receiving the transmitted signal from a point source . . . . .                                                             | 6  |

| Figure 2.4 Energy spectrum of a bandpass signal . . . . .                                                                                            | 8  |

| Figure 2.5 Lowpass equivalent of the bandpass signal whose spectrum is given in<br>Figure 2.4 . . . . .                                              | 9  |

| Figure 2.6 ULA Delay-and-Sum Beamforming . . . . .                                                                                                   | 17 |

| Figure 2.7 Directivity response of the Acoustic Radar Beamformer with steer angle<br>chosen as 90 ° (Same for transmit and receive arrays) . . . . . | 18 |

| Figure 3.1 Acoustic Radar System Structure . . . . .                                                                                                 | 22 |

| Figure 3.2 Phased Array Transmit Steer . . . . .                                                                                                     | 24 |

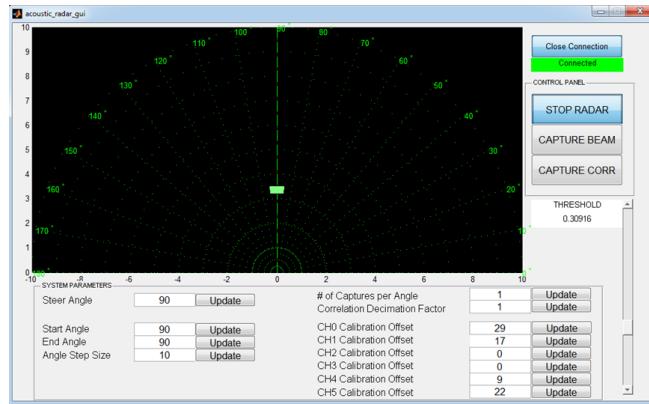

| Figure 3.3 Acoustic Radar Display Unit . . . . .                                                                                                     | 26 |

| Figure 3.4 The Acoustic Radar Pulse . . . . .                                                                                                        | 31 |

| Figure 3.5 Acoustic Radar Pulse Magnitude Response . . . . .                                                                                         | 32 |

| Figure 3.6 Ambiguity function for the Acoustic Radar Pulse . . . . .                                                                                 | 33 |

| Figure 3.7 Ambiguity function for an unmodulated (left) pulse and a chirp pulse (right)<br>of the same length as the Acoustic Radar Pulse . . . . .  | 33 |

| Figure 4.1 Implemented Radar System Structure . . . . .                                                                                              | 34 |

| Figure 4.2 Top view and functional block diagram of ATLYS FPGA Board . . . . .                                                                       | 35 |

| Figure 4.3 PCB for connecting ATLYS Board to ADS8364 ADC EVM . . . . .                                                                               | 37 |

| Figure 4.4 PCM1602 DAC Evaluation Module Functional Block Diagram . . . . .                                                                          | 38 |

| Figure 4.5 Top view of ADS8364 Evaluation Module . . . . .                                                                                           | 39 |

|             |                                                                          |    |

|-------------|--------------------------------------------------------------------------|----|

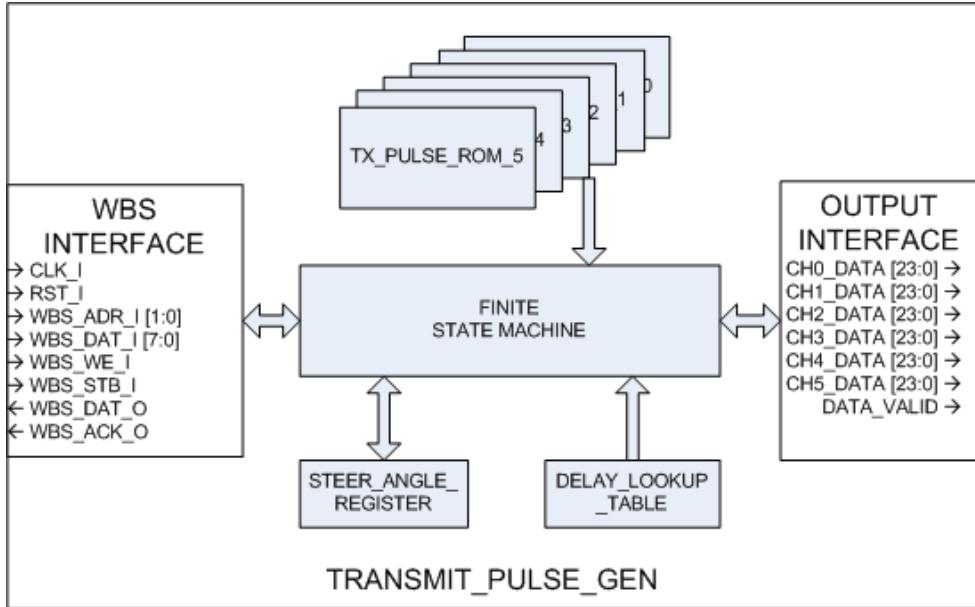

| Figure 4.6  | Transmit Pulse Generator Functional Block Diagram                        | 41 |

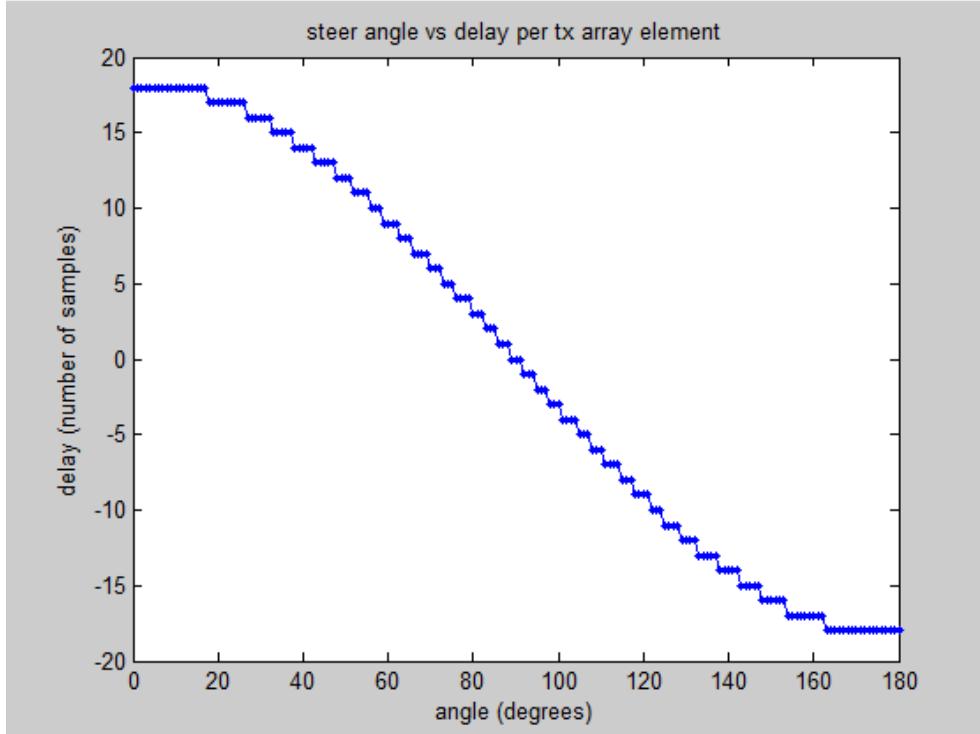

| Figure 4.7  | Delay Lookup Table Content                                               | 42 |

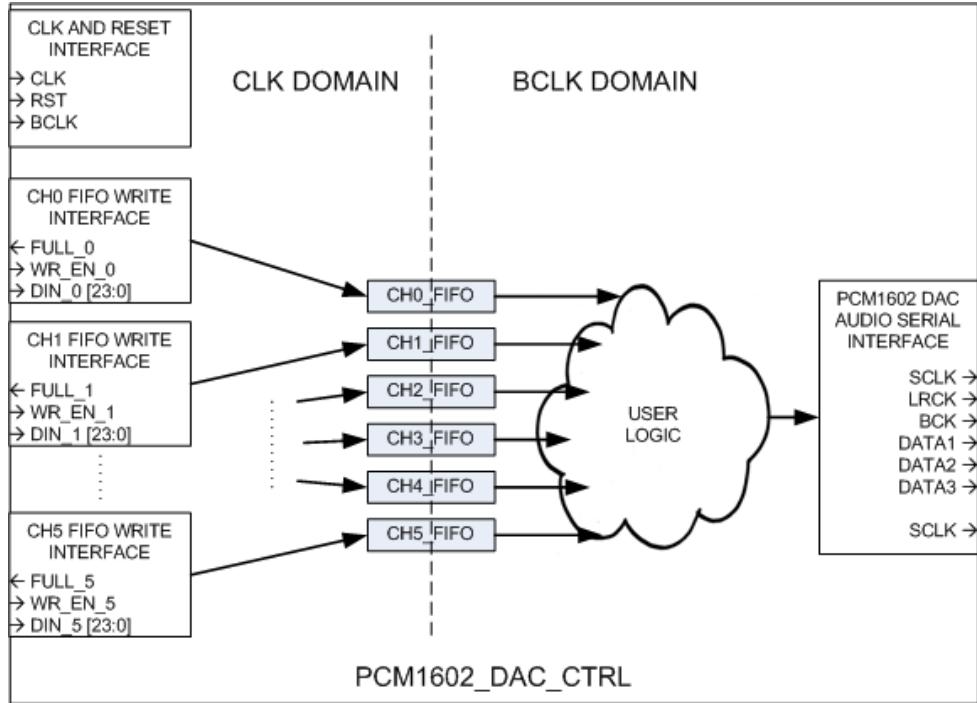

| Figure 4.8  | PCM1602 DAC Controller Functional Block Diagram                          | 44 |

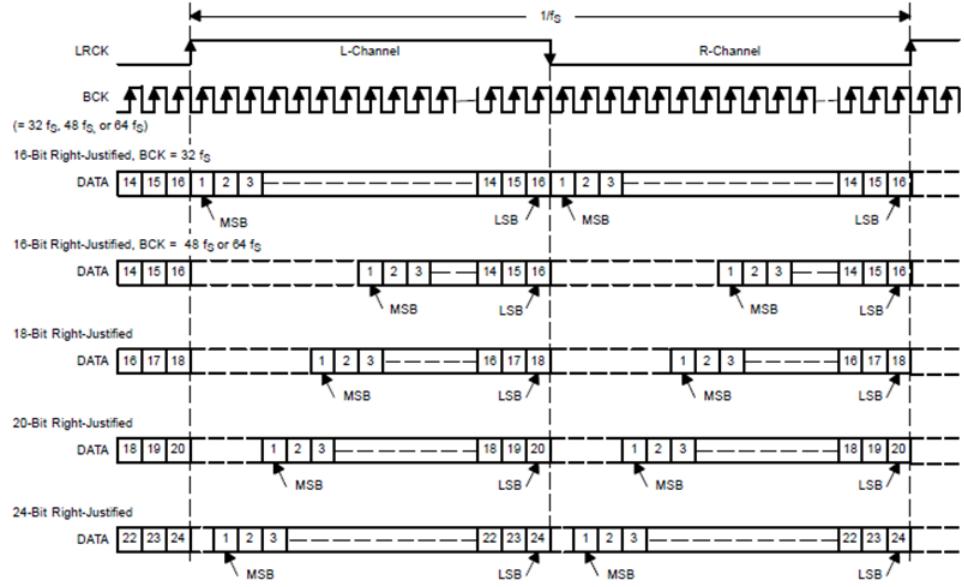

| Figure 4.9  | Standard Audio Data Input Formats                                        | 45 |

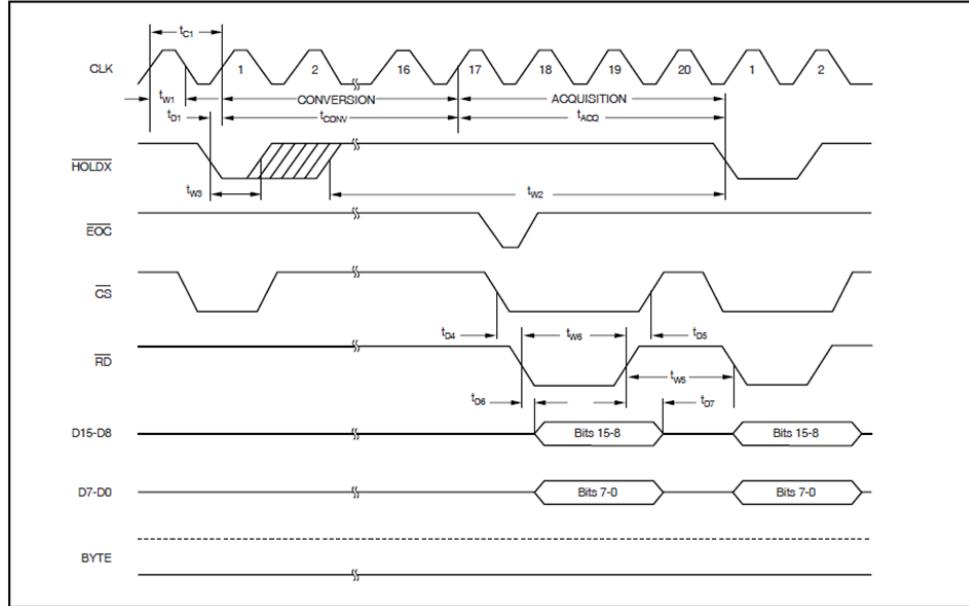

| Figure 4.10 | ADS8364 Data Capture Timing Diagram                                      | 46 |

| Figure 4.11 | ADS8364 Data Capture Timing Diagram                                      | 47 |

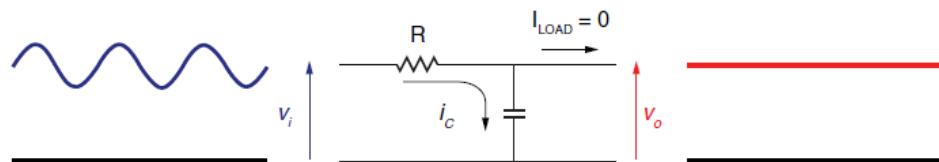

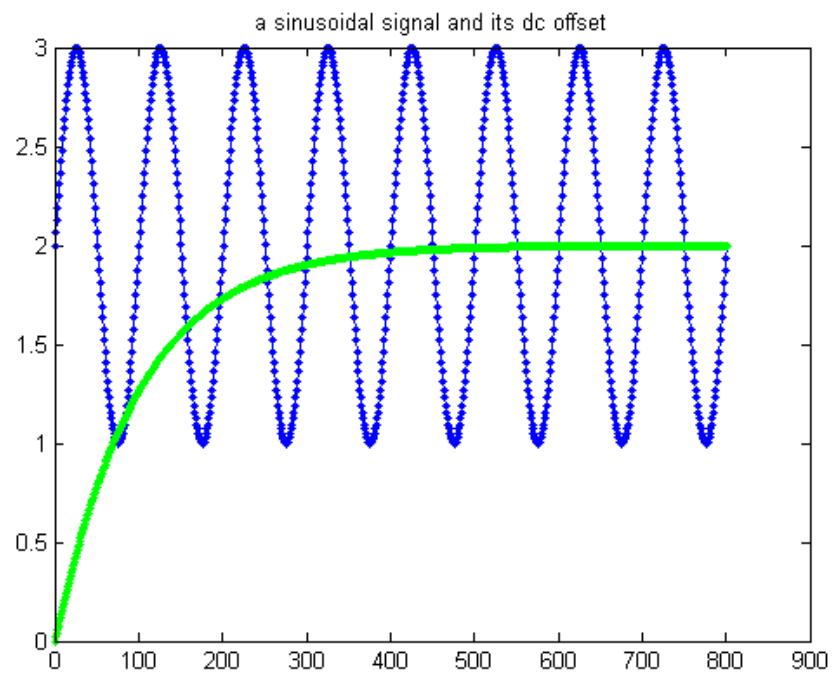

| Figure 4.12 | Analog RC Circuit to Determine the DC Offset of a Signal                 | 47 |

| Figure 4.13 | DC offset of a sinusoidal signal calculated by the RC Circuit            | 49 |

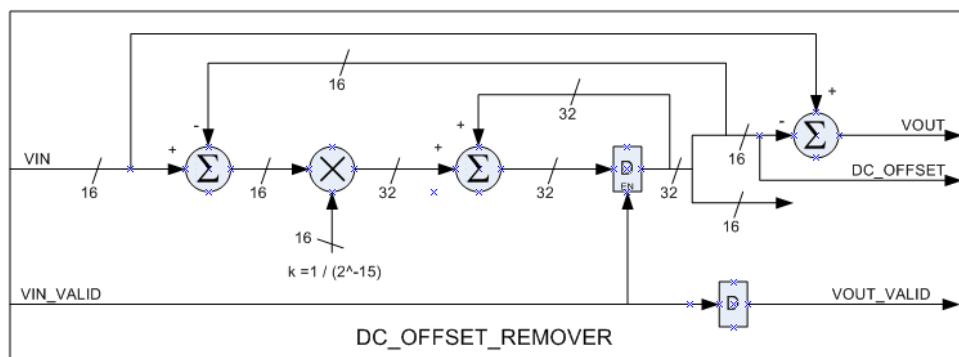

| Figure 4.14 | <i>DC Offset Remover</i> , a digital implementation of the RC Circuit    | 49 |

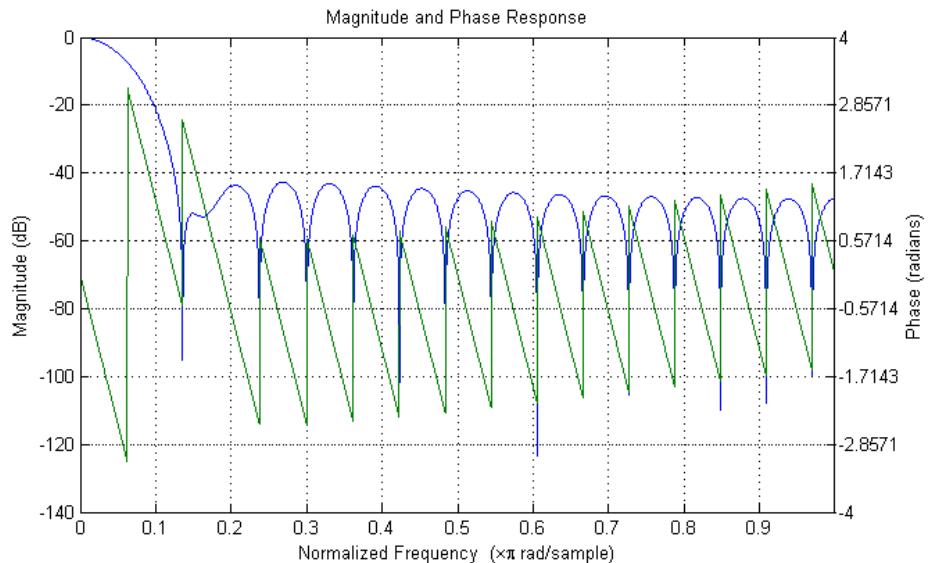

| Figure 4.15 | Frequency Response of the Implemented Low-Pass Filter                    | 50 |

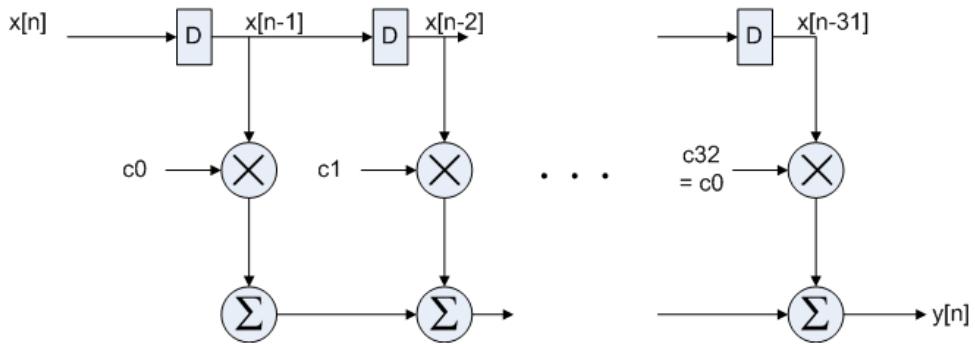

| Figure 4.16 | A direct form realization of an FIR filter (1 channel)                   | 51 |

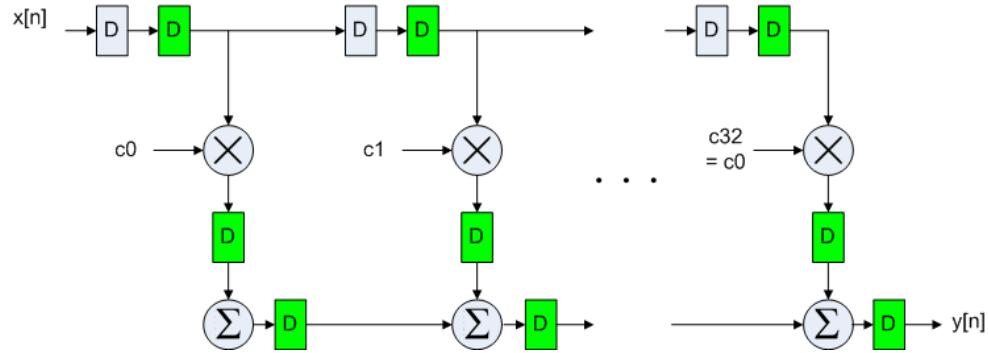

| Figure 4.17 | Pipelined structure of the FIR filter to improve timing (1 channel)      | 52 |

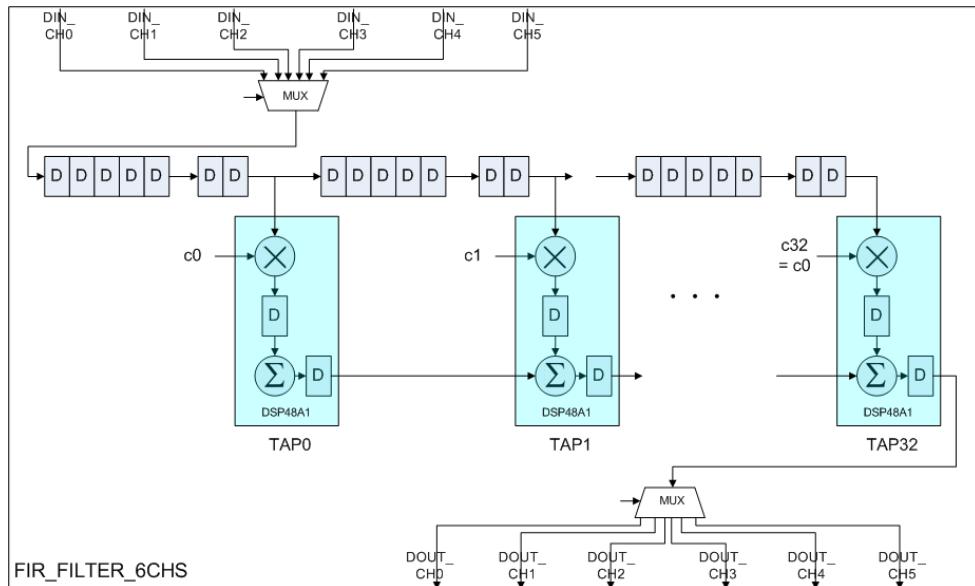

| Figure 4.18 | 6-channel low-pass FIR filter structure                                  | 52 |

| Figure 4.19 | DSP48A1 Slice                                                            | 53 |

| Figure 4.20 | DSP48A1 Slice, used parts highlighted                                    | 54 |

| Figure 4.21 | Receiver Delay-and-Sum Beamformer Functional Block Diagram               | 55 |

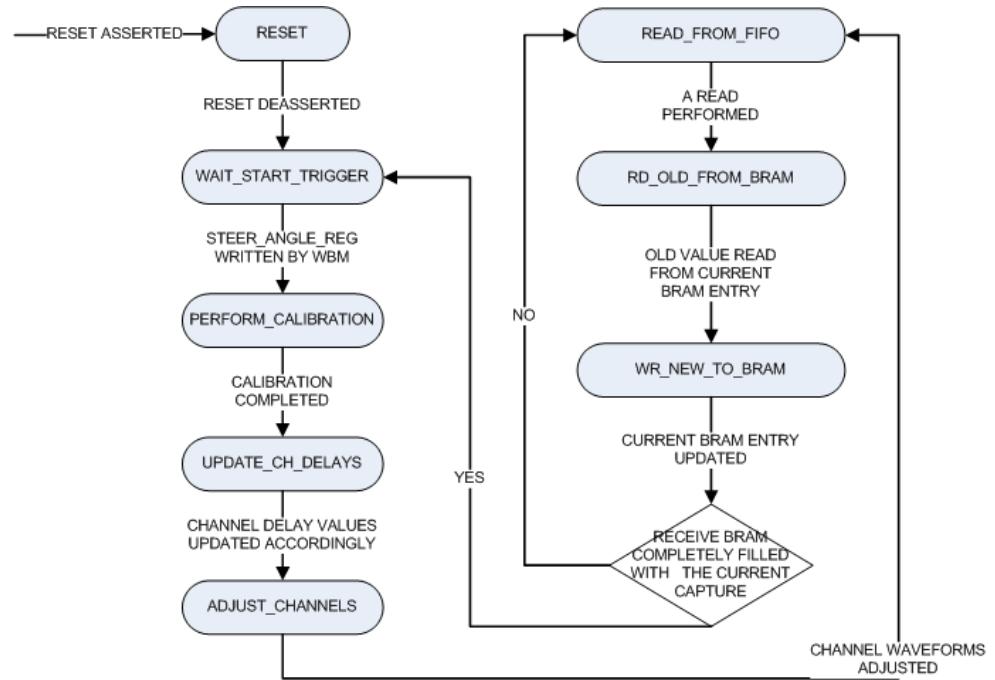

| Figure 4.22 | Receiver Delay-and-Sum Beamformer Finite State Machine Flow Diagram      | 56 |

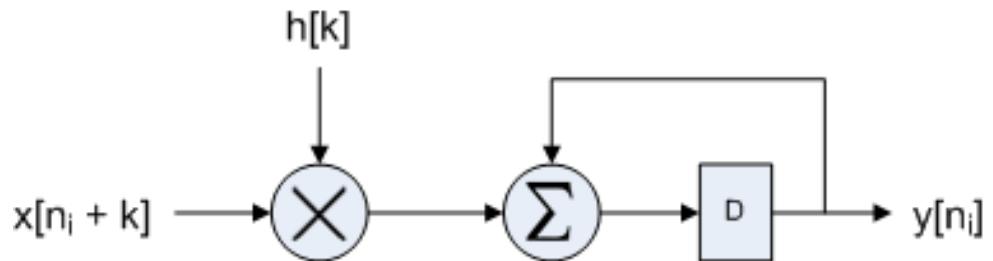

| Figure 4.23 | Multiply-Accumulate circuit which used to calculate a correlation sample | 58 |

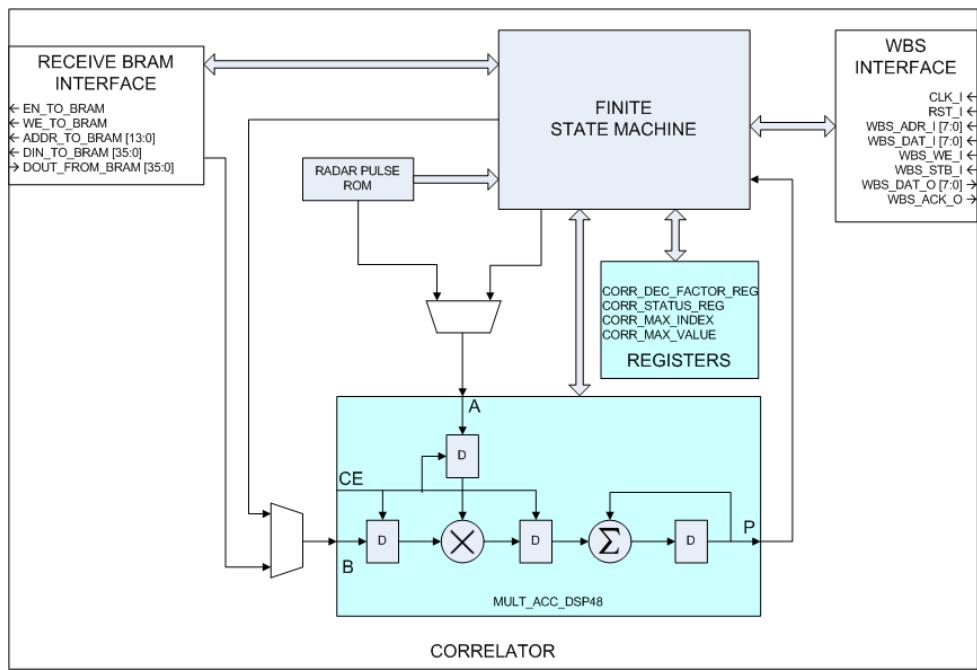

| Figure 4.24 | Correlator Functional Block Diagram                                      | 60 |

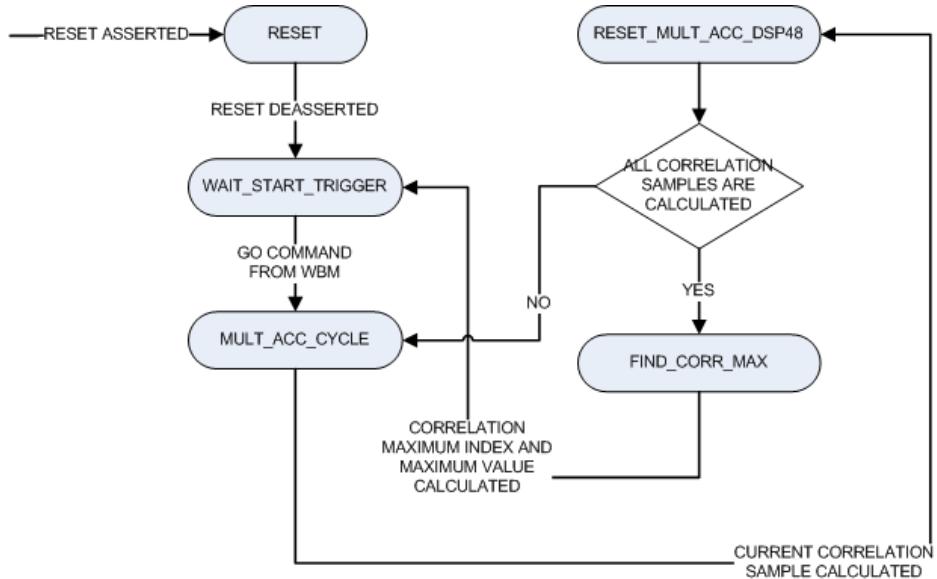

| Figure 4.25 | Correlator Finite State Machine Flow Diagram                             | 60 |

| Figure 4.26 | Clock Generation Module Functional Block Diagram                         | 61 |

| Figure 4.27 | Ethernet Controller Module Functional Block Diagram                      | 63 |

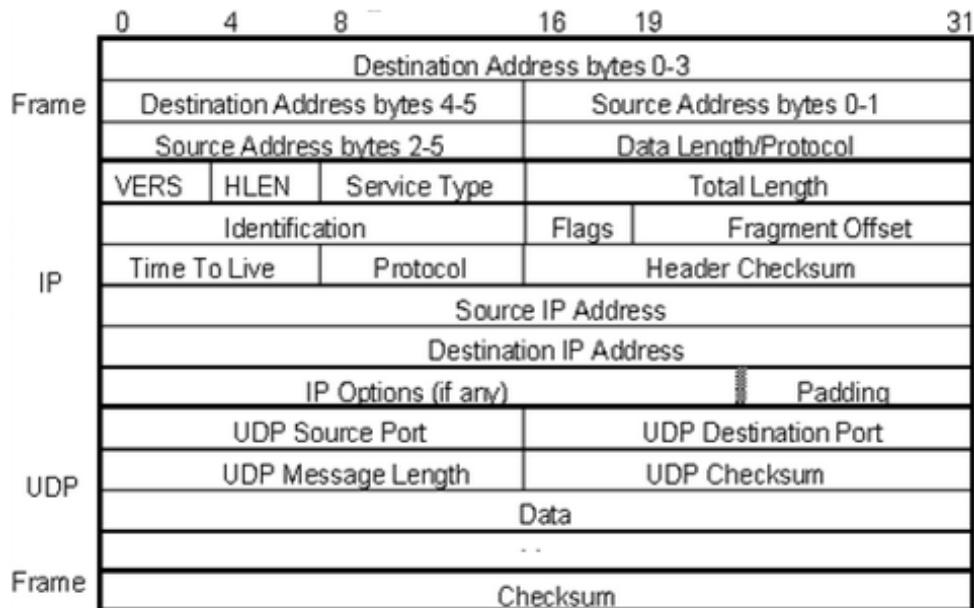

| Figure 4.28 | User Datagram Protocol Packet Format                                     | 64 |

| Figure 4.29 | Acoustic Radar System Controller Functional Diagram                      | 66 |

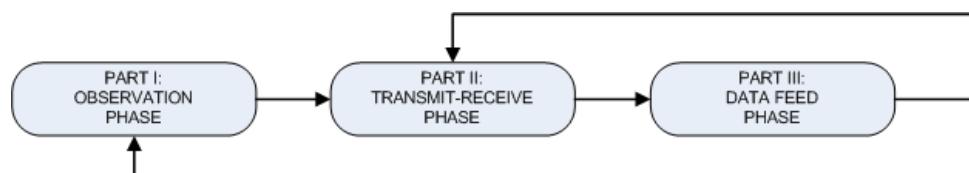

| Figure 4.30 | Acoustic Radar System Controller Finite State Machine Parts              | 68 |

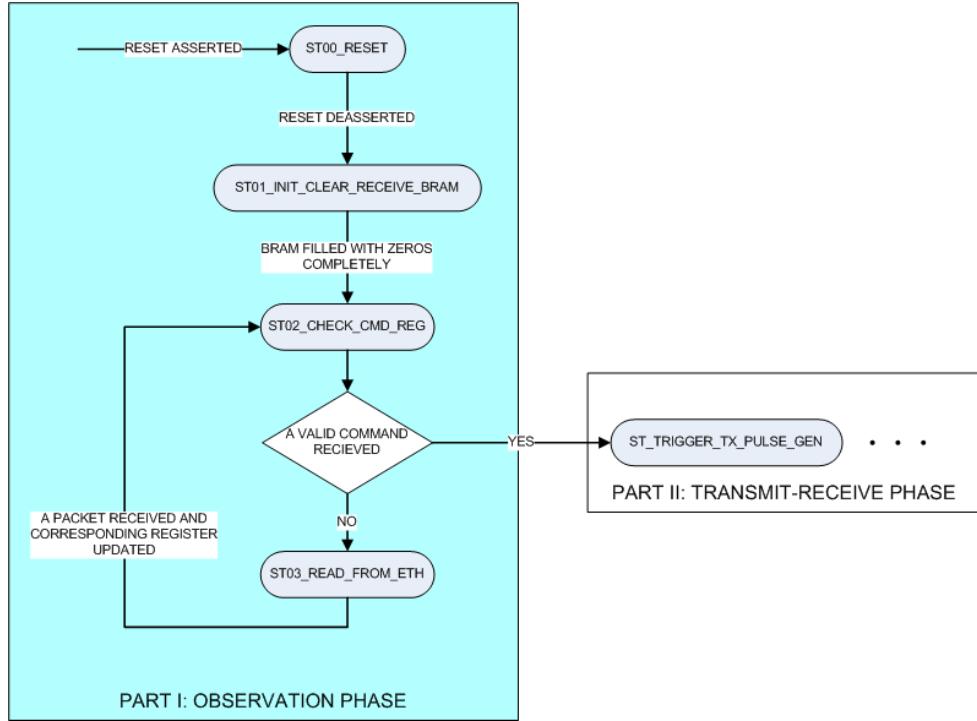

| Figure 4.31 | Acoustic Radar State Machine Part I: Observation Phase                   | 70 |

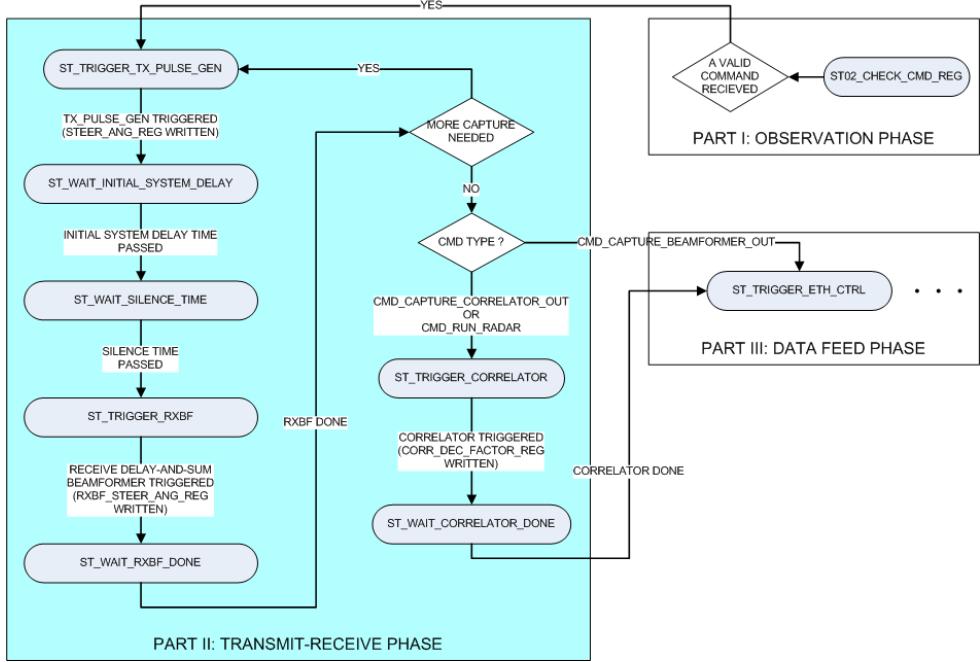

| Figure 4.32 | Acoustic Radar State Machine Part II: Transmit-Receive Phase             | 71 |

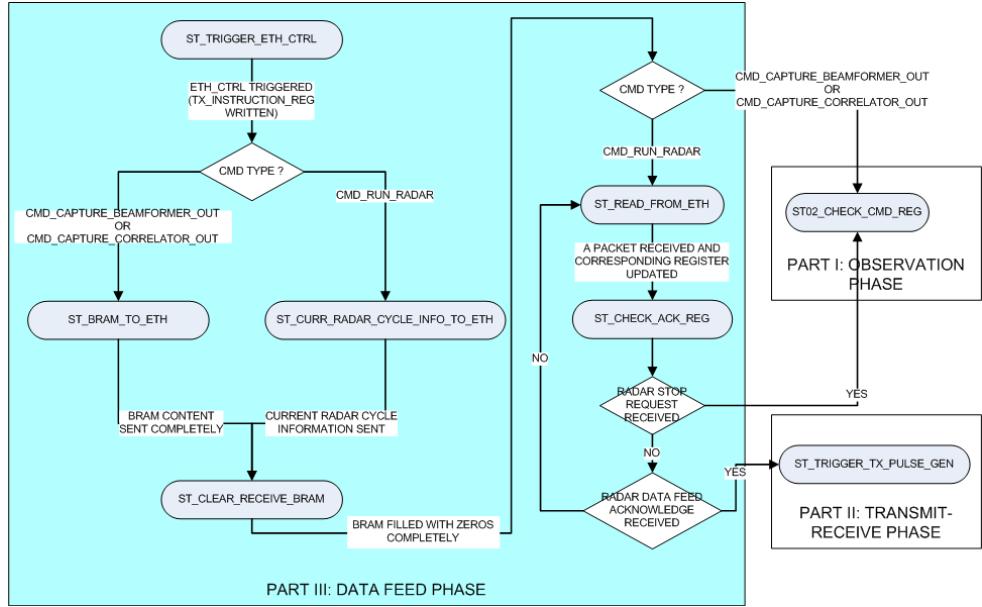

| Figure 4.33 | Acoustic Radar State Machine Part III: Data Feed Phase                   | 74 |

|                                                                                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.1 PC Controlled Transmit Beamformer Functional Block Diagram . . . . .                                                                                | 78  |

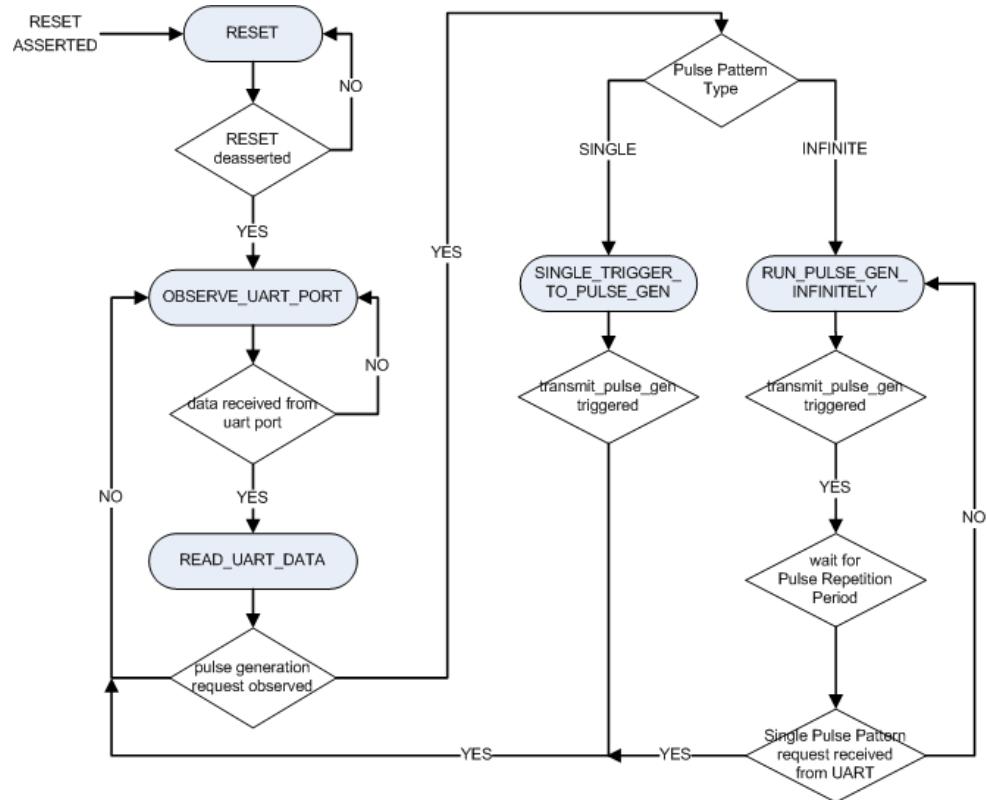

| Figure 5.2 PC Controlled Transmit Beamformer Finite State Machine Flow Diagram . . . . .                                                                       | 80  |

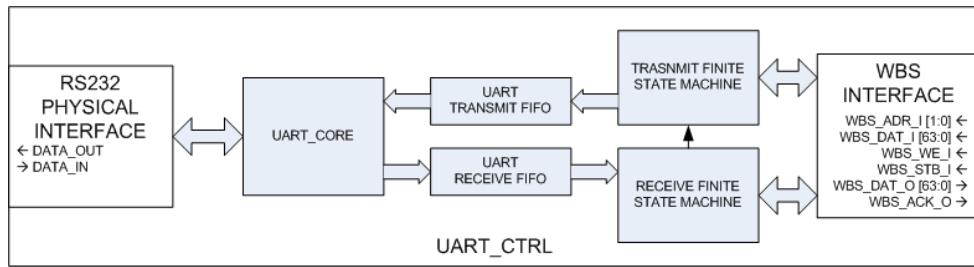

| Figure 5.3 UART Controller Module Functional Block Diagram . . . . .                                                                                           | 81  |

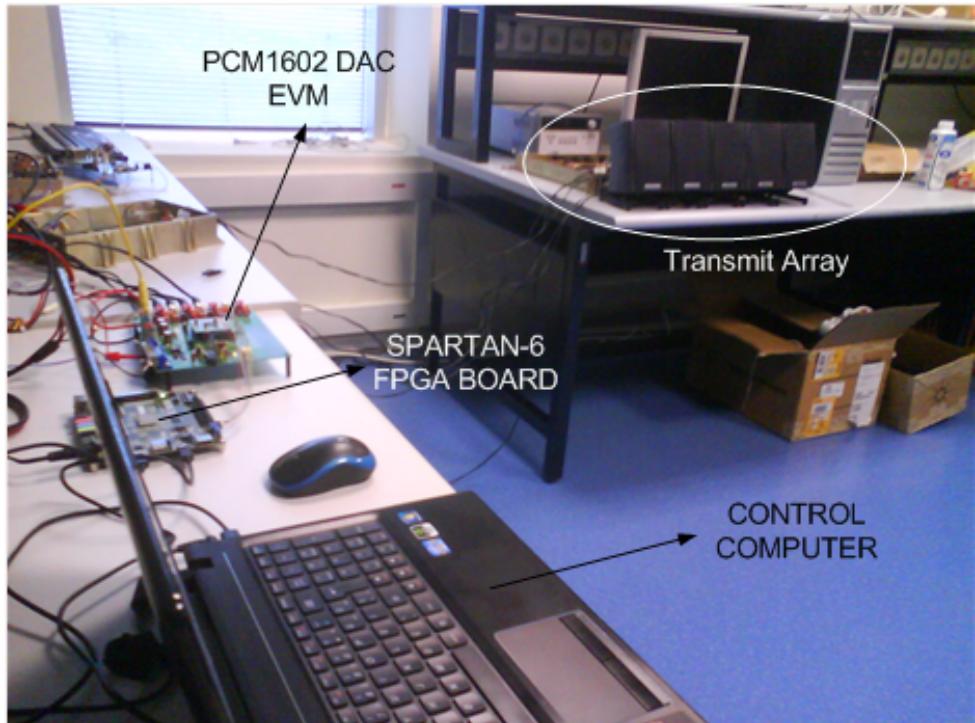

| Figure 5.4 PC Controlled Transmit Beamformer Test Setup . . . . .                                                                                              | 82  |

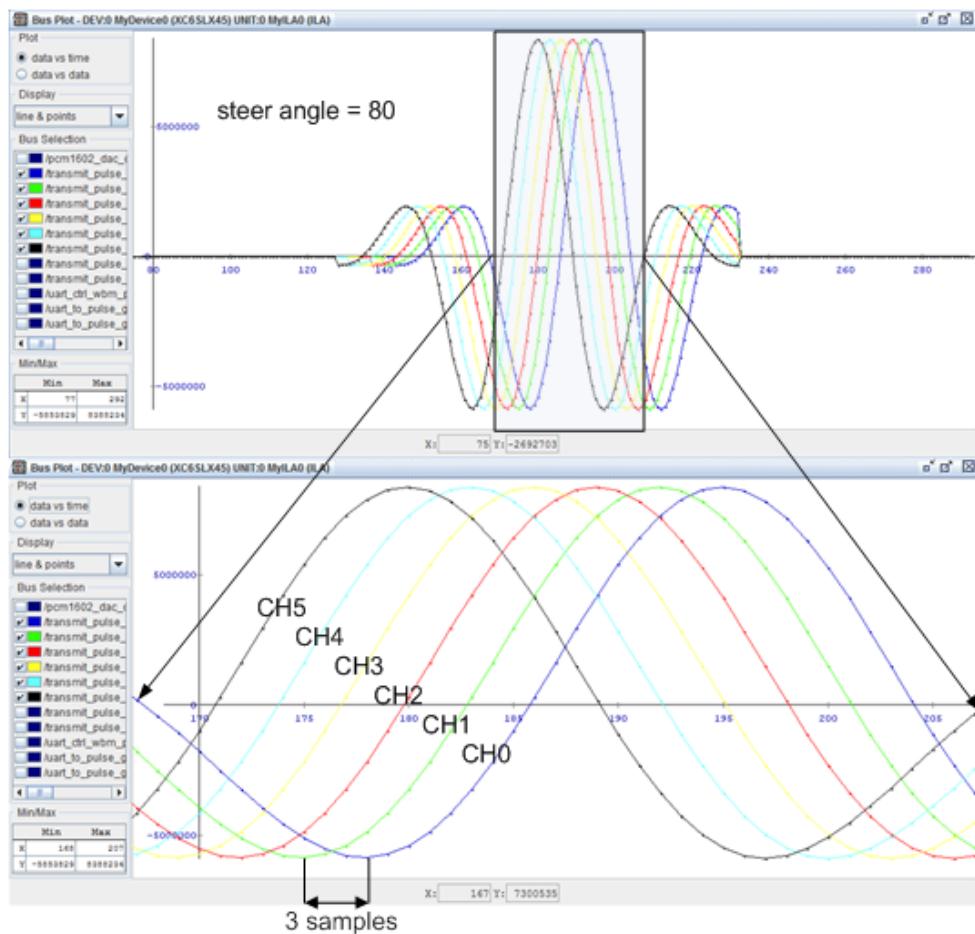

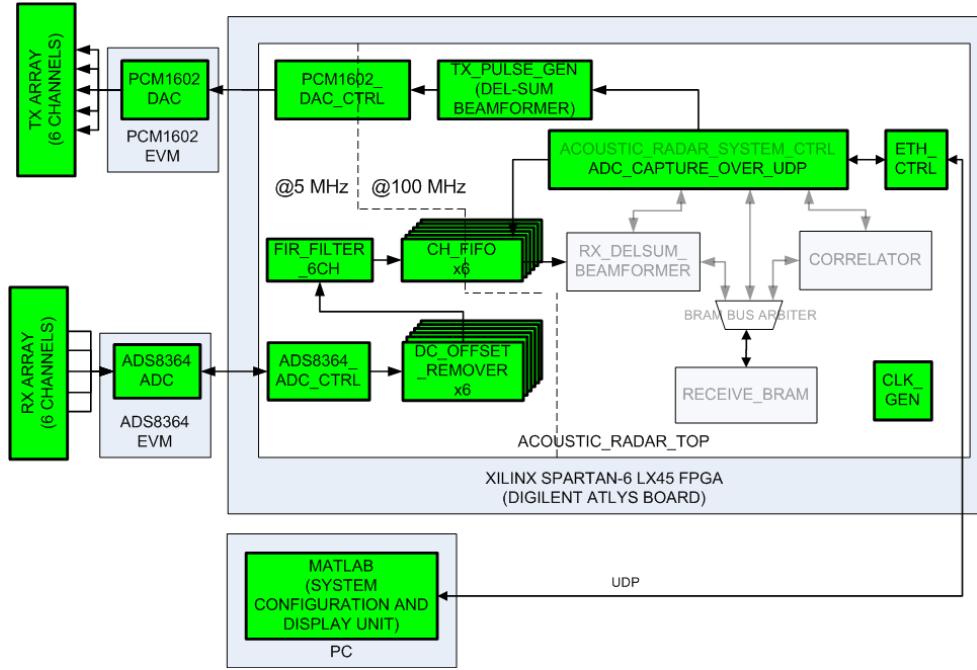

| Figure 5.5 <i>Transmit Pulse Generator</i> output, <i>steer angle</i> is 80° . . . . .                                                                         | 84  |

| Figure 5.6 <i>Transmit Pulse Generator</i> output, <i>steer angle</i> is 170° . . . . .                                                                        | 85  |

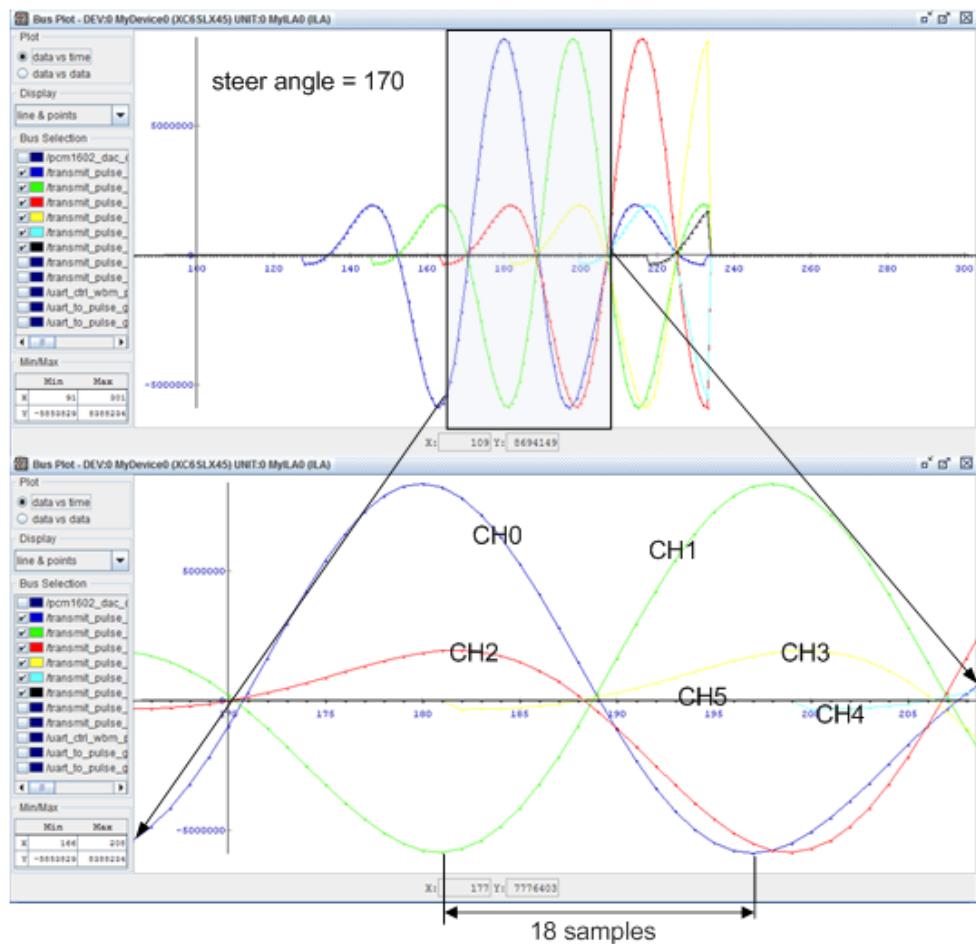

| Figure 5.7 <i>Transmit Pulse Generator</i> output in <i>infinite mode</i> for three different <i>pulse repetition parameter</i> values . . . . .               | 87  |

| Figure 5.8 ADC Capture over UDP Functional Block Diagram . . . . .                                                                                             | 89  |

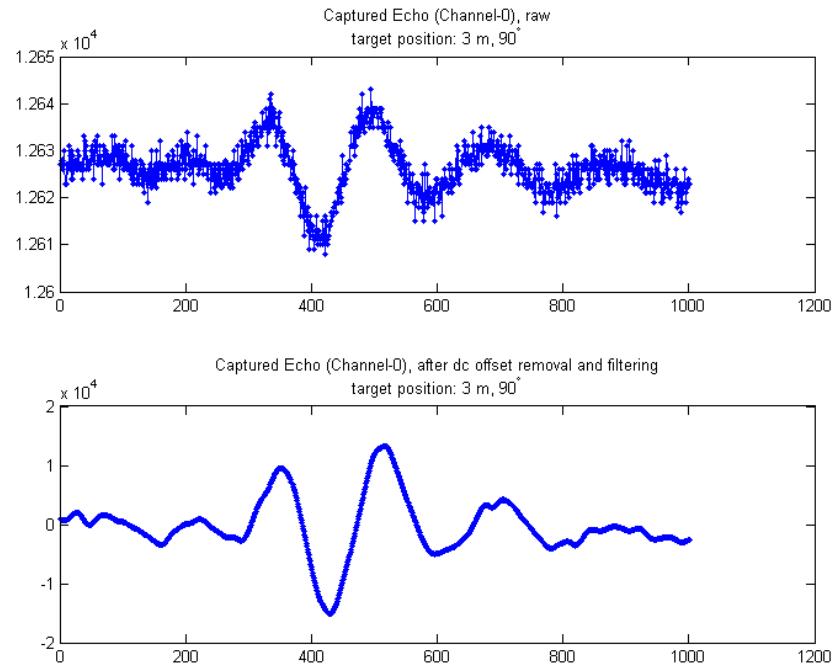

| Figure 5.9 Channel-0 Captured Echo Comparison, Raw vs DC Offset Removed, Low-Pass Filtered Waveform . . . . .                                                  | 90  |

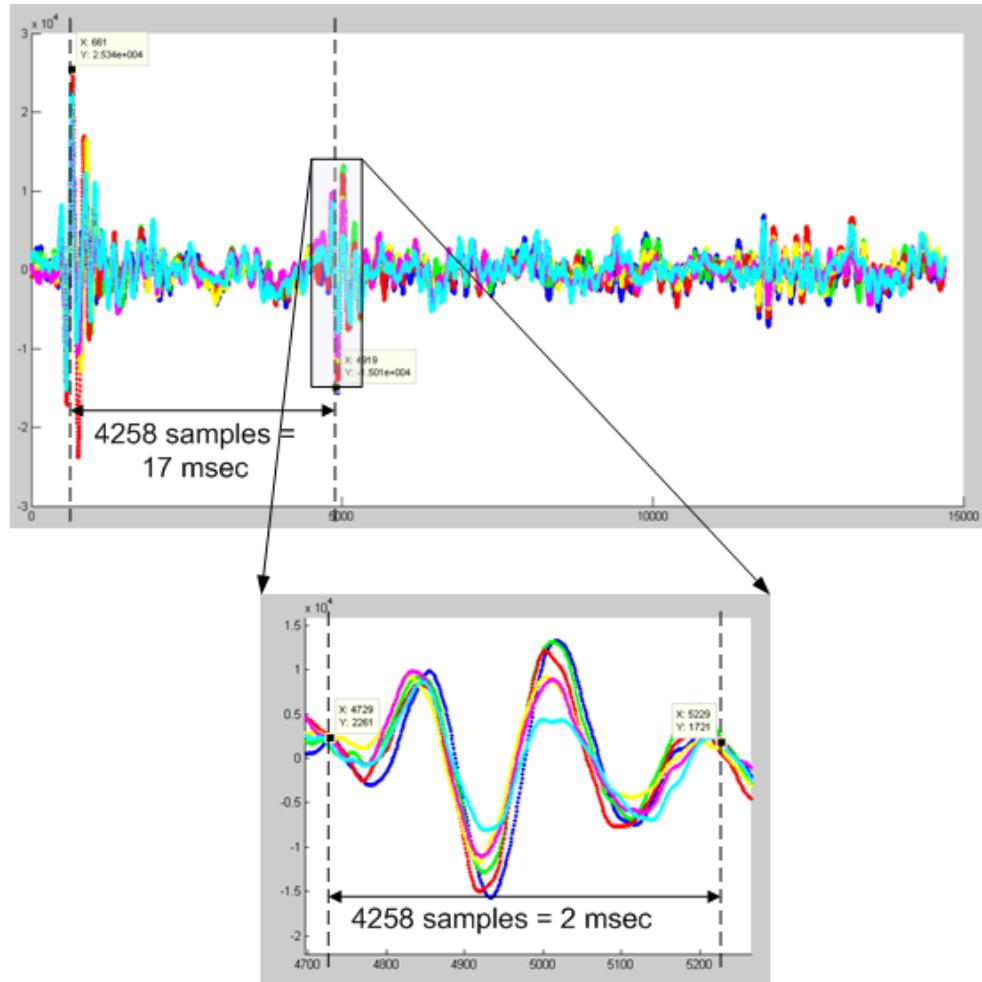

| Figure 5.10 6-Channel Capture, duration: 58.8 msec (1 PRF), target position: 3 m, 90° . . . . .                                                                | 91  |

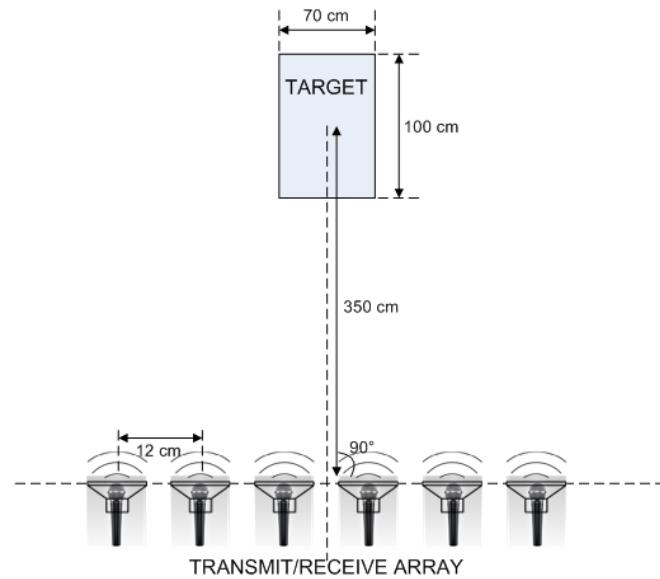

| Figure 5.11 Target placement for Scenario 1 . . . . .                                                                                                          | 92  |

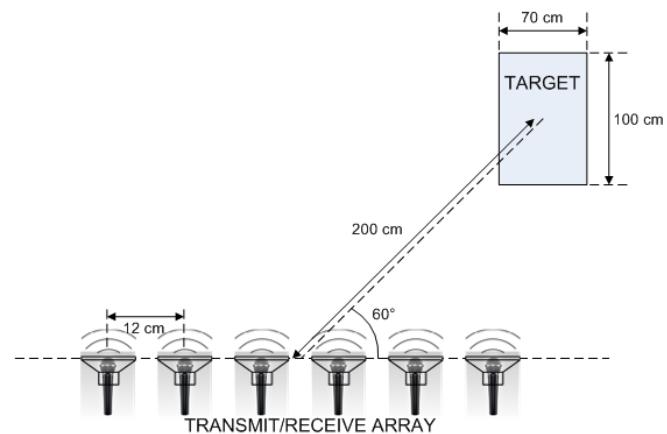

| Figure 5.12 Target placement for Scenario 2 . . . . .                                                                                                          | 92  |

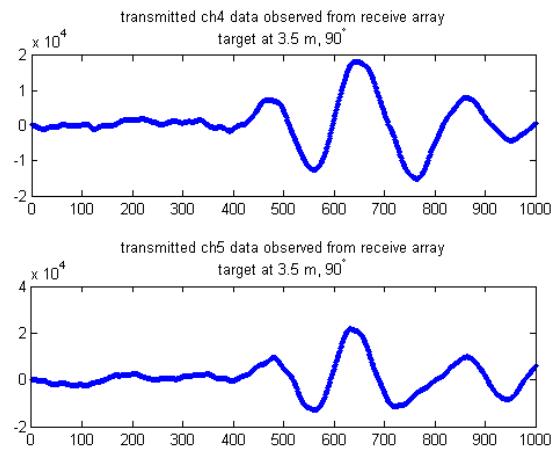

| Figure 5.13 Transmitted CH4 and CH5 waveforms from the receive array's point of view, no phase difference observed, target position: 3.5 m, 90° . . . . .      | 94  |

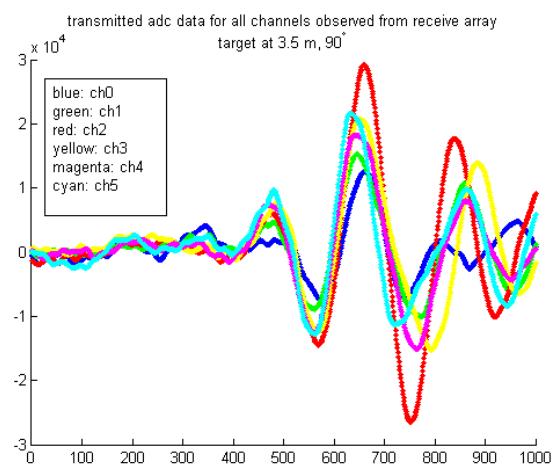

| Figure 5.14 Transmitted waveforms for all channels from the receive array's point of view, no phase difference observed, target position: 3.5 m, 90° . . . . . | 94  |

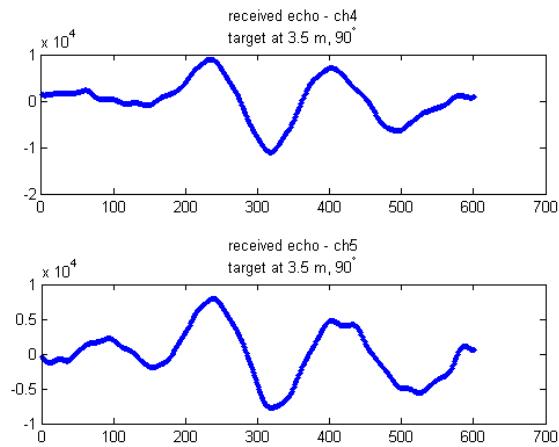

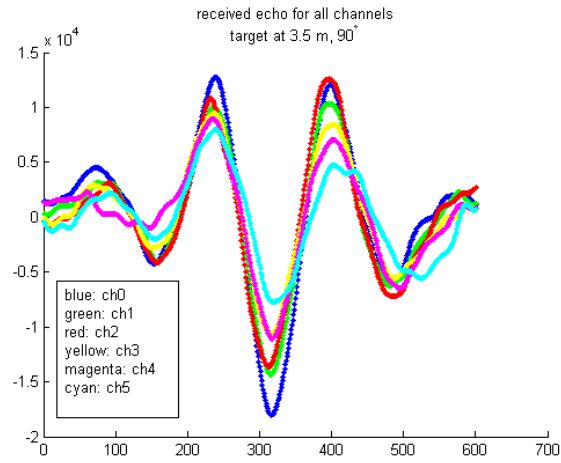

| Figure 5.15 Received echo from CH4 and CH5, no phase difference observed, target position: 3.5 m, 90° . . . . .                                                | 95  |

| Figure 5.16 Received echo from all channels, no phase difference observed, target position: 3.5 m, 90° . . . . .                                               | 96  |

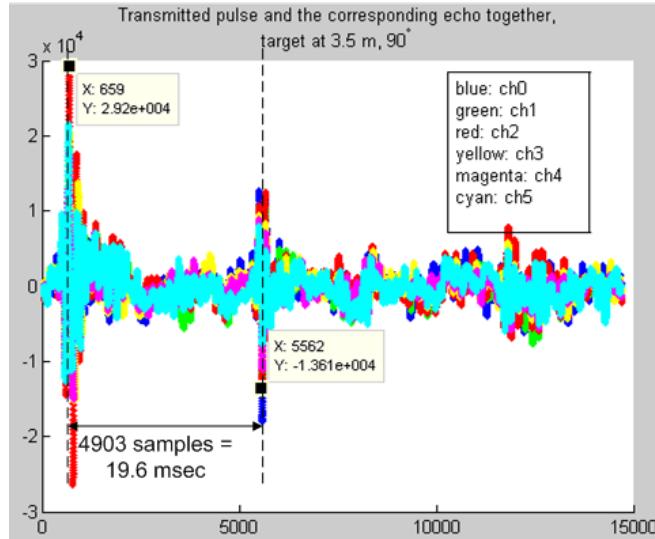

| Figure 5.17 Entire transmit-receive cycle captured, target position: 3.5 m, 90° . . . . .                                                                      | 97  |

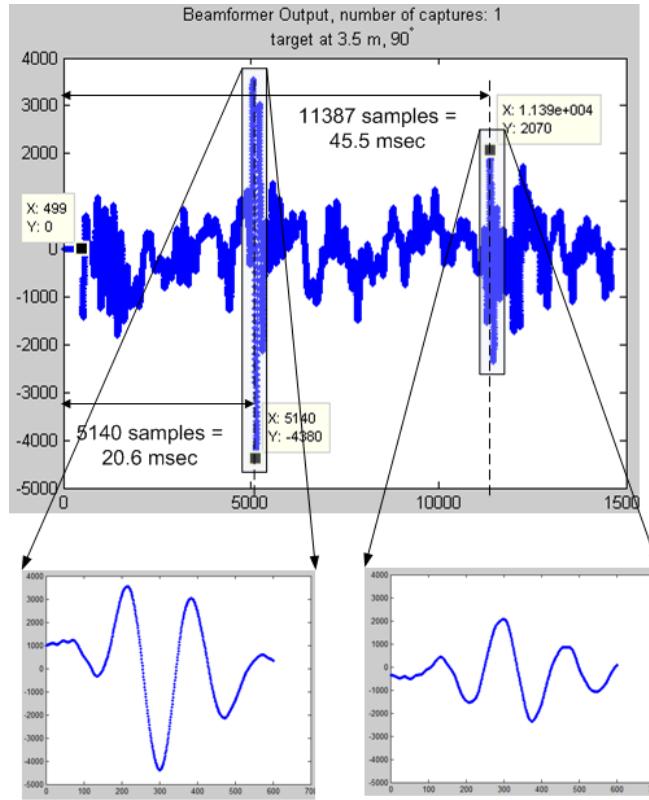

| Figure 5.18 Beamformer Output, number of captures: 1, target position: 3.5 m, 90° . . . . .                                                                    | 98  |

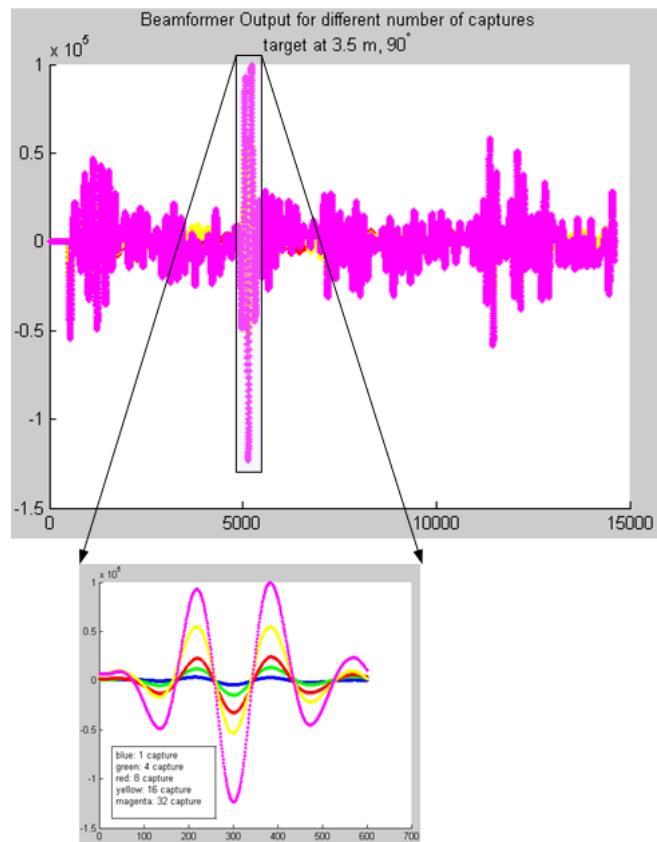

| Figure 5.19 Beamformer Output for different values of <i>number of captures per angle</i> parameter, target position: 3.5 m, 90° . . . . .                     | 99  |

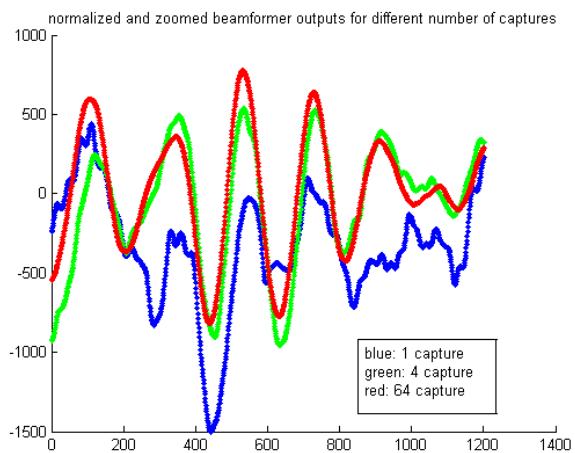

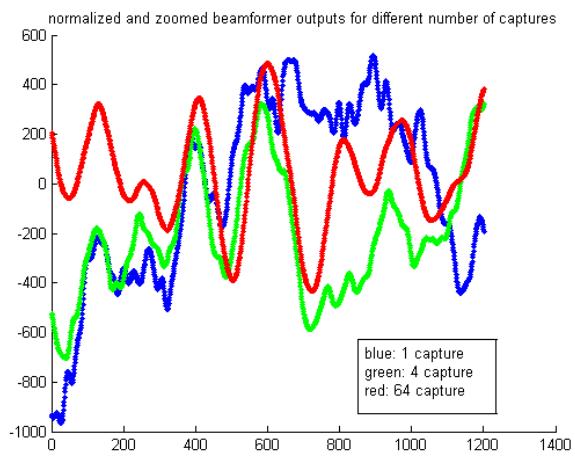

| Figure 5.20 Normalized beamformer outputs zoomed, <i>number of captures</i> parameter varied, target position: 3.5 m, 90° . . . . .                            | 99  |

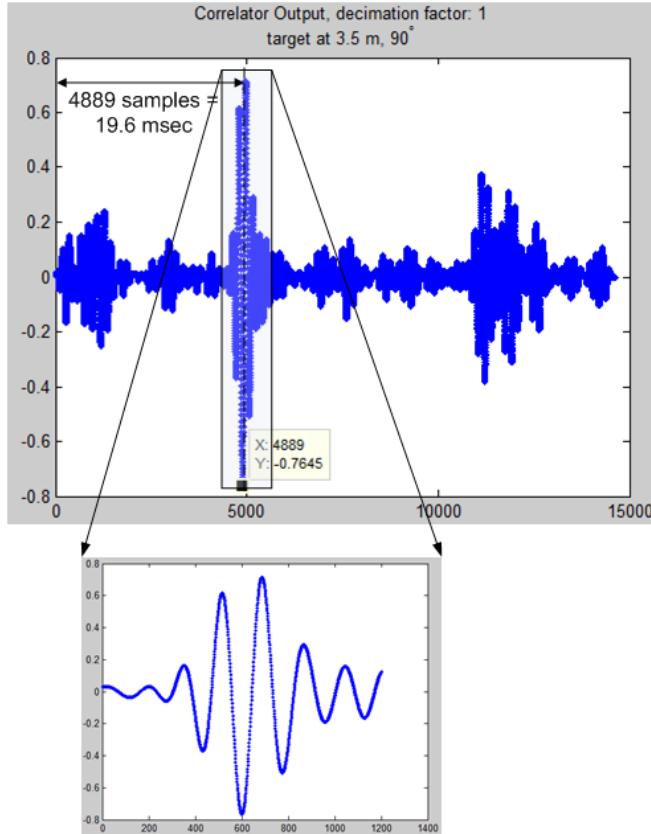

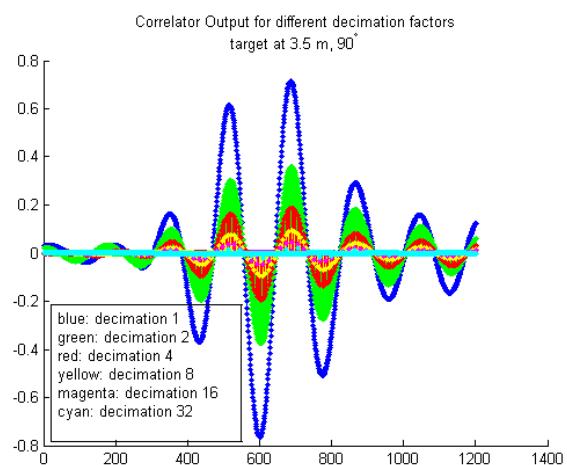

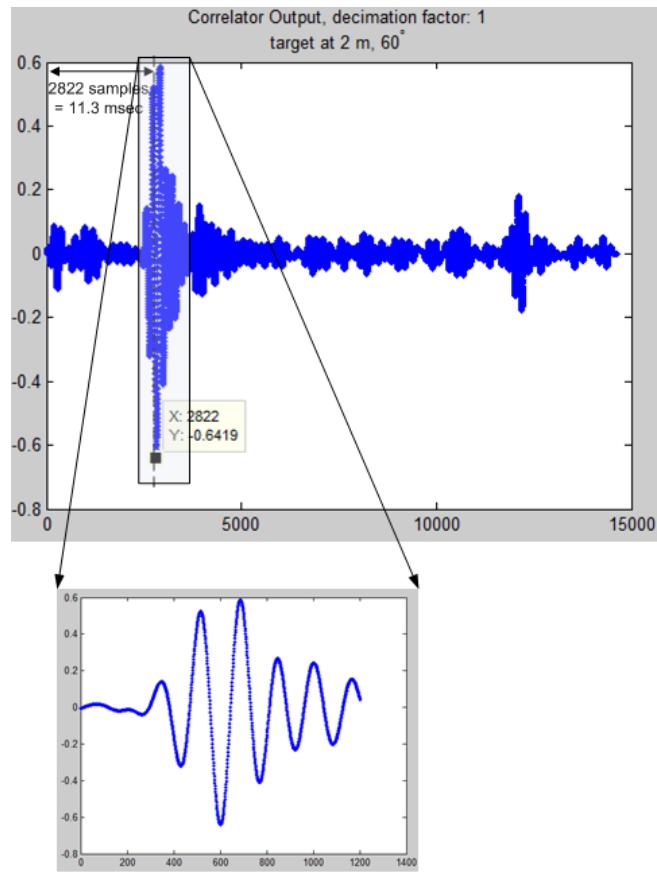

| Figure 5.21 Correlator Output, decimation factor: 1, target position: 3.5 m, 90° . . . . .                                                                     | 100 |

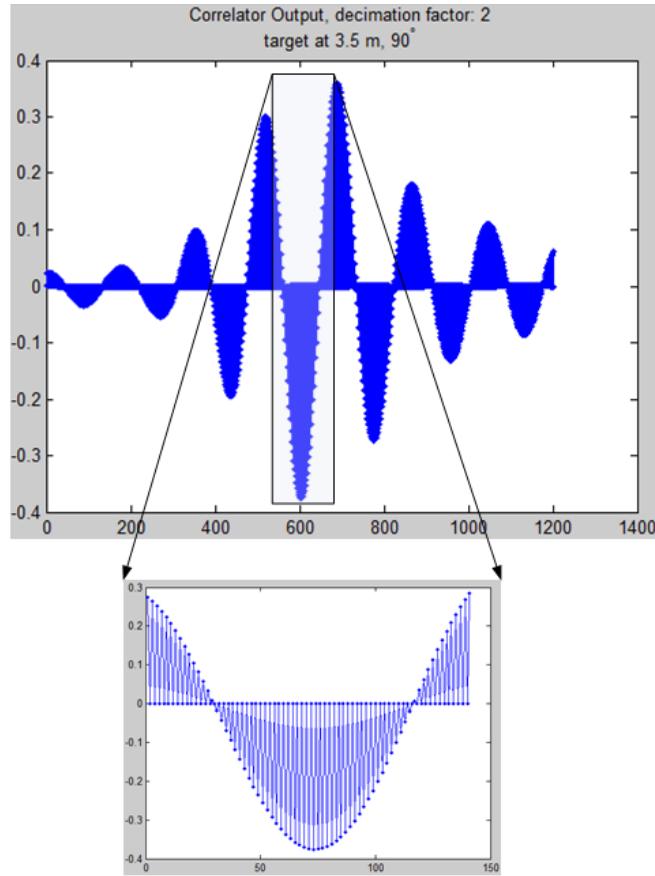

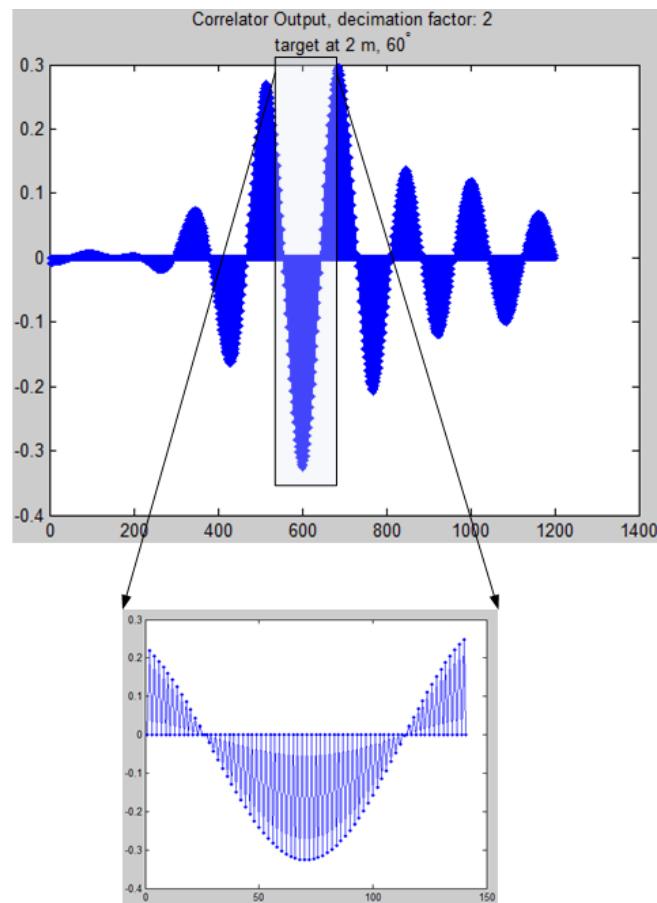

| Figure 5.22 Correlator Output, decimation factor: 2, target position: 3.5 m, 90° . . . . .                                                                     | 101 |

|                                                                                                                                                                                 |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

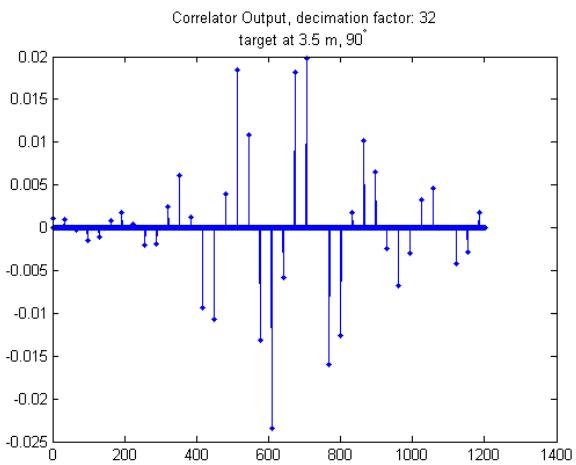

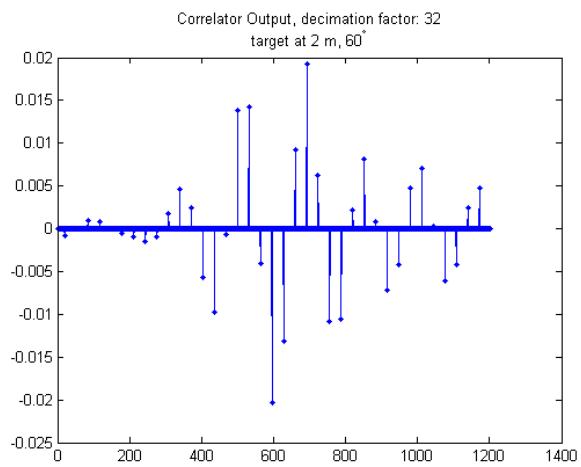

| Figure 5.23 Correlator Output, decimation factor: 32, target position: 3.5 m, 90° . . . . .                                                                                     | 102 |

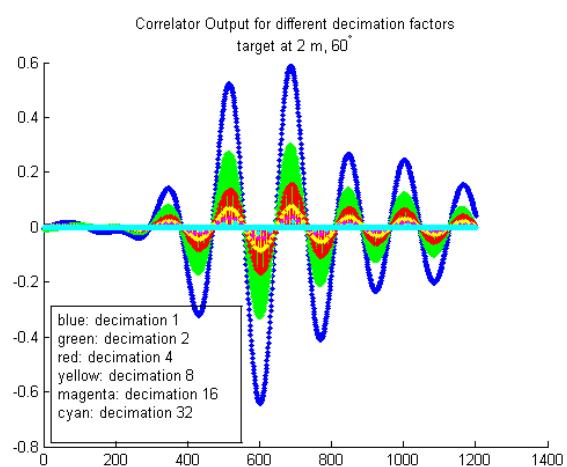

| Figure 5.24 Correlator Output for different values of <i>correlator decimation factor</i> pa-<br>rameter, target position: 3.5 m, 90° . . . . .                                 | 102 |

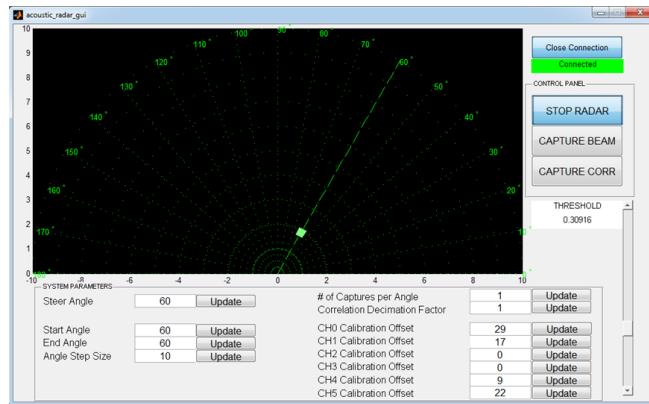

| Figure 5.25 Radar screenshot, target position: 3.5 m, 90° . . . . .                                                                                                             | 103 |

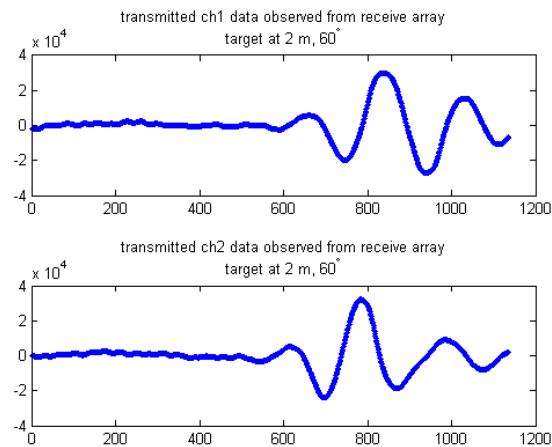

| Figure 5.26 Transmitted CH1 and CH2 waveforms from the receive array's point of<br>view, note the phase difference between channels, target position: 2 m, 60° . . . . .        | 104 |

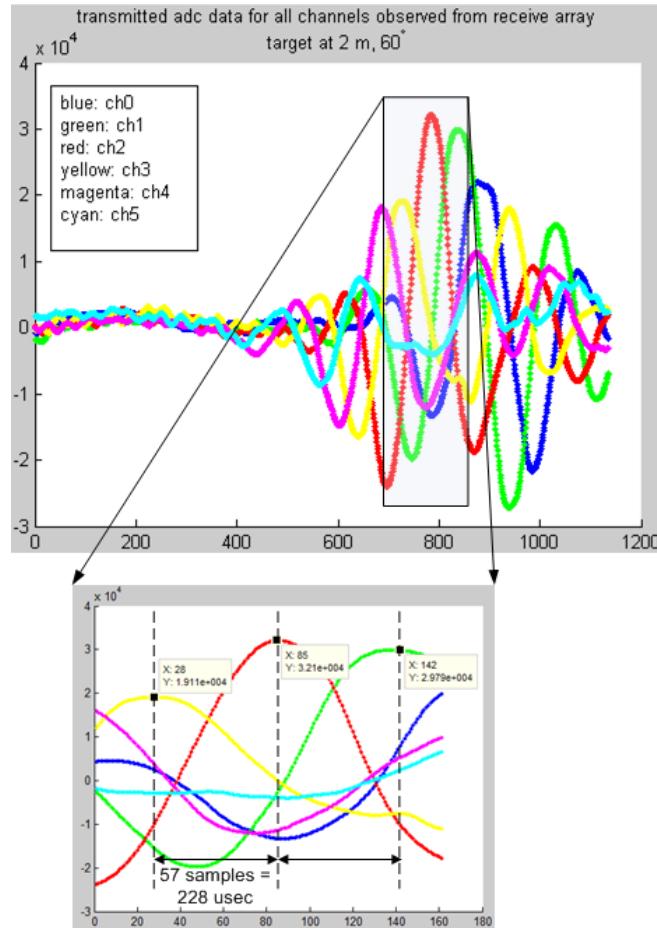

| Figure 5.27 Transmitted waveforms for all channels from the receive array's point of<br>view, note the phase difference between channels, target position: 3.5 m, 90° . . . . . | 105 |

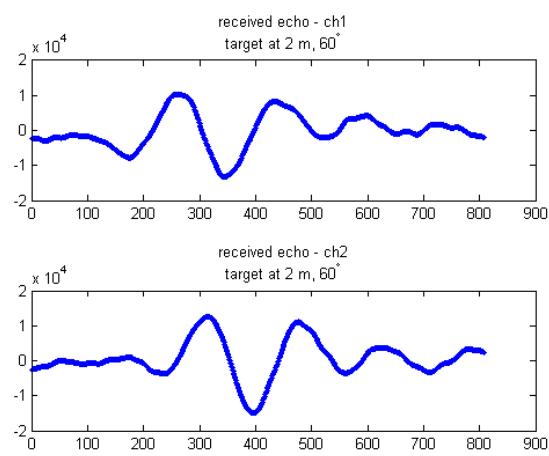

| Figure 5.28 Received echo from CH1 and CH2, note the phase difference, target posi-<br>tion: 2 m, 60° . . . . .                                                                 | 106 |

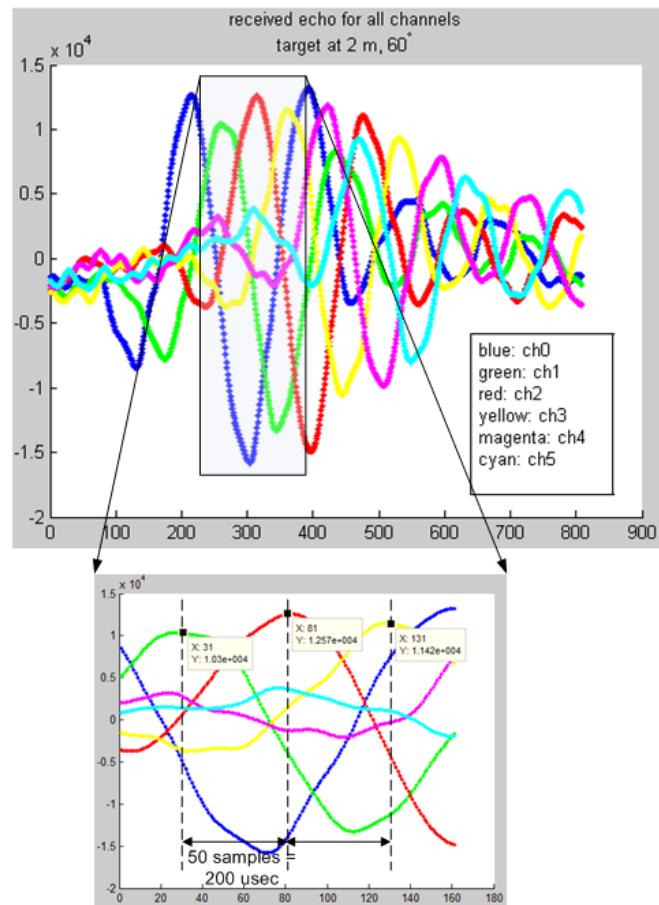

| Figure 5.29 Received echo from all channels, no phase difference observed, target po-<br>sition: 2 m, 60° . . . . .                                                             | 107 |

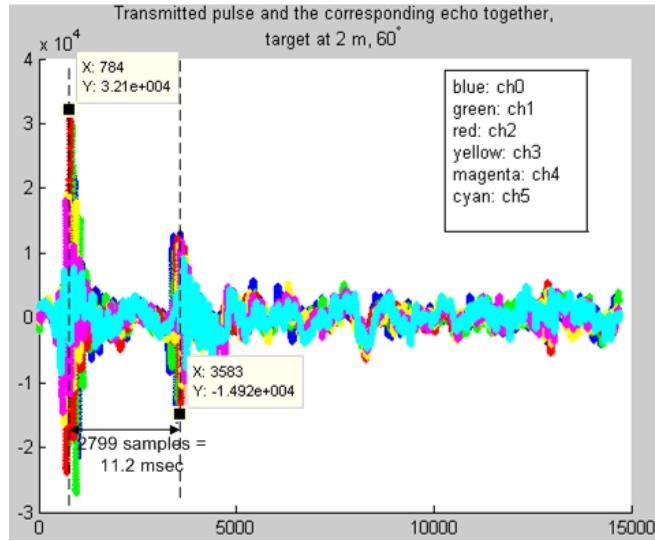

| Figure 5.30 Entire transmit-receive cycle captured, target position: 2 m, 60° . . . . .                                                                                         | 108 |

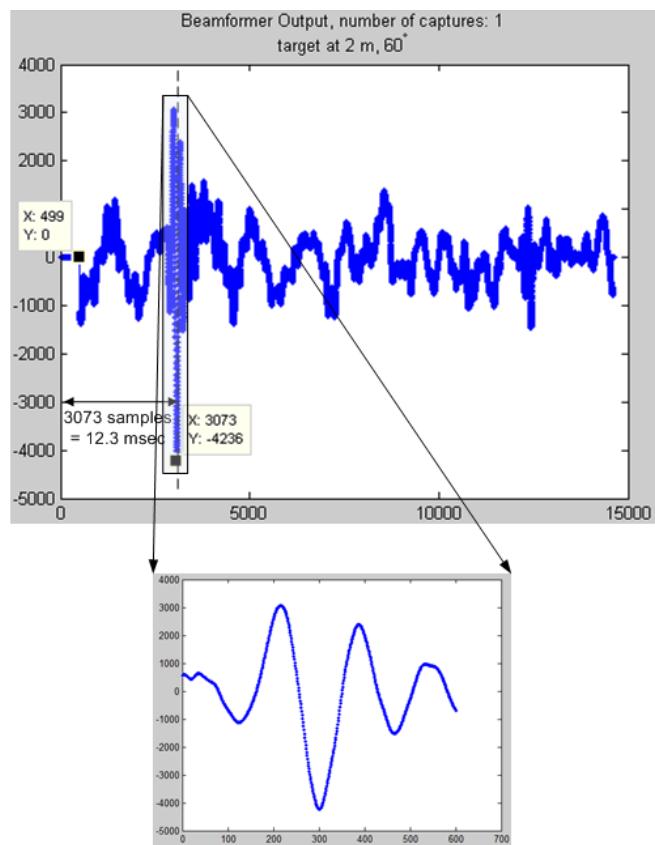

| Figure 5.31 Beamformer Output, number of captures: 1, target position: 2 m, 60° . . . . .                                                                                       | 109 |

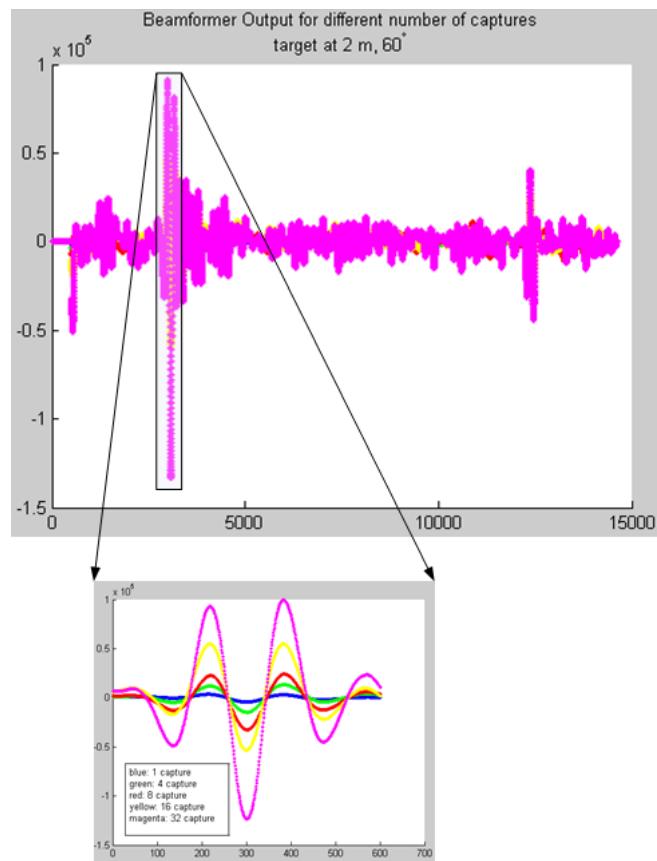

| Figure 5.32 Beamformer Output for different values of <i>number of captures per angle</i><br>parameter, target position: 2 m, 60° . . . . .                                     | 110 |

| Figure 5.33 Normalized beamformer outputs zoomed, <i>number of captures</i> parameter<br>varied, target position: 2 m, 60° . . . . .                                            | 110 |

| Figure 5.34 Correlator Output, decimation factor: 1, target position: 2 m, 60° . . . . .                                                                                        | 111 |

| Figure 5.35 Correlator Output, decimation factor: 2, target position: 2 m, 60° . . . . .                                                                                        | 112 |

| Figure 5.36 Correlator Output, decimation factor: 32, target position: 2 m, 60° . . . . .                                                                                       | 112 |

| Figure 5.37 Correlator Output for different values of <i>correlator decimation factor</i> pa-<br>rameter, target position: 2 m, 60° . . . . .                                   | 113 |

| Figure 5.38 Radar screenshot, target position: 2 m, 60° . . . . .                                                                                                               | 114 |

# CHAPTER 1

## INTRODUCTION

Phased array systems have a wide range of usage in fields such as radar, sonar, tomography and cellular communications [1]. The phased array systems mostly use antennas which operate with radio frequency waves, requiring expensive and technologically advanced equipment. A smaller and cheaper system may be designed and implemented using acoustic waves rather than electromagnetic waves, which may exactly illustrate the concepts of a phased array device. So, this work is concentrated on designing and implementing an acoustic phased array radar system. Together with the fact that it provides a simpler and cheaper test bed to examine the phased array radar behaviors, this work has also a significance in that phased array principles have not been extensively applied for acoustic imaging in air.

The history of acoustic radar applications goes back to the Acoustic Locators used in World War I [2]. They were used for passive detection of aircraft by picking up the noise of the engines. Upon the introduction of radar before and during World War II, which was obviously a more effective technique, those passive acoustic locators have become obsolete. But, there is still a wide application area of acoustic waves in air. In [3], a theoretical discussion about an atmospheric acoustical application, called SODAR, is given. SODAR (sonic detection and ranging) is a RADAR like system which, however, uses sound waves rather than radio waves to remotely measure the vertical turbulence structure and the wind profile of the lower layer of the atmosphere. Phased-array sodar systems, in which the beams are electronically steered by phasing the transducers appropriately as in our particular application, were developed in the United States during late 1980's and early 1990's by Xonics, Radian Corporation and AeroVironment. Another example for the acoustic radar applications is the travel aid devices which are used to improve the mobility of the visually impaired people [4]. The devices in [5], [6] are simplest examples as they do not scan the environment although they are both based on

array structure. As mentioned earlier, phased array principles have not been extensively used in air acoustical applications. In [7], an ultrasonic obstacle detector which uses the phased array principles is introduced. This application is still not a complete one as it only performs receive beamforming using a microphone array and has a single transducer for transmission. A more complete acoustic imaging application is given in [8], which is composed of two separate linear transmit and receive arrays. Transmit and receive arrays both use the phased beamforming technique to electronically sweep the acoustic beam.

In this thesis work, an acoustic radar system is implemented, which has separate transmit and receive arrays composed of six elements. Unlike [8] which employs ultrasound beams, the particular application uses acoustic sound waves which are generated by a 6 element loudspeaker transmit array. A 6 element microphone receive array is used for receive functioning. All signal processing algorithms are implemented in real-time on FPGA which allows fast operation with a 100 MHz clock frequency. The System performs a 2-dimensional scan from 0° to 180° with a resolution of 10°. The system is tested and verified under various scenarios. In CHAPTER 2, a background information is given, which is mainly based on array signal processing and beamforming. In CHAPTER 3, a conceptual structure of the system is given, the theoretical building blocks are described briefly. In CHAPTER 4, a detailed description of the implementation is given, the functionality and design details of each FPGA building block is explained. In CHAPTER 5, the implementation results, test and verification details are given. Chapter 6 is the conclusions part.

## CHAPTER 2

## BACKGROUND

In this chapter, the theoretical background which constitutes the base of the implemented acoustic radar system is given.

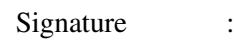

### 2.1 Array Signal Processing

Sensor arrays are used to spatially sample the space and extract both temporal and spatial parameters of signals. For a system which utilizes temporal information only, filter structures which are sensitive to certain frequencies are used. However, for a system which also needs spatial information, a direction sensitivity rather than frequency selection is needed. At this point, the concept of spatial filtering comes into the scene which is analogous to the temporal filtering in the sense that in spatial filtering, the filter is sensitive to the direction, i.e., passes signals from certain directions while rejecting those from other directions, while in temporal filtering, the discrimination is in the frequency content of the incoming signal. The spatial discrimination may be accomplished by a single sensor or an array of sensors as given in Figure 2.1. The spatial discrimination ability of a single sensor is dependent on the geometrical structure of the sensor. Also, in order to change the directivity pattern, i.e. the look direction of the sensor, a mechanical intervention must be applied. An array of sensors overcomes these disadvantages of a single sensor. The directivity pattern and look direction of a sensor array is not that dependent to the physical characteristics and may be altered by changing the phase delay in individual channels rather than moving the sensor array mechanically, which is a big advantage over the single sensor case.

Figure 2.1: Single antenna vs. array of antennas

### 2.1.1 Spatial Signals

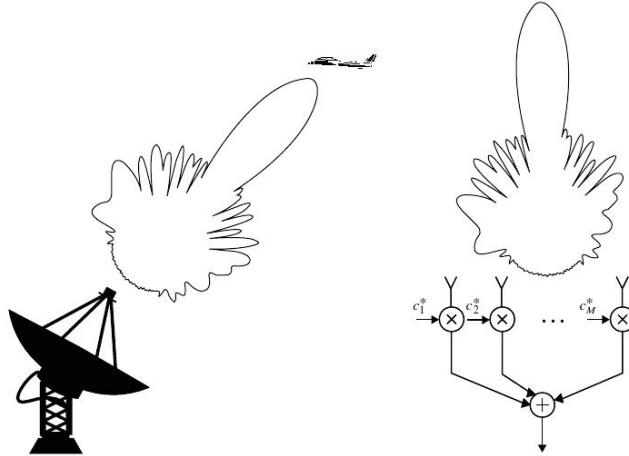

Spatial signals are waves propagating through space whose characteristics are defined by the wave equations. The spatial signal at a particular point specified by the vector  $\mathbf{r}$  may be represented either in Cartesian coordinates  $(x, y, z)$  or in spherical coordinates  $(R, \phi_{az}, \theta_{el})$  as in Figure 2.2, where  $R$  is the distance of wave from the origin,  $\phi_{az}$  is the azimuth angle and  $\theta_{el}$  is the elevation angle.

The spatial wave which is transmitted from a source located at  $\mathbf{r}_0$  may be represented as follows;

$$s(t, \mathbf{r}) = \frac{A}{\|\mathbf{r} - \mathbf{r}_0\|} e^{j2\pi f_c(t - \frac{\|\mathbf{r} - \mathbf{r}_0\|}{c})} \quad (2.1)$$

where  $A$  is the complex amplitude,  $f_c$  is the carrier frequency of the wave, and  $c$  is the speed of propagation of the wave, which is speed of sound in our case.

Figure 2.2: Three dimensional space in spherical coordinates

### 2.1.2 Near and Far Field Concept

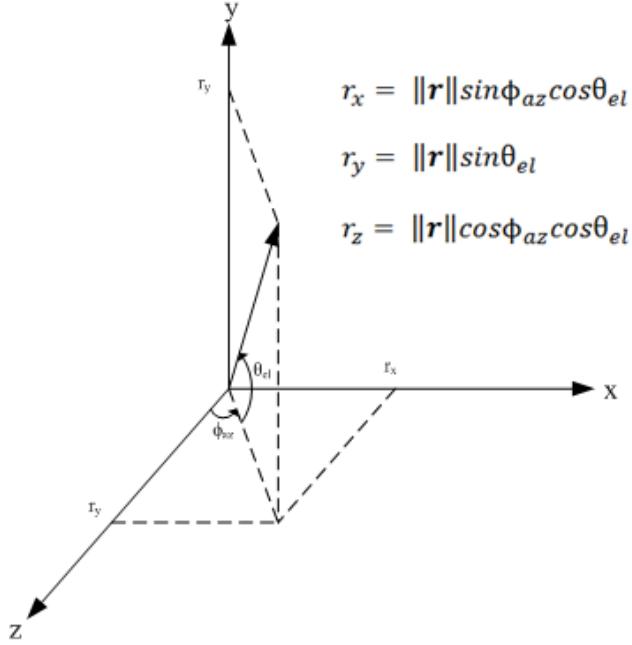

In array signal processing, far field approximation is important which simplifies the computations considerably. It relies on the assumption that if the transmitter is “very“ far away from the receiving array, and the array aperture is “relatively“ small, then the spherical wave front generated by the transmitter can be approximated as a plane wave.

In literature, usually, 3 regions are defined for the space surrounding an antenna, which are, reactive near field, radiating near field (Fresnel) and far-field (Fraunhofer) regions [9]. In the near field, the wave fronts are modeled as spherical. But, in the far field (or Fraunhofer) region, it is plausible to assume that the wave fronts are plane waves.

The far field assumption may be analysed as follows (consider the geometry given in Figure 2.3).  $\delta R$  is the distance between the spherical wavefront and the receiving array plane, which is

$$\delta R = \sqrt{R^2 + \left(\frac{D}{2}\right)^2} - R \quad (2.2)$$

Figure 2.3: A sensor array receiving the transmitted signal from a point source

where  $R$  is the distance between the receiving array and the point transmitter and  $D$  is the array aperture. Note that, in the far field,  $D \ll R$ , (2.2) may be approximated using the binomial expansion  $((x + 1)^{\frac{1}{2}} = 1 + \frac{x}{2} - \frac{x^2}{8} \dots)$  such that,

$$\begin{aligned} \delta R &= \left( \sqrt{1 + \left( \frac{D}{2R} \right)^2} - 1 \right) R = \\ &= \left[ 1 + \frac{\left( \frac{D}{2R} \right)^2}{2} - 1 \right] R = \frac{D^2}{8R} \end{aligned} \quad (2.3)$$

In literature [10], an array is assumed to be in the far-field if the distance  $\delta R$  is less than one sixteenth of the wavelength. Therefore, using the condition of  $\delta R \leq \frac{\lambda}{16}$ , (2.3) reduces to

$$\delta R = \frac{D^2}{8R} \leq \frac{\lambda}{16} \rightarrow R \geq \frac{2D^2}{\lambda} \quad (2.4)$$

(2.4) may further be simplified if the receiving array is an Uniform Linear Array (ULA) with  $L$  elements and the inter-element spacing is chosen as  $d = \frac{\lambda}{2}$  (which is the maximum distance satisfying the spatial sampling theorem, in other words, in order to prevent the spatial aliasing

[11]) such that

$$\begin{aligned}

D &= d(L-1) = \left(\frac{\lambda}{2}\right)(L-1) \\

R &\geq \left(\frac{2}{\lambda}\right) \left(\left(\frac{\lambda}{2}\right)(L-1)\right)^2 \\

R &\geq \frac{\lambda(L-1)^2}{2}

\end{aligned} \tag{2.5}$$

In our case, the wavelength  $\lambda = c/f = 346.13/1417 = 0.2443$  and number of array elements  $L = 6$ . So, the condition for far-field approximation in the particular application is  $R \geq 3.0538 \text{ m}$ .

### 2.1.3 Array Model Representation

In this part, a general array model will be established [12]. First, *single source* case will be considered, then, general array model for the multiple source case will be developed using superposition principle.

Consider the single source case in which only one waveform impinges upon the array. Let  $x(t)$  is the value of that source signal at some *reference point* at time  $t$ . The output of sensor  $k$  can be written as

$$\bar{y}_k(t) = \bar{h}_k(t) * x(t - \tau_k) + \bar{e}_k(t) \tag{2.6}$$

where  $\tau_k$  is the time needed for the wave to travel from the reference point to sensor  $k$ ,  $\bar{h}_k(t)$  is the impulse response of the  $k$ th sensor, “\*” is the convolution operation and  $\bar{e}_k(t)$  is the *additive noise*. In (2.6),  $\bar{h}_k(t)$  is assumed to be known. However,  $x(t)$  and  $\tau_k$  are unknown. The parameter which is intended to be estimated is  $\tau_k$ , because it has the information related to the location of the source. So, as the source signal  $x(t)$  is unknown, the problem is nothing but a *time delay estimation for the unknown input case*.

Equation (2.6) can be simplified significantly if the signals are assumed to be *narrowband*. Let  $X(\omega)$  be the fourier transform of  $x(t)$ ,

$$X(\omega) = \int_{-\infty}^{+\infty} x(t)e^{-i\omega t} dt \quad (2.7)$$

Similarly, let  $\bar{H}_k(\omega)$ ,  $\bar{Y}_k(\omega)$  and  $\bar{E}_k(\omega)$  be the fourier transforms of signals  $\bar{h}_k(t)$ ,  $\bar{y}_k(t)$  and  $\bar{e}_k(t)$ , respectively. So, in frequency domain, (2.6) is

$$\bar{Y}_k(\omega) = \bar{H}_k(\omega)X(\omega)e^{-i\omega\tau_k} + \bar{E}_k(\omega) \quad (2.8)$$

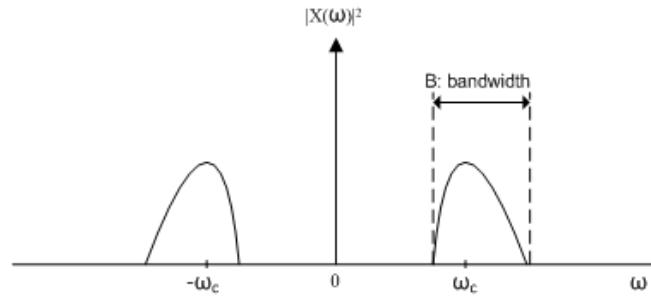

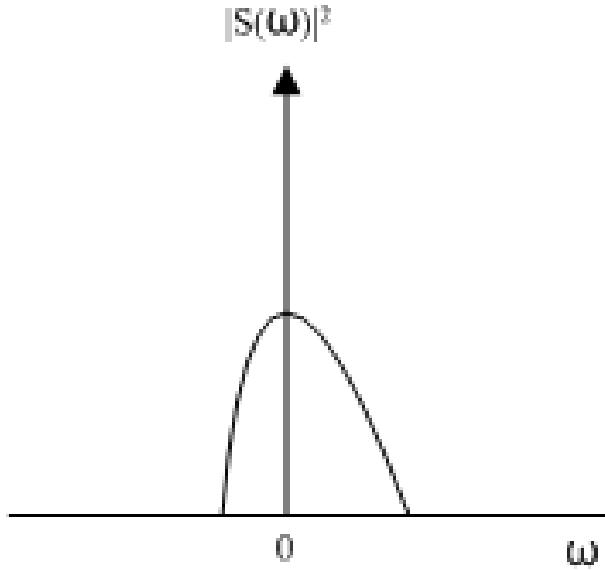

Generally in real systems,  $x(t)$  is a *bandpass signal*. It is obvious from Figure 2.4 that a bandpass is completely defined by its corresponding *lowpass signal*  $s(t)$ . The process of obtaining  $x(t)$  from  $s(t)$  is called *modulation* and the reverse process of obtaining  $s(t)$  from  $x(t)$  is called *demodulation*.

Figure 2.4: Energy spectrum of a bandpass signal

Figure 2.5: Lowpass equivalent of the bandpass signal whose spectrum is given in Figure 2.4

Modulation Process: The bandpass signal  $x(t)$  is obtained from the baseband signal  $s(t)$  via *modulation* process as mentioned above. Multiplying  $s(t)$  with  $e^{i\omega_c t}$  results in a shift of  $\omega_c$  in the spectrum, as expressed in (2.9).

$$\int_{-\infty}^{\infty} s(t)e^{i\omega_c t} e^{-i\omega t} d\omega = \int_{-\infty}^{\infty} s(t)e^{-i(\omega-\omega_c)} d\omega = S(\omega - \omega_c) \quad (2.9)$$

If  $x(t)$ , which is obtained from  $s(t)$  via modulation process, is a real valued signal, it must have an even spectrum. In such a case, in addition to the frequency shift  $\omega_c$  to the right, there is also a translation to the left of the folded and complex-conjugated baseband spectrum. So, the following expression for the modulated spectrum  $X(\omega)$  is obtained;

$$X(\omega) = S(\omega - \omega_c) + S^*(-(\omega + \omega_c)) \quad (2.10)$$

If (2.10) is transformed to the time domain, the following result is obtained:

$$\begin{aligned}

x(t) &= \frac{1}{2\pi} \int_{-\infty}^{\infty} [S(\omega - \omega_c) + S^*(-\omega - \omega_c)] e^{i\omega t} d\omega \\

&= \frac{1}{2\pi} \int_{-\infty}^{\infty} S(\omega - \omega_c) e^{i(\omega - \omega_c)t} e^{i\omega_c t} d\omega + \left[ \frac{1}{2\pi} \int_{-\infty}^{\infty} S(-\omega - \omega_c) e^{-i(\omega + \omega_c)t} e^{i\omega_c t} d\omega \right]^* \\

&= s(t) e^{i\omega_c t} + [s(t) e^{i\omega_c t}]^*

\end{aligned} \tag{2.11}$$

which gives

$$x(t) = 2Re[s(t) e^{i\omega_c t}] \tag{2.12}$$

or

$$x(t) = 2\alpha(t) \cos(\omega_c t + \varphi(t)) \tag{2.13}$$

where  $\alpha(t)$  and  $\varphi(t)$  are the amplitude and phase of  $s(t)$ , respectively;

$$s(t) = \alpha(t) e^{i\varphi(t)} \tag{2.14}$$

(2.12) can also be written in terms of real ( $s_I(t)$ ) and imaginary ( $s_Q(t)$ ) parts of  $s(t)$  as following;

$$x(t) = 2[s_I(t) \cos(\omega_c t) - s_Q(t) \sin(\omega_c t)] \tag{2.15}$$

Demodulation Process:  $s(t)$  is obtained from  $x(t)$  via demodulation process. First, the spectrum of  $x(t)$ , which is  $X(\omega)$  is translated left by  $\omega_c$ . Then, the resulting spectrum is low-pass filtered with a low-pass filter whose bandwidth is matched to that of  $S(\omega)$ . After the first step, the spectrum takes the form

$$[S(\omega) + S^*(-\omega - 2\omega_c)] \tag{2.16}$$

If this signal is low-pass filtered, the high frequency component vanishes and the resulting spectrum is nothing but that of the baseband signal, which is  $S(\omega)$ .

Now, let us return to our ultimate purpose of obtaining signal model. Consider (2.8), if  $X(\omega)$  given in (2.10) is inserted in (2.8);

$$\bar{Y}_k(\omega) = \bar{H}_k(\omega)[S(\omega - \omega_c) + S^*(-\omega - \omega_c)]e^{i\omega\tau_k} + \bar{E}_k(\omega) \quad (2.17)$$

Let  $\tilde{y}_k(t)$  be the demodulated signal, i.e.

$$\tilde{y}_k(t) = \bar{y}_k(t)e^{-i\omega_c t} \quad (2.18)$$

The Fourier transform of  $\tilde{y}_k(t)$  can be expressed as:

$$\tilde{Y}_k(\omega) = \bar{H}_k(\omega + \omega_c)[S(\omega) + S^*(-\omega - 2\omega_c)]e^{-i(\omega + \omega_c)\tau_k} + \bar{E}_k(\omega + \omega_c) \quad (2.19)$$

When  $\tilde{y}_k(t)$  is low-pass filtered, the high frequency component in (2.19), which is  $S^*(-\omega - 2\omega_c)$  is eliminated and the resulting signal is

$$Y_k(\omega) = H_k(\omega + \omega_c)S(\omega)e^{-i(\omega + \omega_c)\tau_k} + E_k(\omega + \omega_c) \quad (2.20)$$

If the received signals are *narrowband*, i.e.  $|S(\omega)|$  decreases rapidly with increasing  $|\omega|$ , (2.20) can be approximated as

$$Y_k(\omega) = H_k(\omega_c)S(\omega)e^{-i\omega_c\tau_k} + E_k(\omega + \omega_c) \text{ for } \omega \in \Omega \quad (2.21)$$

where  $\Omega$  is the lowpass filter's passband. Further assuming that the frequency response of the sensor is flat over the passband  $\Omega$ , the time domain counterpart of 2.21 would be the following:

$$y_k(t) = H_k(\omega_c)e^{-i\omega_c\tau_k}s(t) + e_k(t) \quad (2.22)$$

where  $y_k(t)$  and  $e_k(t)$  are the inverse Fourier transforms of the terms  $Y_k(\omega)$  and  $E_k(\omega + \omega_c)$ , respectively. Now, let us introduce the *array transfer vector*:

$$a(\theta) = [H_1(\omega_c)e^{-i\omega_c\tau_1} \dots H_m(\omega_c)e^{-i\omega_c\tau_m}] \quad (2.23)$$

By making use of (2.23), (2.22) can be rewritten as

$$\begin{aligned} y(t) &= a(\theta)s(t) + e(t) \\ &\text{where} \\ y(t) &= [y_1(t) \dots y_m(t)]^T \\ e(t) &= [e_1(t) \dots e_m(t)]^T \end{aligned} \quad (2.24)$$

The dependency of the *array transfer vector* on sensor responses, which are shown as  $H_i(\omega_c)$  may be ignored if the sensor responses are independent of the direction of arrival. So, with this assumption, (2.23) reduces to

$$a(\theta) = [1 \ e^{-i\omega_c\tau_2} \dots e^{-i\omega_c\tau_m}] \quad (2.25)$$

Note that the array model given in (2.24) is for single channel. Extension of this model to multiple source case is straightforward. Using superposition principle, the following model is obtained,

$$y(t) = [a(\theta_1) \dots a(\theta_n)] \begin{bmatrix} s_1(t) \\ \dots \\ s_n(t) \end{bmatrix} + e(t) \triangleq As(t) + e(t) \quad (2.26)$$

$\theta_k$  = the DOA of the  $k^{\text{th}}$  source

$s_k(t)$  = the signal corresponding to the  $k^{\text{th}}$  source

Note that the array model in (2.26) is developed for *narrowband* signals. But, as explained in Section 3.1.7.5, for our particular acoustic radar application, the narrowband assumption does not hold. In other words, (2.20) cannot be approximated by (2.21) in our case. So, wideband

methods must be used. Wideband signals can be decomposed into many narrowband signals using filter banks or the discrete time Fourier transform along temporal domain, picking the frequencies with the highest power. After this decomposition, narrowbands methods can be applied to each of these narrowband components. The disadvantage of this kind of approach is not taking full advantage of the signal's frequency band. Because, some frequency bins which might have information about the direction of arrival is discarded. As well as frequency domain approaches, some time domain methods can be used to deal with wideband signals. *Delay and Sum Beamforming*, which is used in the acoustic radar system, is one of these methods.

## 2.2 Array Beamforming

A beamformer may be defined as a spatial filter which discriminates signals depending on the direction of arrival in such a way that it maximizes the SNR in the direction of interest [13]. A beamformer may be used both for reception and transmission (beam steering, [14]) of signals, as in the particular acoustic radar implementation. Let's rewrite the signal model developed in the previous section here for a receiving array of L elements;

$$\begin{aligned}

y_i(t) &= \alpha_i s(t - T_0 - \tau_i) + e_i(t) \\

&= x_i(t) + e_i(t)

\end{aligned} \tag{2.27}$$

where  $i = 1, 2, \dots, L$

Where  $\alpha_i$  is the attenuation factor due to propagation  $\alpha_i \in [0, 1]$ ,  $s(t)$  is the unknown signal, which may be narrowband or wideband,  $T_0$  is the time required for the signal to propagate from the source to the 1<sup>th</sup> array element which is the reference sensor,  $e_i(t)$  is the additive noise at the  $i^{\text{th}}$  sensor,  $\tau_i$  is the relative delay between the reference sensor and  $i^{\text{th}}$  sensor.

From now on, it will be assumed that TDOA (Time Difference of Arrival), which is nothing but the time required for the signal to travel between adjacent array elements, is known (which is actually the case for the particular acoustic radar implementation; because, the direction of arrival angle of the incoming or expected echo is known *a priori*). Also, it is assumed that channel noise signals are uncorrelated.

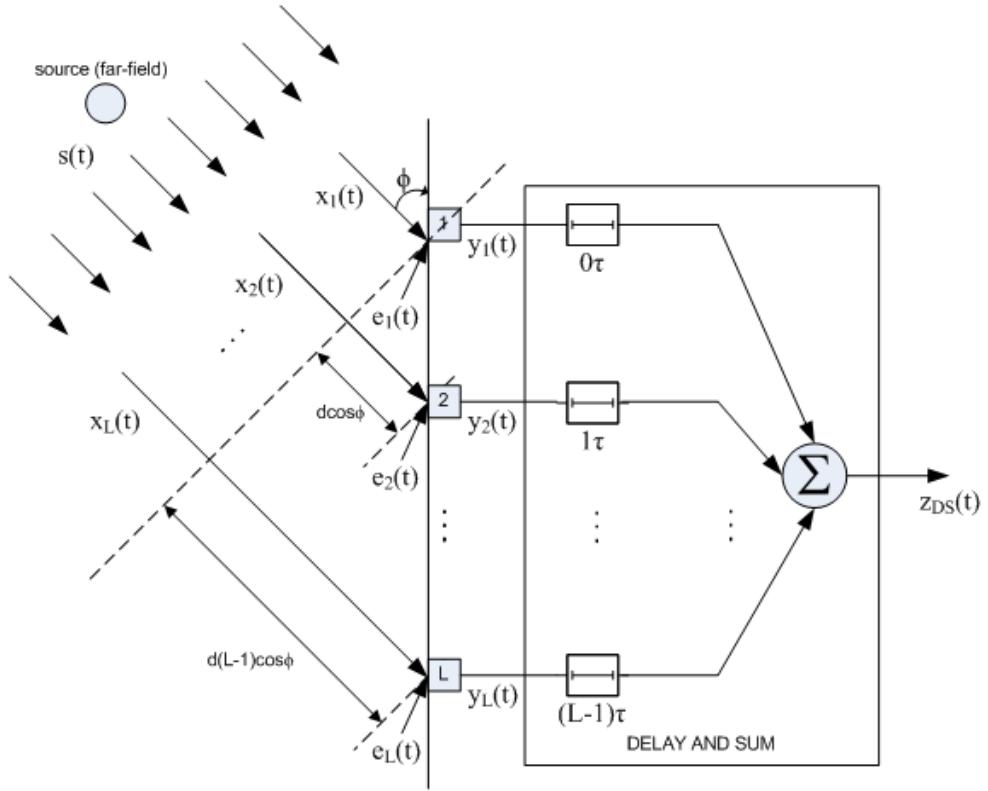

### 2.2.1 Delay and Sum Technique

A simple beamformer, called “Delay and Sum Beamformer“ accomplishes the spatial filtering task via - as the name suggests - summing the sensor outputs after a particular delay [15]. The first step of Delay-and-Sum beamforming is time-shifting each sensor signal by a value corresponding to the TDOA between that sensor and the reference one

$$\begin{aligned}

y_{a,i} &= y_i(t + \tau_i) \\

&= \alpha_i s(t - T_0) + e_{a,i}(t) \\

&= x_{a,i}(t) + e_{a,i}(t), \quad i = 1, 2, \dots, L

\end{aligned} \tag{2.28}$$

where  $e_{a,i} = e_i(t + \tau_i)$ . The next step is just adding up these time-shifted sensor outputs, which results in

$$\begin{aligned}

z(t) &= \frac{1}{L} \sum_{i=1}^L y_{a,i}(t) \\

&= \alpha_s s(t - T_0) + \frac{1}{L} e_s(t) \\

&\text{where } \alpha_s = \frac{1}{L} \sum_{i=1}^L \alpha_i \\

e_s(t) &= \sum_{i=1}^L e_{a,i}(t) \\

&= \sum_{i=1}^L e_i(t + \tau_i)

\end{aligned} \tag{2.29}$$

The input SNR, based on the model given in (2.27) of the receiving array is (relative to the  $i^{th}$  signal),

$$SNR_i = \frac{\sigma_{x_i}^2}{\sigma_{e_i}^2} = \alpha_i^2 \frac{\sigma_s^2}{\sigma_{e_i}^2} \tag{2.30}$$

where  $\sigma_{x_i}^2 = E[x_i^2]$ ,  $\sigma_{e_i}^2 = E[e_i^2]$ , and  $\sigma_s^2 = E[s^2(t)]$  are the variance of the signals  $x_i(t)$ ,  $e_i(t)$  and  $s(t)$  respectively.

After Delay-and-Sum processing, the SNR can be expressed as the ratio of the variances of the first and second terms in the right hand side of (2.29):

$$\begin{aligned}

SNR_{out} &= L^2 \alpha_s^2 \frac{E[s^2(t - T_0)]}{E[e_s^2]} = L^2 \alpha_s^2 \frac{\sigma_s^2}{\sigma_{e_s}^2} \\

&= \left( \sum_{i=1}^L \alpha_i \right)^2 \frac{\sigma_s^2}{\sigma_{e_s}^2}, \\

\text{where } \sigma_{e_s}^2 &= E \left\{ \left[ \sum_{i=1}^L e_i [t + \tau_i] \right]^2 \right\} \\

&= \sum_{i=1}^L \sigma_{e_i}^2 + 2 \sum_{i=1}^{L-1} \sum_{j=i+1}^L \varsigma_{e_i e_j},

\end{aligned} \tag{2.31}$$

with  $\sigma_{e_i}^2 = E[e_i^2]$  is the variance of the noise signal  $e_i(t)$  and  $\varsigma_{e_i e_j} = E\{e_i [t + \tau_i] e_j [t + \tau_j]\}$  is the cross-correlation between  $e_i(t)$  and  $e_j(t)$

The beamformer is regarded as successful if the condition

$$SNR_{out} > SNR_i \tag{2.32}$$

is satisfied

*1st particular case :* Assume that noise signals at the elements of receiving array are uncorrelated, i.e.  $\varsigma_{e_i e_j} = 0, \forall i, j = 1, 2, \dots, L, i \neq j$  and they all have the same variance, i.e.  $\sigma_{e_{i_1}}^2 = \sigma_{e_{i_2}}^2 = \dots = \sigma_{e_{i_L}}^2$ . And also assume that all the attenuation factors are equal to 1, i.e.  $\alpha_i = 1, \forall i$ . Then

$$SNR_{out} = N \times SNR_i \tag{2.33}$$

So, it is interesting that under the particular condition, simply delaying and summing the sensor outputs results in an SNR improvement by a factor equal to the number of sensors.

*2nd Particular Case :* Here, an assumption which is more restrictive than the 1<sup>st</sup> one will be made. Assume that the noise signals have the same energy (they may be correlated), and all the attenuation factors are 1 as in the 1<sup>st</sup> case. In this case;

$$\begin{aligned}

SNR_{out} &= \frac{L}{1 + \rho_s} \times SNR_i \\

\text{where } \rho_s &= \frac{2}{L} \sum_{i=1}^{L-1} \sum_{j=i+1}^L \rho_{e_i e_j}, \\

\rho_{e_i e_j} &= \frac{S_{e_i e_j}}{\sigma_{e_i} \sigma_{e_j}}

\end{aligned} \tag{2.34}$$

$\rho_{e_i e_j}$  is the correlation coefficient with  $|\rho_{e_i e_j}| \leq 1$ . If the noise signals are completely correlated, i.e. if the correlation coefficient  $\rho_{e_i e_j} = 1$ , then  $SNR_{out} = SNR_i$ , so no gain is possible with delay-and-sum technique in this condition. Until this point, the performance of the beamformer is investigated in terms of SNR improvement. Another way of illustrating the performance is through examining the beam pattern (or directivity pattern or spatial pattern). Note that the Delay-and-Sum Beamformer is actually an L-point spatial filter and its beam pattern is defined as the magnitude of the spatial filter's directional response. Now, consider the Uniform Linear Array in Figure 2.6, TDOA between the  $i^{th}$  and the reference sensors is

$$\tau_i = \frac{(i-1)d\cos(\phi)}{c} \tag{2.35}$$

For the Uniform Linear Array case, the directional response of the DS filter can be expressed as

$$\begin{aligned}

S_{DS}(\psi, \phi) &= \frac{1}{L} \sum_{i=1}^L \left[ e^{\frac{j2\pi(i-1)fd\cos\theta}{c}} \right] e^{-\frac{j2\pi(i-1)fd\cos\psi}{c}} \\

&= \frac{1}{L} \sum_{i=1}^L e^{-\frac{j2\pi(i-1)fd[\cos\psi - \cos\phi]}{c}}

\end{aligned} \tag{2.36}$$

where  $\psi$  ( $0 \leq \psi \leq \pi$ ) is a directional angle. The beam pattern is then written as

$$\begin{aligned}

A_{DS}(\psi, \phi) &= |S_{DS}(\psi, \phi)| \\

&= \left| \frac{\sin [L\pi fd(\cos\psi - \cos\phi) / c]}{L \sin [\pi fd(\cos\psi - \cos\phi) / c]} \right|

\end{aligned} \tag{2.37}$$

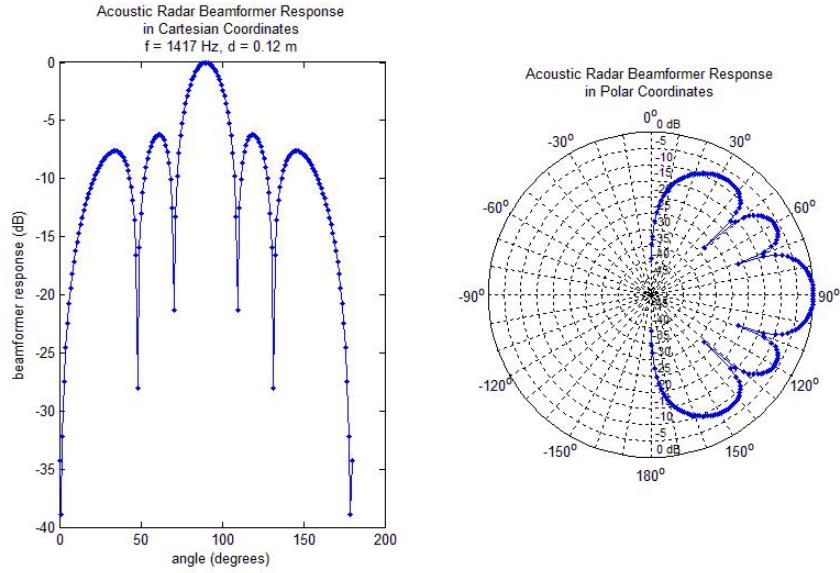

For the implemented acoustic radar system, the beamformer response is given in Figure 2.7, with the pulse frequency  $f$  is chosen as 1417 Hz and the inter-element spacing of both trans-

Figure 2.6: ULA Delay-and-Sum Beamforming

mit and receive array is chosen as 12 cm (the reason why these values are chosen will be explained).

Consider Figure 2.7. The beam which has the highest amplitude is called mainlobe, all the others are sidelobes. An important parameter for a beamformer design is defined as beamwidth, which is the region between first zero-crosses on either side of the mainlobe. Beamwidth can easily be calculated considering (2.37). Equating the numerator to zero (with the steer angle  $\phi$  is chosen as  $90^\circ$ ), the angle at which beamformer response becomes zero can be easily calculated such that;

Figure 2.7: Directivity response of the Acoustic Radar Beamformer with steer angle chosen as  $90^\circ$  (Same for transmit and receive arrays)

$$\begin{aligned}

\sin [L\pi f d (\cos\psi - \cos\phi) / c] &= 0 \rightarrow \\

\frac{L\pi f d \cos\psi}{c} &= \pi \rightarrow \\

\psi &= \cos^{-1} \frac{c}{L f d}

\end{aligned} \tag{2.38}$$

note that beamwidth =  $2 \times \psi \rightarrow$

$$\text{beamwidth} = 2 \cos^{-1} \frac{c}{L f d}$$

Obviously, the performance of a beamformer with a narrower beamwidth is considered as good. Beamwidth decreases as the inter-element spacing  $d$  increases and the frequency of the transmitted/received signal is increased. It should be noted that there is a limit on the inter-element spacing. One would like to increase  $d$  as large as possible to get a narrower beamwidth and more noise reduction. But, when  $d$  is larger than  $\lambda/2 = c/2f$ , where  $\lambda$  is the wavelength of the signal, spatial aliasing would arise. So, there is a trade-off between  $d$ ,  $f$  and the beamwidth of the beamformer. In order to avoid spatial aliasing, the condition  $d \leq \lambda/2 = c/2f$  must be satisfied. In the particular implementation, the maximum possible frequency satisfying the Spatial Sampling Theorem (i.e. not causing spatial aliasing) is 1417 Hz. It is achieved by minimizing the inter-element spacing  $d$ , which is, by physical constraints

of the loudspeaker array elements, chosen as 12 cm.

### 2.2.2 Designing the Maximum SNR Spatial Filter [15]

In this section, the optimal spatial filter which maximizes the SNR at the output of the beamformer is [15] presented.

Equation (2.28) may be rewritten in vector form as;

$$\begin{aligned} \mathbf{y}_a(k) &= s(t - T_0)\boldsymbol{\alpha} + \mathbf{e}_a(t) \\ \text{where } \mathbf{y}_a(t) &= [y_{a,1}(t) \ y_{a,2}(t) \ \dots \ y_{a,L}(t)]^T, \\ \mathbf{e}_a(t) &= [e_{a,1}(t) \ e_{a,2}(t) \ \dots \ e_{a,L}(t)]^T, \\ \boldsymbol{\alpha} &= [\alpha_1 \ \alpha_2 \ \dots \ \alpha_L]^T \end{aligned} \quad (2.39)$$

where the subscript “a“ is used to indicate that the corresponding signal is “delayed“ (in (2.28), this was also indicated by “a“ subscript). Under the assumption that the signal and noise are uncorrelated, the correlation matrix of  $\mathbf{y}_a(t)$  can be expressed as

$$\mathbf{R}_{y_a y_a} = \sigma_s^2 \boldsymbol{\alpha} \boldsymbol{\alpha}^T + \mathbf{R}_{e_a e_a} \quad (2.40)$$

where  $\mathbf{R}_{e_a e_a} = E[\mathbf{e}_a(t) \mathbf{e}_a^T(t)]$  is the noise correlation matrix. Note that in a simple Delay-and-Sum beamformer, the time-shifted sensor outputs are simply summed. But, in a more general beamformer, the time-shifted outputs are weighted before summation, this may be expressed as;

$$\begin{aligned} z(t) &= \mathbf{h}^T \mathbf{y}_a(t) \\ &= \sum_{i=1}^L h_i y_{a,i}(t) \\ &= s(t - T_0) \mathbf{h}^T \boldsymbol{\alpha} + \mathbf{h}^T \mathbf{e}_a(t) \\ \text{where } \mathbf{h} &= [h_1 \ h_2 \ \dots \ h_L]^T \end{aligned} \quad (2.41)$$

Delay-and-Sum beamformer is a special case of this filter where  $h_n$ ‘s are taken as  $1/N$ , i.e. no

weighting is employed, time-delayed signals are simply summed in Delay-and-Sum beamformer). Using (2.41), the output SNR may be written as

$$SNR(\mathbf{h}) = \frac{\sigma_s^2 (\mathbf{h}^T \boldsymbol{\alpha})^2}{\mathbf{h}^T \mathbf{R}_{e_a e_a} \mathbf{h}} \quad (2.42)$$

Maximizing the SNR at the output of the beamformer is equivalent to solving the following eigenvalue problem:

$$\sigma_s^2 \boldsymbol{\alpha} \boldsymbol{\alpha}^T \mathbf{h} = \lambda \mathbf{R}_{e_a e_a} \mathbf{h} \quad (2.43)$$

Assuming that  $\mathbf{R}_{e_a e_a}^{-1}$  exist, the optimal solution to the above eigenvalue problem is the eigenvector,  $\mathbf{h}_{max}$  corresponding to the maximum eigenvalue,  $\lambda_{max}$  of  $\sigma_s^2 \mathbf{R}_{e_a e_a}^{-1} \boldsymbol{\alpha} \boldsymbol{\alpha}^T$  so;

$$\begin{aligned} z_{max}(t) &= \mathbf{h}_{max}^T \mathbf{y}_d(t), \\ SNR(\mathbf{h}_{max}) &= \lambda_{max} \end{aligned} \quad (2.44)$$

Now, remember the *1st particular case* examined in 2.2.1, in which noise signals are uncorrelated, they all have the same variance and the attenuation factors ( $\sigma_i$ 's) are all 1. Then, for this particular case, (2.44) becomes

$$SNR \cdot \boldsymbol{\alpha} \boldsymbol{\alpha}^T \mathbf{h}_{max} = \lambda_{max} \mathbf{h}_{max} \quad (2.45)$$

Left multiplying both sides by  $\boldsymbol{\alpha}^T$ ,

$$\begin{aligned} \lambda_{max} &= N \cdot SNR_i \text{ so that,} \\ SNR_i(\mathbf{h}_{max}) &= N \cdot SNR_i = SNR_{out} \end{aligned} \quad (2.46)$$

This implies that

$$\mathbf{h}_{max} = \frac{1}{N} [1 \ 1 \ \dots \ 1]^T \quad (2.47)$$

So, for the 1<sup>th</sup> particular case given in section 2.2.1, which is also the assumption in this Acoustic Radar Implementation, the maximum SNR filter is identical to the Delay-and-Sum beamformer.

# CHAPTER 3

## ACOUSTIC RADAR

In this chapter, a general description of the acoustic radar system is given. The detailed technical description of the implemented Acoustic Radar System is given in CHAPTER 4.

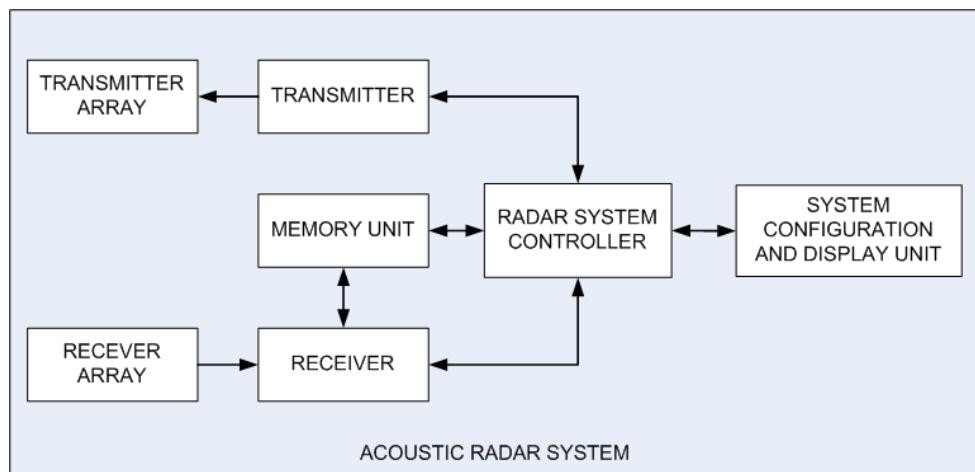

### 3.1 System Structure

The basic structure of the implemented acoustic radar system is given below in Figure 3.1. The diagram shows a conceptual structure, rather than a functional block diagram of the FPGA implementation (the functional block diagram of the implementation is given in the following chapter).

Figure 3.1: Acoustic Radar System Structure

### 3.1.1 Radar System Controller

Radar system controller is the main processor of the system which is responsible for operating the whole system synchronously and organizing the data flow throughout the system. Its operation is managed by a finite state machine which provides the control of the system for standalone operation.

The functionality of the controller may be described briefly as follows: First, the controller gives instruction to the transmitter unit for generation of a pulse which is to be sent to air ultimately from the transmit array. To generate pulses for the transmit array elements, the only information that the transmitter unit needs is the steer angle. So, the only action that radar system controller takes to send a pulse to air is just triggering the transmitter unit with the desired steer angle information. Acoustic Radar System has a scan ability in range [0, 180] degrees with a resolution of 1 degrees. However, in practice, a coarse scan step is selected since the array beamwidth is large. After triggering the transmit pulse generation with a particular steer angle request, acoustic radar system controller runs the receive unit which consists of a delay-sum beamformer and a correlator unit. Upon triggering receiver unit, system controller waits until correlator finishes its operation. Correlator provides the radar information to the system controller, which are namely;

- the **index** of the correlation maximum, which is directly related to the fly time of the radar pulse in the air

- the **value** of the correlation maximum, which is directly related to reflectivity quality of the scanned object

Upon gathering this information from correlator, acoustic radar system controller sends it to Display Unit (together with current steer angle information attached) which is ultimately to be displayed on the Radar Screen. After the position information of a particular look direction is plotted on the radar screen, the Display Unit sends a feedback signal to System Controller with which it is triggered to scan the next steer angle.

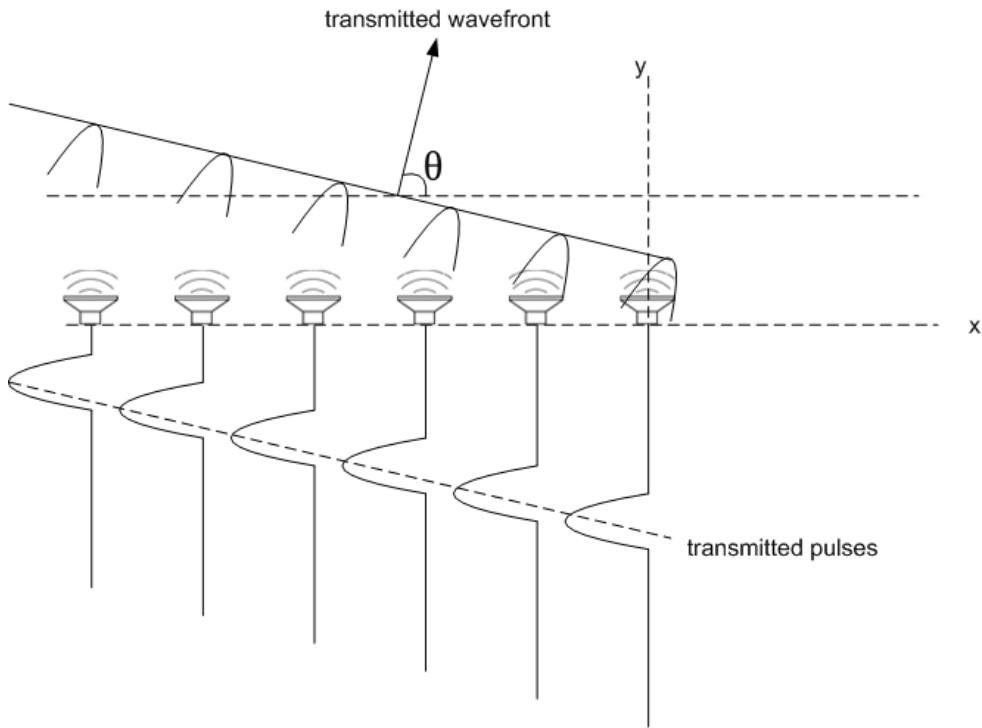

### 3.1.2 Transmitter

Transmitter block is mainly responsible for generating the transmit pulse. This block is a slave unit which is controlled by the main controller of the system, namely the “Radar System Controller“.

The main controller of the system does not deal with the details of the pulse generation process, i.e., all the necessary steps for transmit beam steering is handled by the Transmitter block. This unit implements transmit beam steering digitally [14]. Transmit beam steering is similar to the receive beamforming which is explained in 2.2.1. The difference is that in delay-sum receive beamforming, the received waves are summed together after passing them through proper delays, however, in transmit beam steering, the reverse process applies, namely, the waves are transmitted to the air after passing them through very same delays as in the receive case. How transmit beam steering is achieved is illustrated in Figure 3.2. Note from the figure that feeding the transmit array elements with signals having phase differences causes the transmitted wavefront to be directed to a particular direction.

Figure 3.2: Phased Array Transmit Steer

### 3.1.3 Receiver

This block is responsible to receive the expected acoustic echo pulses from the air (which are captured by the receive array elements, i.e. the microphones) and then to apply matched-filtering after receive delay-and-sum beamforming. This block, just like the Transmitter, is controlled by the main system controller, i.e. Radar System Controller.

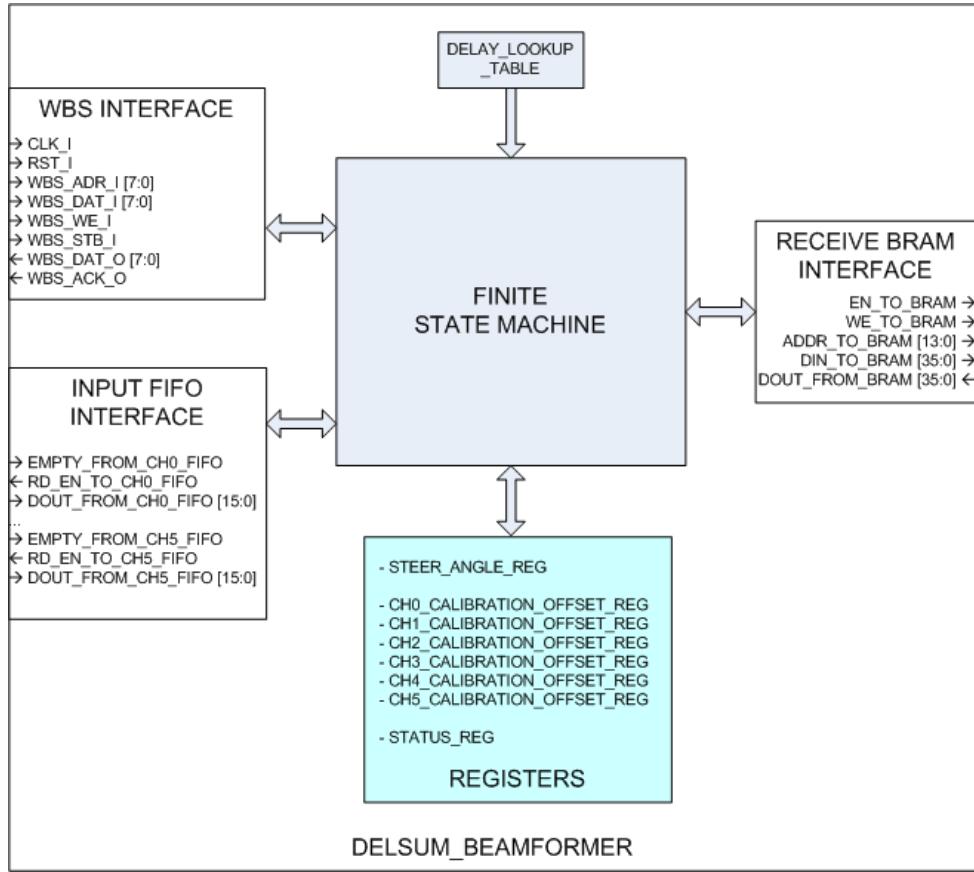

The receiver block mainly consists of three parts, data capture and filtering part, delay-and-sum beamforming part and correlator part. Data capture and filtering part operates independently from the System Controller, it continuously captures data from 6-Channel ADC - with a sampling rate of 250 MSPS for each channel-, removes the DC present in the signal, low-pass filters it and ultimately dumps the filtered data to 6 input channel FIFOs for further processing. The other two fundamental units of the receiver, namely delay-and-sum beamformer and correlator units, are run by the System Controller. The process is as follows: at first, the 6 channel FIFOs mentioned above are held on reset by the System Controller, so write accesses of the data capture and filtering part to these FIFOs are simply ignored. Then, the reset of the FIFOs is released, at the same time delay-and-sum beamformer part is triggered with the current steer angle information. Delay-and-sum beamformer starts its operation, it sums 6 channel data with the proper delays applied to each channel and writes the resulting beam data to the Memory Unit. The capture length is so long that it is enough to span the entire range of the radar. Upon realizing that the operation of the delay-and-sum beamformer is completed, System Controller triggers correlator part of the receiver. Correlator starts to process the data which is already recorded to the Memory Unit by the delay-and-sum beamformer. After correlation is over, it detects the index and magnitude of the peak, which are supplied to System Controller to be ultimately sent to Display Unit.

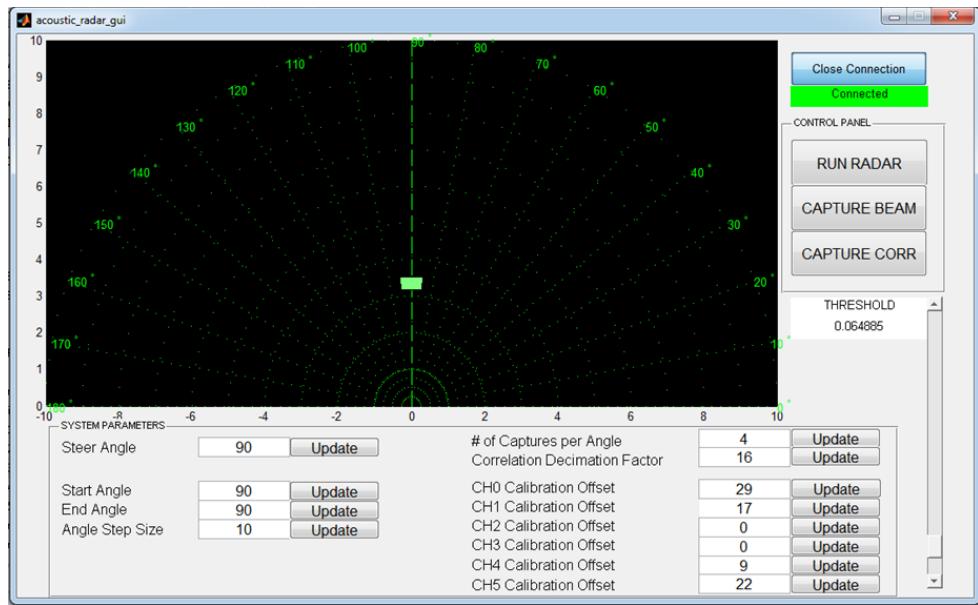

### 3.1.4 System Configuration and Display Unit

This block, which is actually a MATLAB GUI, forms the visual part of the system. In addition to this, it provides user the ability to adjust the acoustic radar system parameters. System Configuration and Display Unit is connected to the Acoustic Radar System Controller over a UDP (User Datagram Protocol) link. Upon a click to an update button in the GUI to modify a system parameter, a UDP packet is transmitted to the Acoustic Radar System Controller,

which is realized as a register write access ultimately. In the normal radar operation, it receives a UDP packet for the current look direction. This packet consists of steer angle information, the index and the value of the correlation. After a simple threshold comparison, the decision whether a valid object is detected for the current angle is made and the corresponding area on the plot is highlighted with a proper intensity which is proportional to the magnitude of the correlation. Upon displaying the position information of the current steer angle, System Configuration and Display Unit transmits a feedback packet to the System Controller, which triggers it to start another transmit-receive cycle for the next steer angle.

Figure 3.3: Acoustic Radar Display Unit

### 3.1.5 Memory Unit

This unit is a block memory used to dump the received echo for further processing. It is implemented using FPGA's dedicated memory primitives (detailed explanation is given in Section 4). This memory is used by three main units in the acoustic radar system, which are, namely, *delay-and-sum beamformer*, *correlator* and the *system controller* units. This multi-purpose usage is achieved via a bus arbitration structure such that for a specific time, the physical port of the memory is devoted to one of the candidates (the bus owner is assigned by the *system controller*). *Delay-and-sum beamformer* and *correlator* uses this memory both as

an input source and an output sink. They read the memory for the input data and write their output to it. So, this is an obvious memory saving. During radar operation, *system controller* does not access to the memory. But, when beamformer or correlator output is asked to be captured by *System Configuration and Display Unit*, *system controller* accesses the memory and sends the requested data to pc.

### **3.1.6 Transmit and Receive Arrays**

Transmit Array is responsible to convert electrical signals which are supplied by the Transmitter unit to acoustical signals. It consists of 6 loudspeakers. The operation of the Receive Array is just the opposite of the Transmit one, which is converting acoustic waves to electrical signals, which are then fed to the Receiver block for further processing. It consists of 6 microphones.

### **3.1.7 Acoustic Radar System Parameters**

In a radar system design problem, there are several parameters which should be taken into account carefully. Radar performance is determined by the design parameters.

In this thesis, only a subset of these parameters is considered since the implemented system has the ability to scan the range and azimuth only. The radar design parameters used in designing the Acoustic Radar System can be listed as follows,

- Pulse Width

- Wavelength

- Pulse Repetition Period

- Pulse Shape

These design parameters -implicitly or explicitly- appears in the so-called “radar equation” and they affect the maximum detection range of the system. So, before explaining them, it would be convenient to give an insight on “radar equation“.

### 3.1.7.1 The Radar Equation

The radar equation is basically the measure on the expected return signal and SNR [17]. Assume that a radar transmits a pulse with power  $P_T$  and there is a target at a range  $R$ . Assume that the radar transmitting antenna has an isotropic radiation pattern, then the power would spread with spherical symmetry. Then the power flux per unit area at range  $R$  would be

$$\text{Power Density} = \frac{P_T}{4\pi R^2} \quad (3.1)$$

If the antenna has a gain  $G$  then the power density at the target area would be multiplied by  $G$ . Assume that the effective area of the target is  $\alpha$ , then the reflected power from the target would be

$$\text{Reflected Power} = \frac{P_T G \alpha}{4\pi R^2} \quad (3.2)$$

and since the power is reflected isotropically, the reflected power density back at the radar is

$$\text{Reflected Power Density} = \frac{P_T G \alpha}{(4\pi R^2)^2} \quad (3.3)$$

Let  $A$  be the effective area of the radar's receiving antenna, then the power received by the antenna is given by

$$P_R = \frac{P_T G A \alpha}{(4\pi R^2)^2} \quad (3.4)$$

The relationship between the antenna gain  $G$  and its effective area  $A$  is given by

$$A = \frac{G \lambda^2}{4\pi} \quad (3.5)$$

Insert (3.5) in (3.4), the basic radar equation is obtained

$$P_R = \frac{P_T G^2 \lambda^2 \sigma}{(4\pi)^3 R^4} \quad (3.6)$$

Usually, the signal that is returned when the target lies somewhere along the maximum of the radar beam is of particular interest. Considering this target, let's define the maximum gain of the antenna  $G_o$  as [16]:

$$G_o = \frac{4\pi A f}{\lambda^2} \quad (3.7)$$

Insert (3.7) in (3.6), then

$$P_R = \frac{P_T \sigma A^2 f^2}{4\pi R^4 \lambda^2} \quad (3.8)$$

Suppose the minimum power required for satisfactory detection,  $P_{R_{min}}$  is known, so (3.8) may be solved for the maximum range of detection,  $R_{max}$ :

$$R_{max} = \sqrt[4]{\frac{P \sigma A^2 f^2}{4\pi P_{R_{min}} \lambda^2}} \quad (3.9)$$

(3.9) is function of the system design parameters which are to be explained shortly.

### 3.1.7.2 Pulse Width

This parameter has a direct effect on the minimum detectable received signal power of the radar, which appears in (3.9) as  $P_{R_{min}}$ .  $P_{R_{min}}$  varies inversely with pulse length since the receiver bandwidth is an inverse function of the pulse length. There is also a tradeoff between increasing the transmitted power through increasing the pulse width and decreasing range ambiguity of the radar. If Pulse Width is increased, the transmitted power also increases. However, increasing the pulse width also increases the range ambiguity (in other words, decreases the range resolution). The range resolution of a radar system is defined as

$$\text{Range Resolution} = \frac{c\tau}{2} \quad (3.10)$$

where,  $\tau$  is the pulse length. In our particular implementation, pulse width is chosen as 2 milliseconds, resulting in a range resolution of  $\frac{(340 \text{ m/s}) \times (2 \text{ msec})}{2} = 34 \text{ cm}$ .

### 3.1.7.3 Wavelength

Wavelength has a direct effect on the power of received signal (3.8). Attenuation increases as the frequency of the signal is increased, in other words, the wavelength is decreased. Beamwidth is another important parameter which is affected by the wavelength (2.38). Beamwidth decreases with increasing frequency. There is a maximum limit on the frequency of the pulse, which is spatial sampling rate constraint. In order to avoid spatial aliasing, the array spacing has to satisfy

$$d \leq \frac{\lambda}{2} = \frac{c}{2f} \quad (3.11)$$

according to the spatial sampling theorem.

So, from (3.11), it is obvious that there is a limit on the maximum frequency of the wave,

$$f_{max} = \frac{c}{2d} \quad (3.12)$$

There are also physical constraints on the distance between transmitter array elements. The minimum distance between transmitter array elements, i.e., between the loudspeakers is 0.12 m. So, frequency of the radar pulse is chosen as the maximum possible  $f = \frac{c}{2d} = \frac{340}{2*0.12} = 1417$  Hz

### 3.1.7.4 Pulse Repetition Period

Pulse Repetition Period (or Frequency) is the time between radar pulses. PRF determines the Maximum Unambiguous Range (3.13) of the system.

$$Maximum\ Unambiguous\ Range = \frac{c \times PRF}{2} \quad (3.13)$$

The Maximum Unambiguous Range is the longest range to which a transmitted pulse can travel and return to the radar before the next pulse is transmitted. “Before the next pulse is transmitted” is the keyword in the definition, because this implies that it is the maximum distance that the radar system measures without any ambiguity. In our particular application

the Maximum Unambiguous Range is chosen as 10 meters. As a result, the Pulse Repetition Period of the system  $T = \frac{2 \times (10 \text{ m})}{(340 \text{ m/sec})} = 58.8 \text{ msec}$

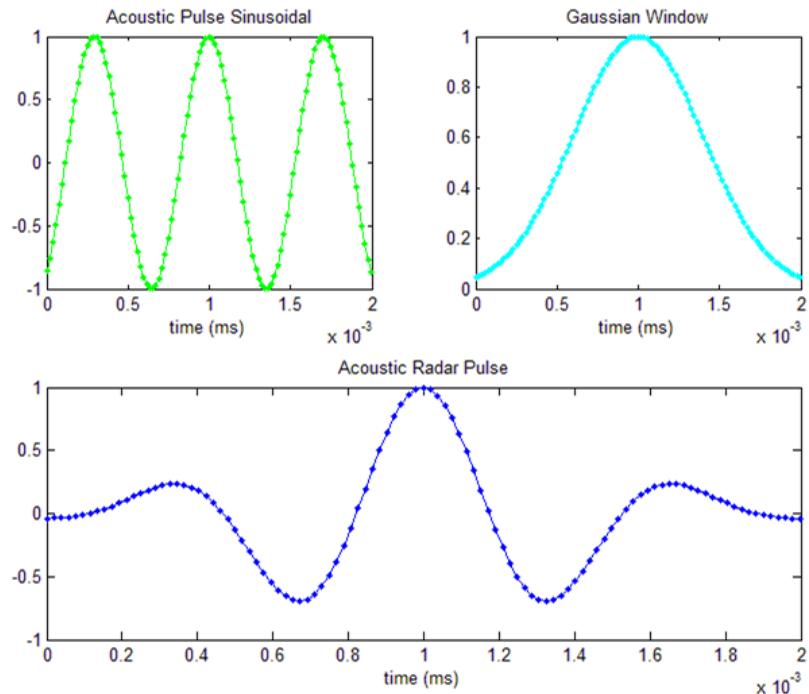

### 3.1.7.5 Pulse Shape

Pulse shape selection is an important decision in the radar system design process. In practice, generally used radar waveforms are linear chirps (chirp is a signal whose frequency increases or decreases with time), non-linear chirps, stepped frequency waveforms (SFW) and binary phase coded pulses (like gold sequences and barker codes). Chirp signals are mostly used to improve the range resolution of the system via pulse compression. Phase coded pulses are preferred for thesis desirable autocorrelation functions. In this thesis work, a simple pulse shape is used. The reason why such a simple pulse shape is selected is to have simple transmitter and receiver structures (Note that the primary task of this thesis work is not to implement sophisticated array signal processing algorithms). Acoustic radar pulse is generated by windowing a sinusoidal signal with a gaussian, as seen from Figure 3.4.

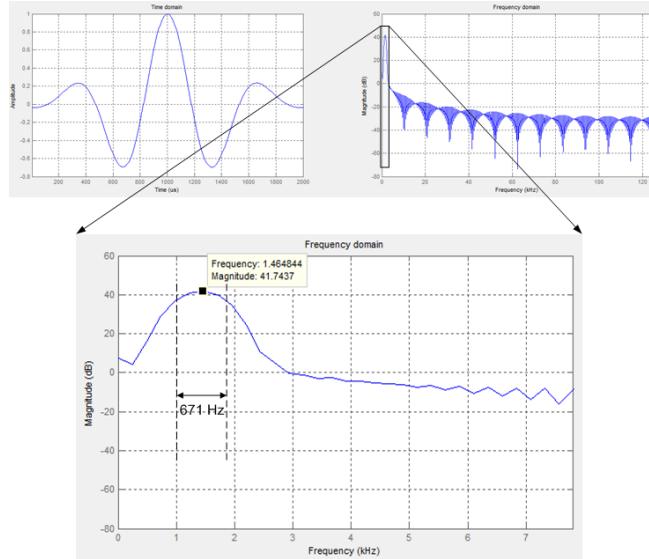

Figure 3.4: The Acoustic Radar Pulse

The magnitude response (in dB) of the acoustic radar pulse, which is the spectrum of a sinusoidal signal windowed by a gaussian, is given in Figure 3.5. It can be seen from the figure that the carrier frequency of the acoustic radar is 1417 Hz (approximately) and the 3 db bandwidth of the signal is 671 Hz. The carrier frequency and the bandwidth of the pulse is comparable. So, narrowband assumption, which requires  $B \ll \omega_c$  condition, cannot be applied for this case. In other words, the acoustic radar pulse is a wideband signal.

Figure 3.5: Acoustic Radar Pulse Magnitude Response

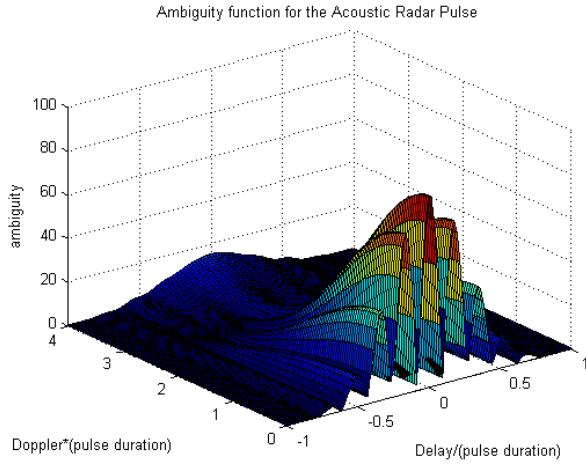

Before leaving this section, the **Ambiguity Function**, which is a well-known performance parameter for a radar system, corresponding to the particular Acoustic Radar Pulse will be given. The ambiguity function (AF) represents the time response of a filter which is matched to a given finite energy signal when the signal is received with a delay  $\tau$  and a Doppler shift  $\nu$  relative to the nominal values (zeros) expected by the filter [18]. It is defined as;

$$|\chi(\tau, \nu)| = \left| \int_{-\infty}^{\infty} u(t) u^*(t + \tau) e^{j2\pi\nu t} dt \right| \quad (3.14)$$

where  $u$  is the complex envelope of the signal. Using (3.14), AF for the Acoustic Radar Pulse is calculated. It is shown in Figure 3.6. Note that the *Doppler* and *Delay* variables in Figure 3.6 are normalized values with respect to the pulse duration (or width), which is 2 msec as mentioned above.

Figure 3.6: Ambiguity function for the Acoustic Radar Pulse

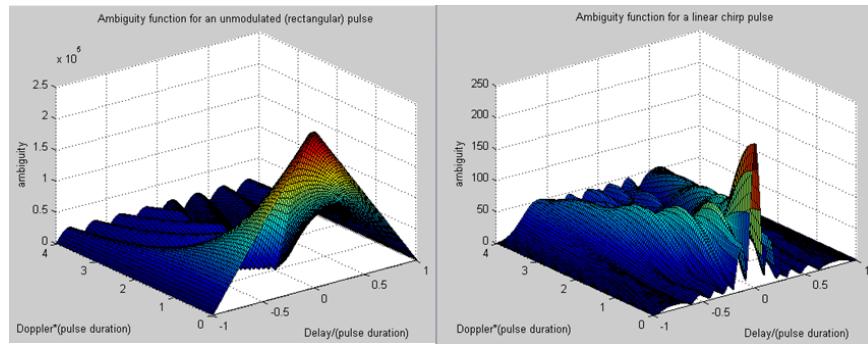

The ambiguity performance of the Acoustic Radar Pulse can be evaluated better when compared with different pulse shapes. In Figure 3.7, ambiguity functions for two different signals are given. The signal whose AF is given on the left is an unmodulated (rectangular) pulse. The other one is a linear chirp pulse, whose frequency varies linearly from 100 Hz to 1417 Hz (which is the frequency of the Acoustic Radar Pulse). They both have the same pulse width of 2 msec as the Acoustic Radar Pulse. When the mainlobe widths of three pulses are compared, it is easily concluded that the linear chirp pulse has the best performance, while the unmodulated pulse has the worst. The ambiguity performance of the particular Acoustic Radar Pulse is in between, as seen easily from figures 3.6 and 3.7.

Figure 3.7: Ambiguity function for an unmodulated (left) pulse and a chirp pulse (right) of the same length as the Acoustic Radar Pulse

## CHAPTER 4

### FPGA IMPLEMENTATION OF RADAR PROCESSING

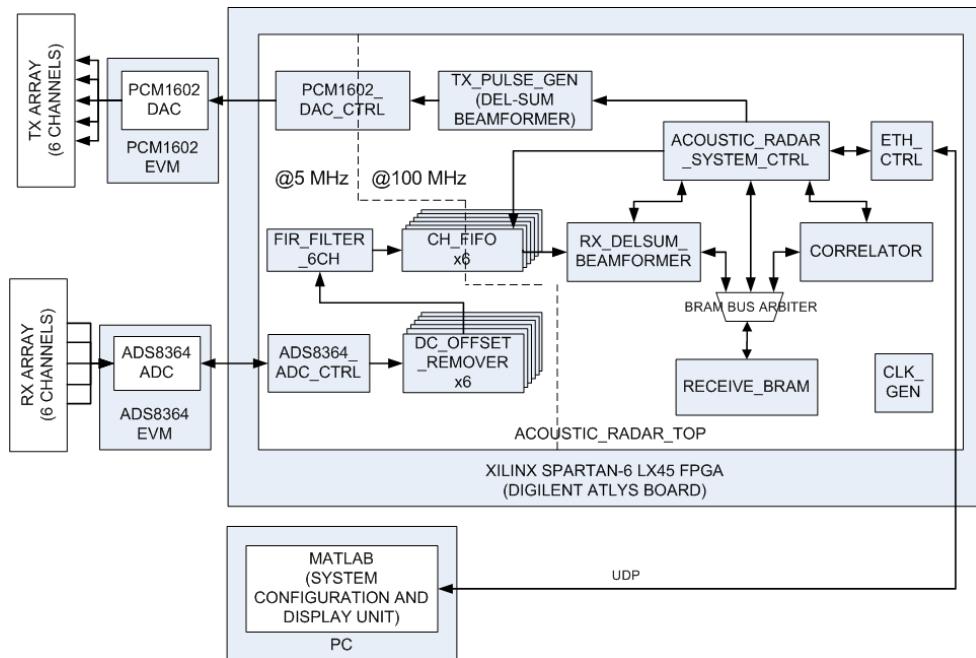

In this section, the detailed description of the implemented radar system is given. Firstly, the hardware on which the system is implemented will be explained briefly. Then the FPGA building blocks will be described in detail. Note that all the mathematical functions of the Acoustic Radar is implemented in real time on FPGA.

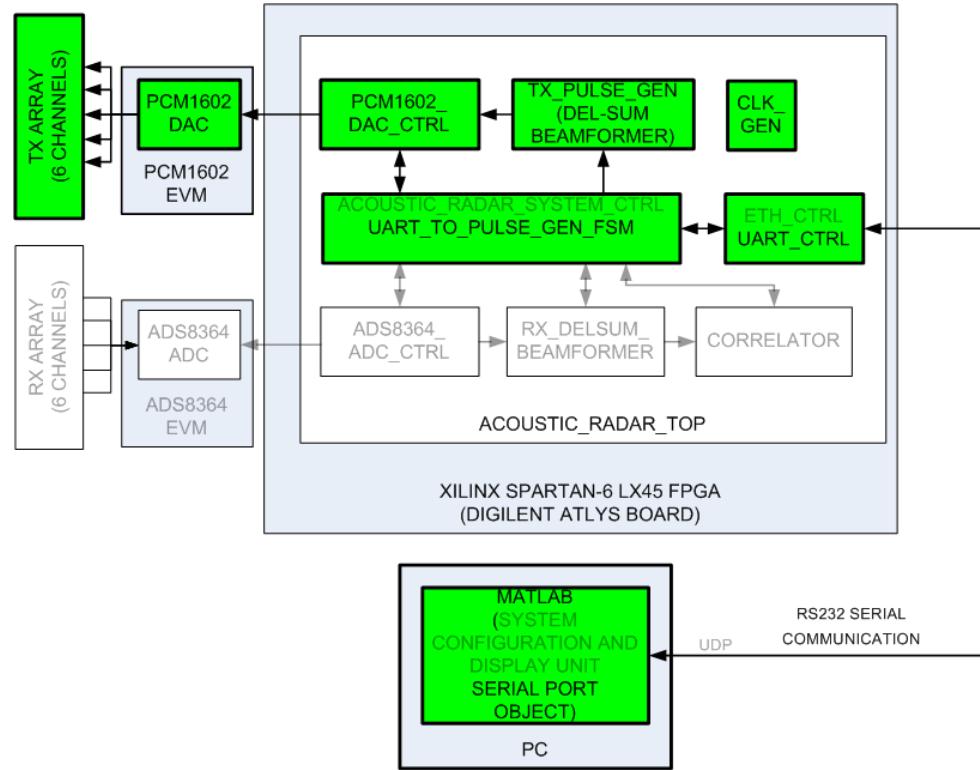

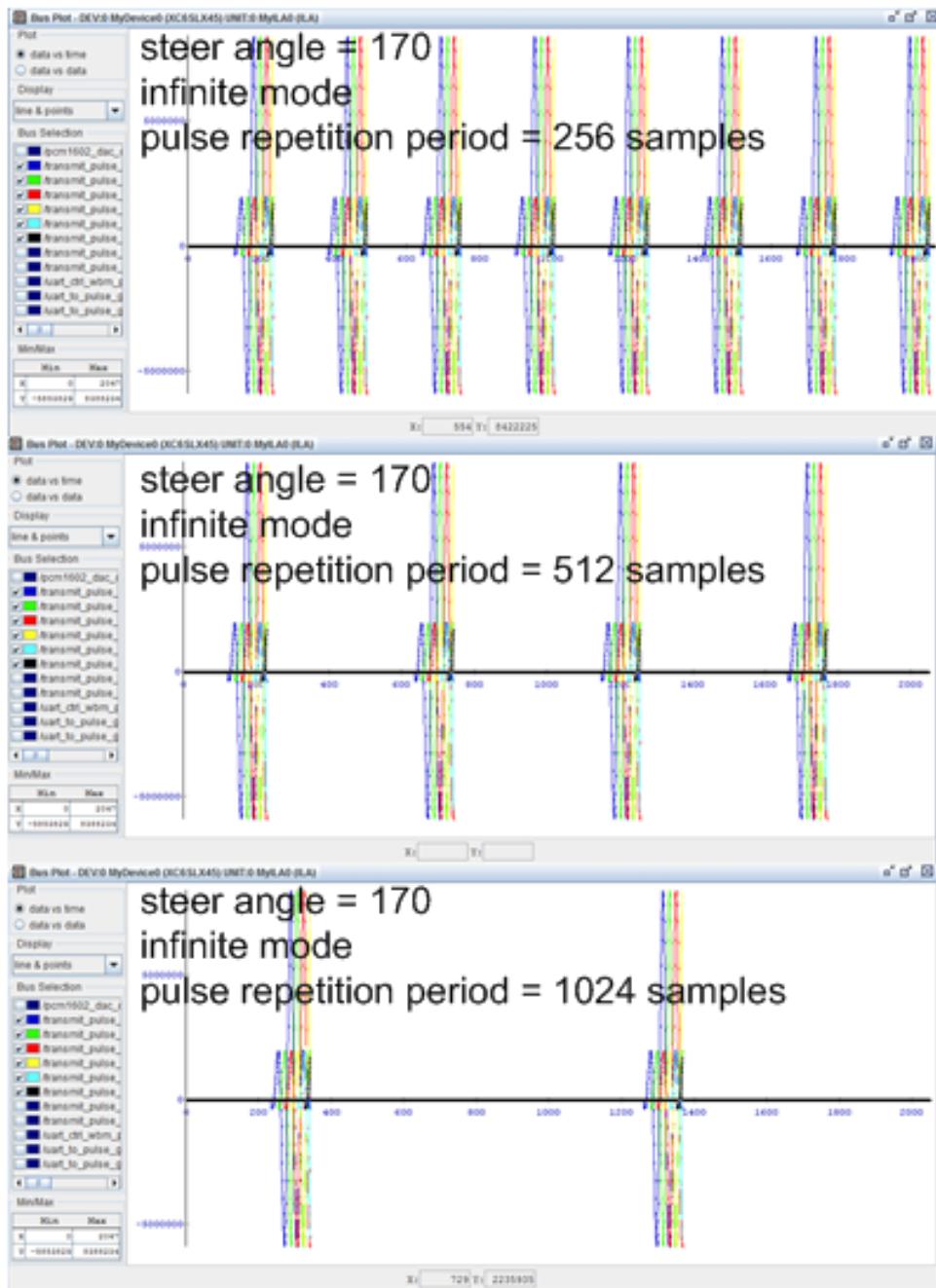

Figure 4.1: Implemented Radar System Structure

## 4.1 Hardware Description

In Figure 4.1, the radar system structure is given. The hardware that the radar system is implemented on mainly consists of 3 parts:

1. DIGILENT ATLYS Spartan-6 FPGA Board [20]

2. TI PCM1602 DAC Evaluation Module [21]

3. TI ADS8364 ADC Evaluation Module [22]

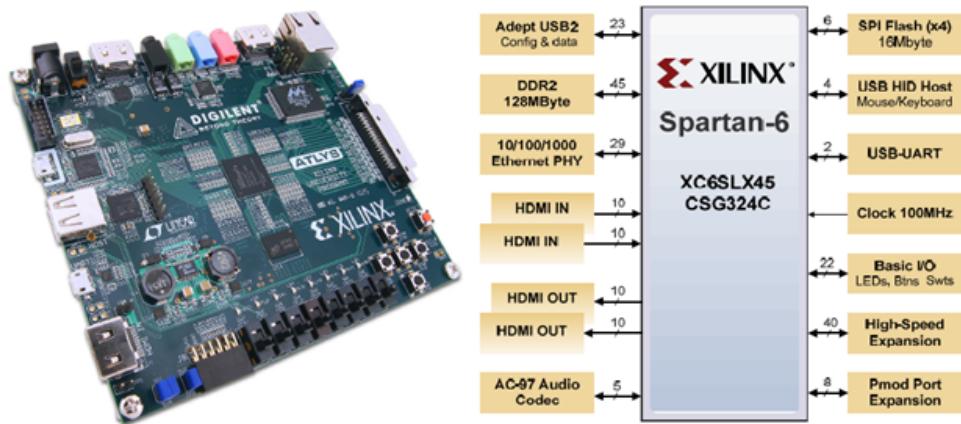

### 4.1.1 DIGILENT ATLYS Spartan-6 FPGA Board

The main hardware unit of the radar system is the FPGA board, namely, Digilent ATLYS XILINX Spartan-6 Board. Figure 4.2 shows this board and the functional outline of the FPGA. All the digital signal processing is handled in the FPGA. FPGA Board has external interfaces with ADC and DAC evaluation modules and the PC. The reason why this FPGA board is chosen is that the performance of Spartan-6 FPGA is enough for our particular application and that the board is cost efficient when compared to other available ones in the field.

Figure 4.2: Top view and functional block diagram of ATLYS FPGA Board

The Spartan-6 LX45 is a high performance FPGA [19], it consists of

- 6822 slices (each of them contains four 6-input LUTs and eight flip flops)

- 2.1 Mbits of block RAMs (which is really important as the system necessitates many memory elements like FIFOs, RAMs and ROMs)

- Four clock tiles (8 DCMs (Digital Clock Manager) and 4 PLLs (Phased Locked Loops))

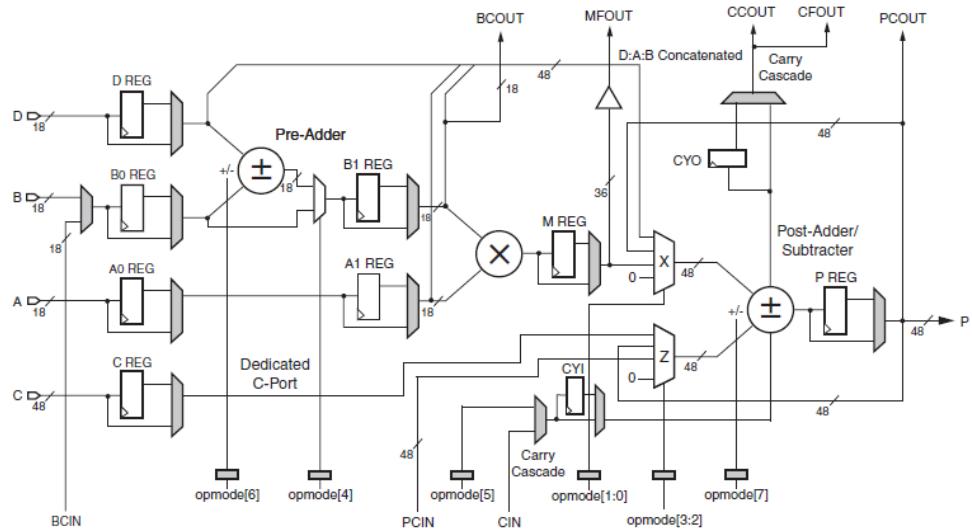

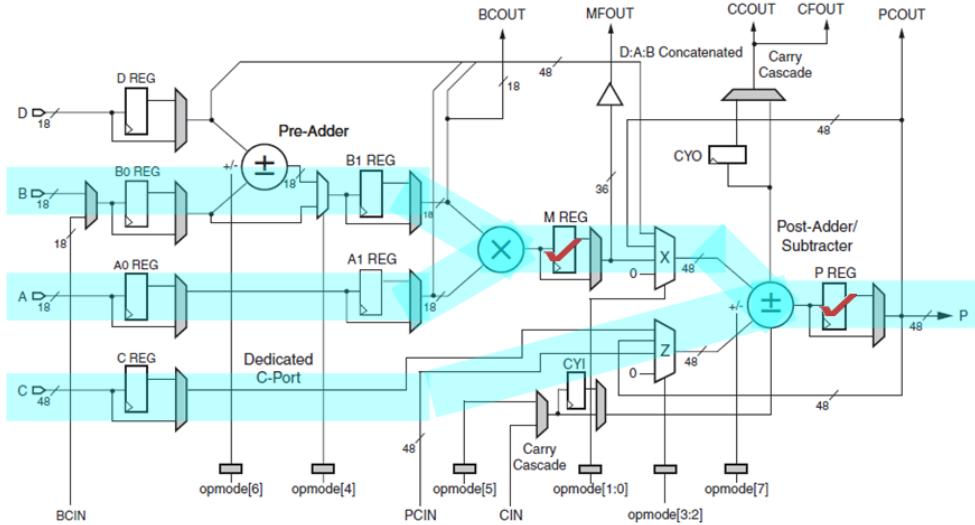

- 58 DSP Slices (these are specific optimized structures in FPGA, supporting many DSP algorithms with minimal use of the general purpose FPGA fabric. They are, at first look, 18x18 bit two's complement multiplier followed by a 48 bit sign extended adder/subtractor/accumulator, which are configurable in various ways)