BROADBAND HIGH EFFICIENCY RF POWER AMPLIFIER DESIGN BASED

ON MODIFIED CLASS-J APPROACH WITH APPLICATIONS USING GAN

HEMT TECHNOLOGY

A THESIS SUBMITTED TO

THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

OF

MIDDLE EAST TECHNICAL UNIVERSITY

BY

MURAT KOÇ

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF MASTER OF SCIENCE

IN

ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2021

Approval of the thesis:

**BROADBAND HIGH EFFICIENCY RF POWER AMPLIFIER DESIGN

BASED ON MODIFIED CLASS-J APPROACH WITH APPLICATIONS

USING GAN HEMT TECHNOLOGY**

submitted by **MURAT KOÇ** in partial fulfillment of the requirements for the degree of **Master of Science in Electrical and Electronics Engineering Department, Middle East Technical University** by,

Prof. Dr. Halil Kalıçlılar \_\_\_\_\_

Dean, Graduate School of **Natural and Applied Sciences**

Prof. Dr. İlkay Ulusoy \_\_\_\_\_

Head of Department, **Electrical and Electronics Engineering**

Prof. Dr. Şimşek Demir \_\_\_\_\_

Supervisor, **Electrical and Electronics Engineering, METU**

**Examining Committee Members:**

Prof. Dr. Gönül Turhan Sayan \_\_\_\_\_

Electrical and Electronics Engineering, METU

Prof. Dr. Şimşek Demir \_\_\_\_\_

Electrical and Electronics Engineering, METU

Prof. Dr. Özlem Aydın Çivi \_\_\_\_\_

Electrical and Electronics Engineering, METU

Prof. Dr. Sencer Koç \_\_\_\_\_

Electrical and Electronics Engineering, METU

Assoc. Prof. Dr. Ahmet Hayrettin Yüzer \_\_\_\_\_

Electrical and Electronics Engineering, Karabük University

Date: 29.09.2021

**I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.**

Name, Surname: Murat Koç

Signature :

## ABSTRACT

# **BROADBAND HIGH EFFICIENCY RF POWER AMPLIFIER DESIGN BASED ON MODIFIED CLASS-J APPROACH WITH APPLICATIONS USING GAN HEMT TECHNOLOGY**

Koç, Murat

M.S., Department of Electrical and Electronics Engineering

Supervisor: Prof. Dr. Şimşek Demir

SEPTEMBER 2021, 112 pages

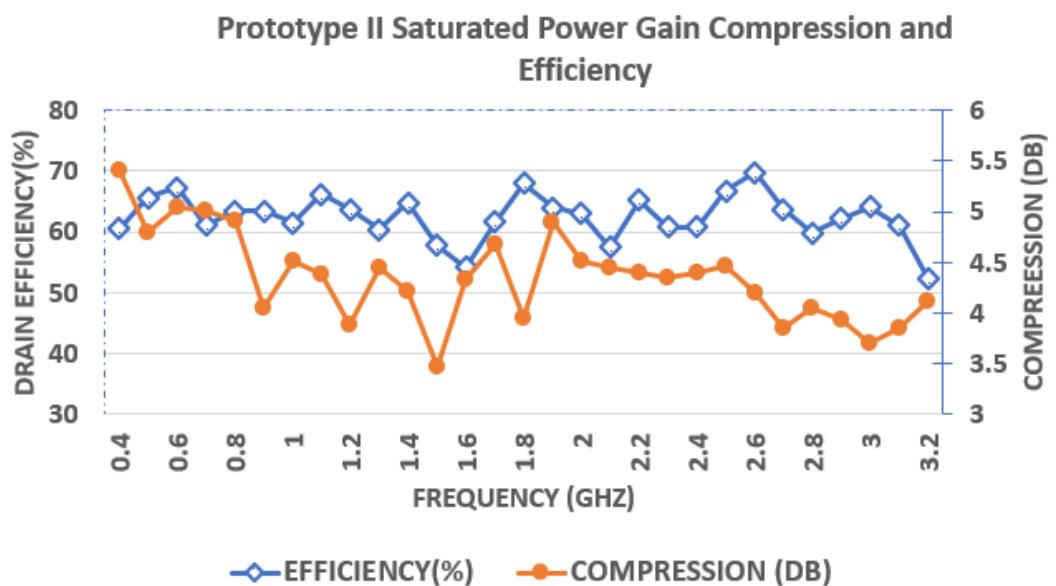

RF power amplifiers have been the essential elements of any transmit/receive block. Especially in the transmit chain, some applications require high RF power, such as radar, jammer, telecommunication signals targeting a wide range of coverage. High power requirements in RF broadcast mean high supply power to feed RF PA. The efficiency parameter of a high-power transmission system becomes an issue due to heating problems and performance degradation depending on rising temperatures. The heating problem is commonly solved using active cooling plants. Cooling plants add extra cost demanding discrete power supplies and considerable amount of design labor. With these problems at hand, industrial and academic environments have turned to look for more efficient amplifier topologies. In this thesis, modified class-J schemes proposed to enhance operating bandwidth are studied. A modification called "normalized resistive-reactive class-J" (NRRCJ) approach is proposed. Detailed parametric analysis is presented. The effects of parameters in governing equations are discussed. A related engineering design procedure is demonstrated with an ultra-broadband GaN PA. Prototype PA operating at 400-3200 MHz capable of at least 10 W saturated output power is fabricated. Measured efficiency values of %53 – %69.8 are obtained at

saturated output power. The average efficiency is calculated as %62.45. The measurement results, theoretical aspects, and expectations are compared. It is shown that the resistive termination of harmonics in a systematic way makes it possible to achieve a broadband and relatively high efficiency performance, simultaneously. The final prototype achieves remarkable compatibility with a practical RF system, compared with similar examples in the literature, in terms of size, gain, efficiency, output power and operating frequency band.

Keywords: RF PA, High Efficiency, UHF, VHF, Broadband, Normalized Resistive-Reactive Class-J

## ÖZ

# ALTERNATİF J-SINIFI YAKLAŞIMI İLE GAN TEKNOLOJİSİ TEMELLİ GENİŞ BANT YÜKSEK VERİMLİ GÜC YÜKSELTECİ UYGULAMALARI

Koç, Murat

Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü

Tez Yöneticisi: Prof. Dr. Şimşek Demir

Eylül 2021 , 112 sayfa

Radyo frekans güç yükselteçleri gönderme ve alma zincirinin vazgeçilmez elemanlarındandır. Özellikle radar, sinyal karıştırıcı ve uzun menzil haberleşme sinyali iletimi yüksek çıkış gücü gerektiren uygulamalarıdır. Yüksek RF güç çıkışları isterleri beraberinde daha fazla DC güç tüketimine neden olmaktadır. RF güçe dönüşmeyen enerji güç yükselteci etrafında ısiya dönüşerek kritik sıcaklık artışlarına neden olmaktadır. Bu sebele güç yükseltecinin verim parametresi önem arz etmektedir. Isınma problemi birçok sistemde aktif soğutma yöntemleriyle aşılmaktadır. Aktif soğutma yöntemleri sistem tasarımda ayrık güç besleme üniteleri kullanılmasını gerektirebilir. Bunun yanında ek tasarım işçiliği bedelleriyle toplam sistem maliyetini artırmaktadır. Endüstriyel ve akademik çevreler, bu etkenleri göz önüne alarak, verimli yükselteç topolojileri üzerine yoğunlaşmaktadır. Bu tez çalışmasında literatürde mevcut, bant genişliğini artırmayı amaçlayan alternatif-J sınıfı tasarım yöntemleri incelenmiştir. Bu fikirlerden yola çıkarak türev bir yaklaşım olan "düzgelenmiş dirençsel-tepkin J sınıfı" alternatifçi önerilmiştir. Detaylı parametre analizleri sunulmuştur. Teorik başıntılarla ilintili olarak geliştirilen tasarım prosedürü ultra geniş bantlı bir GaN güç

yükselteç ile gösterilmiştir. Prototip yükseltçeç 400-3200 MHz bant aralığında, doygun gücü en az 10W olacak şekilde tasarlanıp üretilmiştir. Verimlilik 53% – 69.8% arasında elde edilmiştir. Ortalama verim 62.45% olarak hesaplanmıştır. Ölçüm sonuçları ve teorik beklentiler karşılaştırılmıştır. Sistematik şekilde yapılan harmonik empedans uyumlamlarının bant genişliğini artırırken verimi de makul seviyelerde tutmaya olanak sağladığı gösterilmiştir. Kazanç, verim, boyut, bant genişliği, çıkış gücü gibi kriterler çerçevesinde literatürde var olan benzer örneklerle kıyaslama yapıldığında üstün veya denk performans özelliklerini gözlenmiştir. Bu kıyaslamalar sonucunda pratik RF uygulamalarına uyumlu bir tasarım çıktıısı elde edildiği sonucuna varılmıştır.

**Anahtar Kelimeler:** RF güç yükselteci, yüksek verim, UHF, VHF, Geniş bant, düzgeçenmiş dirençsel-tepkin J sınıfı

TO MY MOTHER...

## **ACKNOWLEDGMENTS**

First, I would like to thank Professor Şimşek Demir for his constructive guidance throughout this research. His encouraging attitudes provided me with a confidence enabling the achievements of this work. It was a great honor to work with him.

I am grateful to METU professors for the extremely beneficial lectures in MSc. programme. The courses I had taken in METU provided me with a strong academic background in pursuit of academic research. In addition, I thank all faculty staff for their dedicated effort in department affairs.

I would like to thank ASELSAN Inc., my division managers and colleagues. They encouraged me to perform this academic research with their sincere attitudes. ASELSAN provided me with the facilities to carry out this research with confidence. It has been a great honor for me to be a member of the ASELSAN family.

Thanks to my family for their offerings of wisdom and special advices when I needed. Their continuous moral support allowed me to achieve this degree. I always felt special for having them with me.

## TABLE OF CONTENTS

|                                                                                      |      |

|--------------------------------------------------------------------------------------|------|

| ABSTRACT . . . . .                                                                   | v    |

| ÖZ . . . . .                                                                         | vii  |

| ACKNOWLEDGMENTS . . . . .                                                            | x    |

| TABLE OF CONTENTS . . . . .                                                          | xi   |

| LIST OF TABLES . . . . .                                                             | xiii |

| LIST OF FIGURES . . . . .                                                            | xiv  |

| LIST OF ABBREVIATIONS . . . . .                                                      | xx   |

| CHAPTERS                                                                             |      |

| 1 INTRODUCTION . . . . .                                                             | 1    |

| 1.1 RF Power Amplifiers . . . . .                                                    | 1    |

| 1.1.1 Technologies and Terminologies Used in Design of RF Power Amplifiers . . . . . | 1    |

| 1.1.2 GAN HEMT Technology . . . . .                                                  | 6    |

| 1.2 Resarch Motivations and Objectives . . . . .                                     | 8    |

| 1.3 Contributions . . . . .                                                          | 9    |

| 1.4 The Outline of the Thesis . . . . .                                              | 10   |

| 2 LITERATURE REVIEW . . . . .                                                        | 13   |

| 2.1 Conventional Modes of Operation . . . . .                                        | 13   |

|       |                                                       |     |

|-------|-------------------------------------------------------|-----|

| 2.1.1 | Class-A, B and A/B . . . . .                          | 13  |

| 2.2   | Load-Line Theory of Ideal Linear Amplifier . . . . .  | 31  |

| 3     | METHODOLOGY OF MODIFIED CLASS-J APPROACH . . . . .    | 39  |

| 3.1   | Class-J Theory . . . . .                              | 39  |

| 3.2   | Modified Class-J Theoretical Approaches . . . . .     | 44  |

| 3.3   | Proposed Modified Class-J Approach . . . . .          | 51  |

| 4     | PRACTICAL IMPELEMENTATION OF NRRCJ APPROACH . . . . . | 59  |

| 4.1   | Design Scheme for Broadband PA Design . . . . .       | 59  |

| 4.1.1 | Three-Octave Design Scheme . . . . .                  | 64  |

| 4.2   | Design of the Prototype . . . . .                     | 67  |

| 4.2.1 | Output Matching Design . . . . .                      | 67  |

| 4.2.2 | Prototype I . . . . .                                 | 75  |

| 4.2.3 | Prototype I Results . . . . .                         | 81  |

| 4.2.4 | Prototype II . . . . .                                | 87  |

| 4.2.5 | Prototype 2 Results . . . . .                         | 92  |

| 5     | CONCLUSIONS . . . . .                                 | 103 |

| 5.1   | Comparison with Other Works . . . . .                 | 103 |

| 5.2   | Conclusions . . . . .                                 | 105 |

| 5.3   | Future Work . . . . .                                 | 105 |

|       | REFERENCES . . . . .                                  | 107 |

## LIST OF TABLES

### TABLES

|                                                                                             |     |

|---------------------------------------------------------------------------------------------|-----|

| Table 1.1 Parameters for Microwave Semiconductor Materials . . . . .                        | 7   |

| Table 3.1 Summary of important parameters for the well-known classes of operation . . . . . | 44  |

| Table 4.1 Bill of Materials List Of Output Circuit . . . . .                                | 76  |

| Table 4.2 Bill of Materials List Of Input Circuit Prototype I . . . . .                     | 81  |

| Table 4.3 Bill of Materials List Of Prototype 2 . . . . .                                   | 88  |

| Table 5.1 Comparsion table . . . . .                                                        | 104 |

## LIST OF FIGURES

### FIGURES

|             |                                                                                                                             |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1  | Reflection Plane Definitions with a Device Under Test (DUT) . . . . .                                                       | 4  |

| Figure 2.1  | Transistor and surrounding RF circuit diagram showing used current conventions. . . . .                                     | 14 |

| Figure 2.2  | I-V current profile of a simple FET . . . . .                                                                               | 16 |

| Figure 2.3  | Basic Constant Transconductance VCCS Model . . . . .                                                                        | 18 |

| Figure 2.4  | Class-A Drain and Current Waveforms for $V_{dd} = 1$ , $I_{max} = 1$ . . . . .                                              | 19 |

| Figure 2.5  | Red-line paths showing dynamic I-V loadline. The knee voltage is zero. . . . .                                              | 19 |

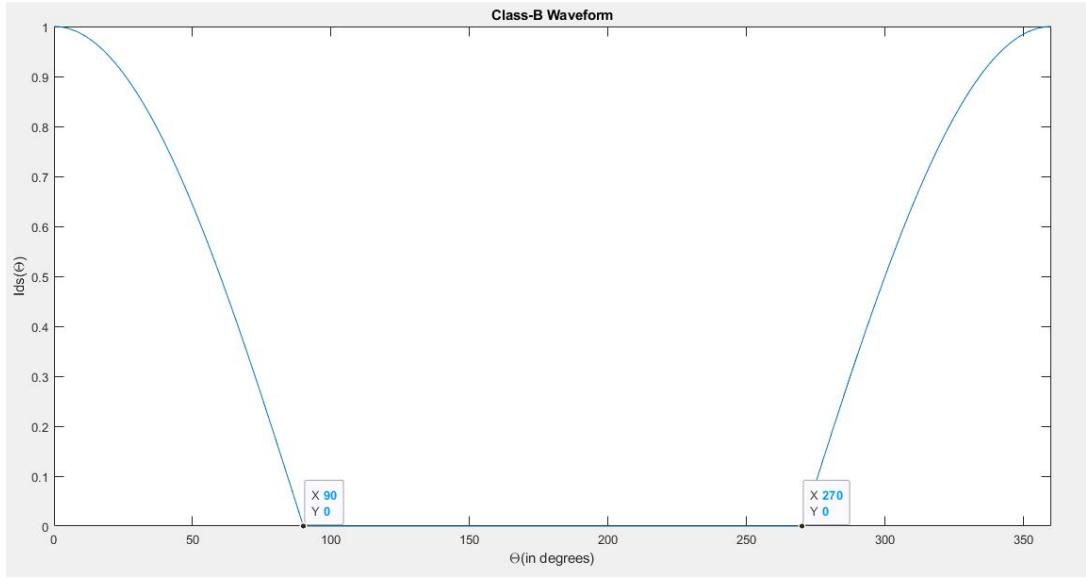

| Figure 2.6  | Conventional Class-B Waveform (Normalized to Peak Value) . . . . .                                                          | 21 |

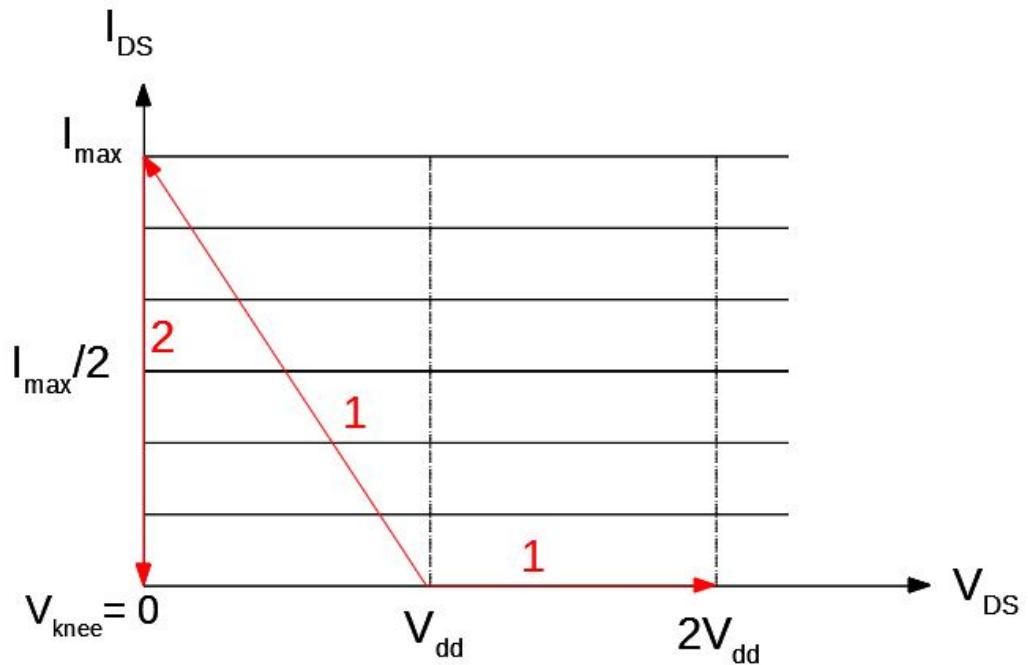

| Figure 2.7  | Zero-knee load-line trajectory for class-B . . . . .                                                                        | 23 |

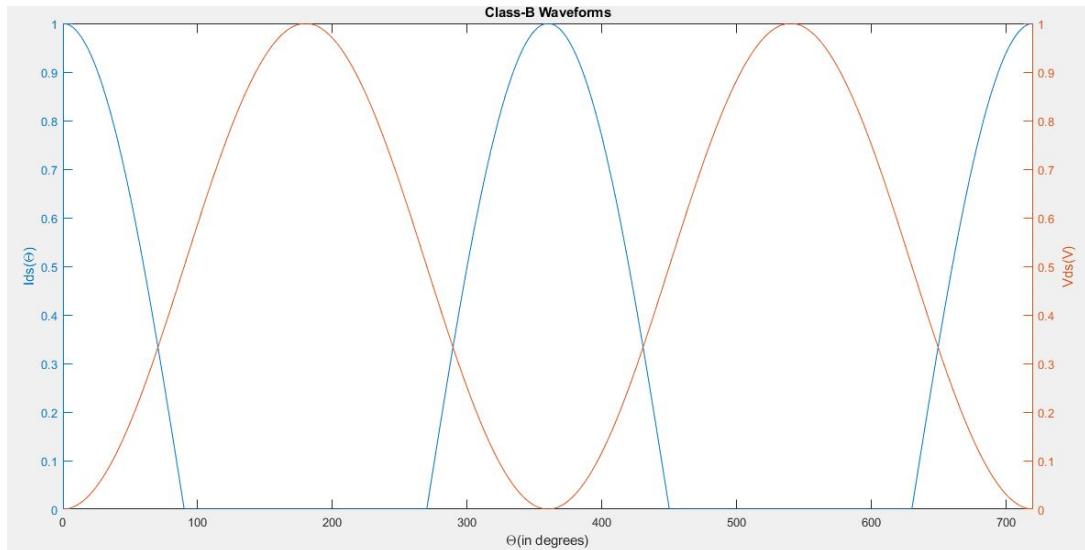

| Figure 2.8  | Class-B voltage and current waveforms normalized to their peak value ( $R_{opt} = 1, V_{dd} = 0.5, I_{max} = 1$ ) . . . . . | 24 |

| Figure 2.9  | Non-zero knee voltage fan diagram . . . . .                                                                                 | 25 |

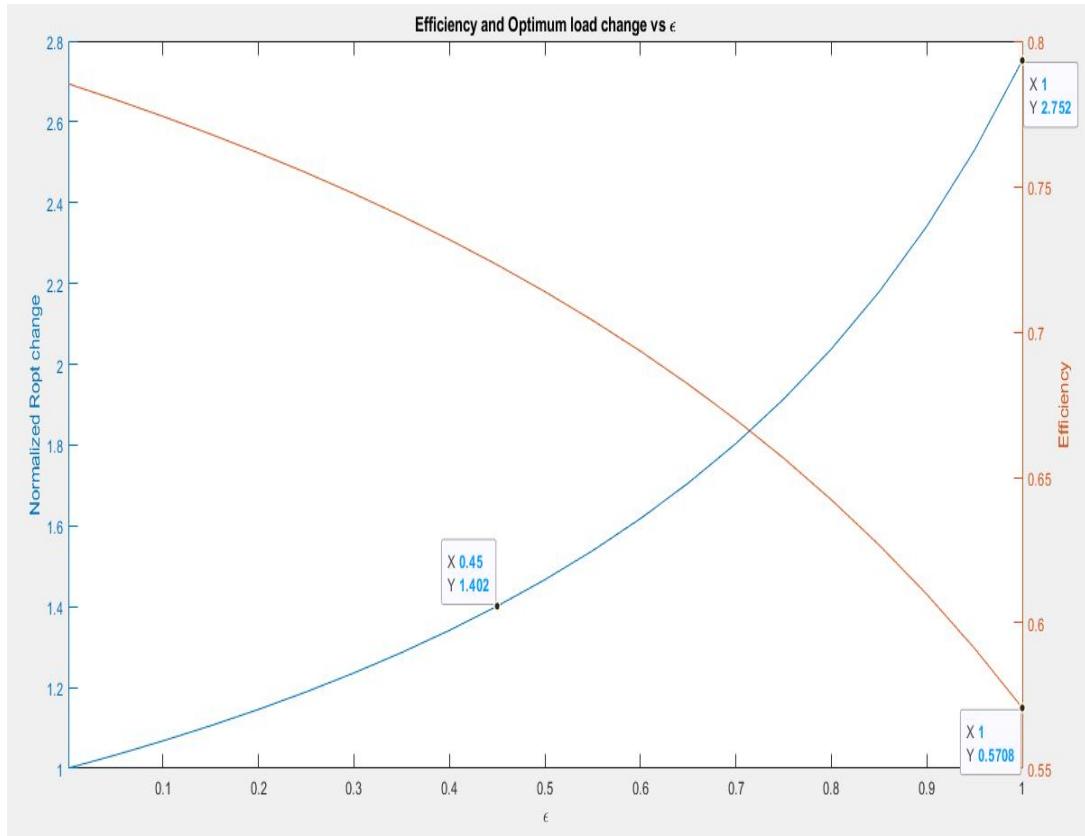

| Figure 2.10 | Normalized optimum load and efficiency change vs $\varepsilon$ factor . . . . .                                             | 26 |

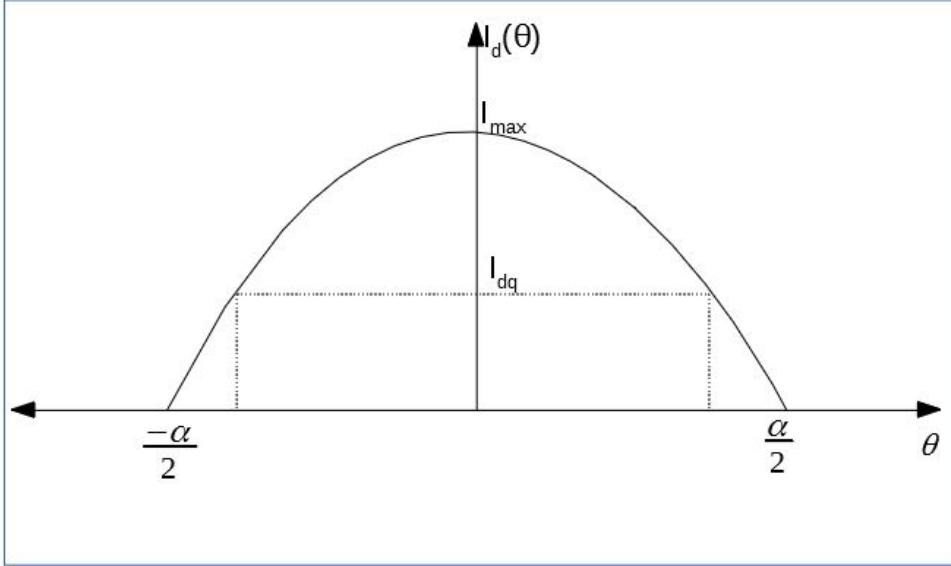

| Figure 2.11 | Current waveform with $\alpha$ conduction angle . . . . .                                                                   | 28 |

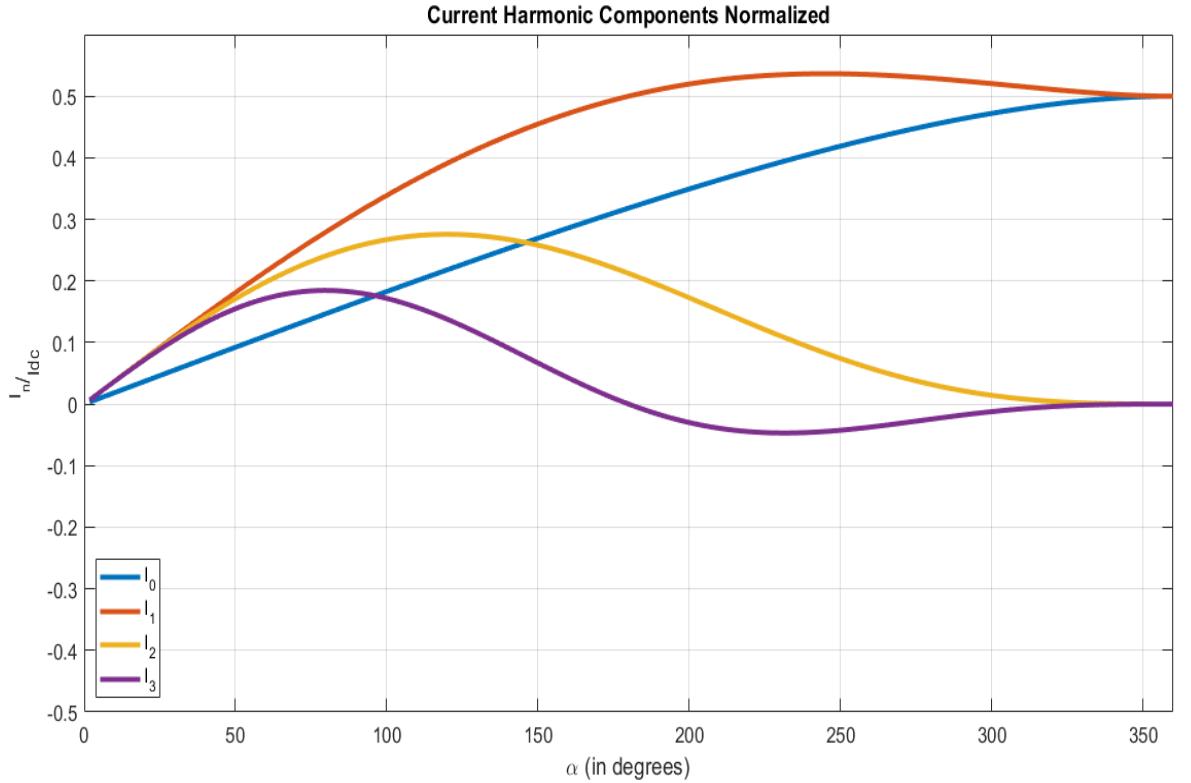

| Figure 2.12 | Conduction angle versus normalized harmonic amplitudes. . . . .                                                             | 29 |

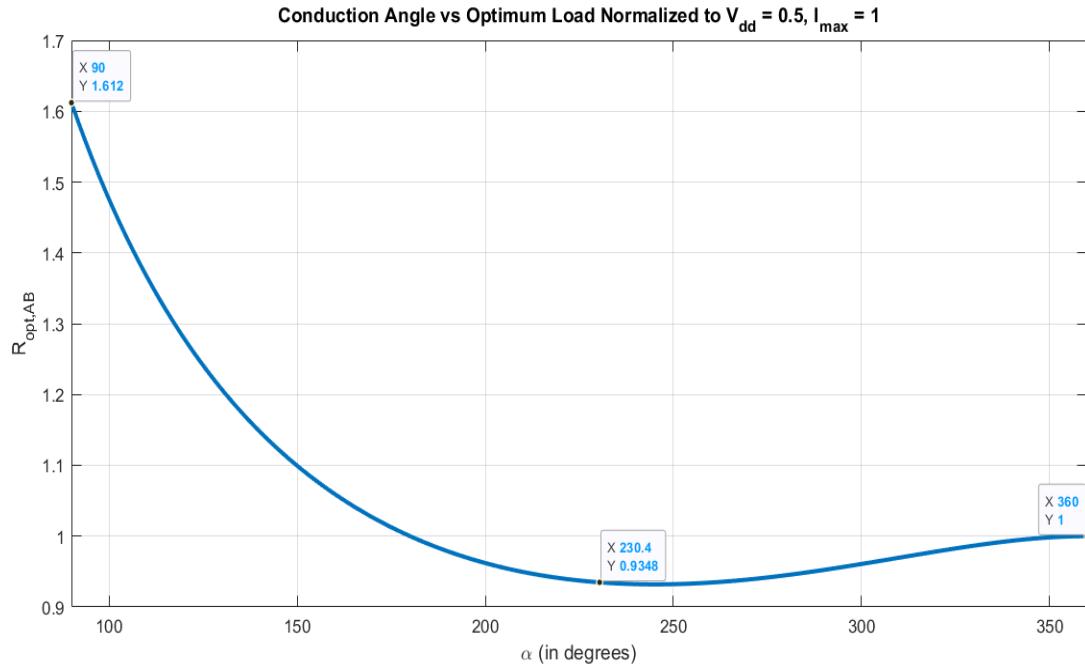

| Figure 2.13 | Conduction angle versus optimum load. . . . .                                                                               | 30 |

|                                                                                                                                                    |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

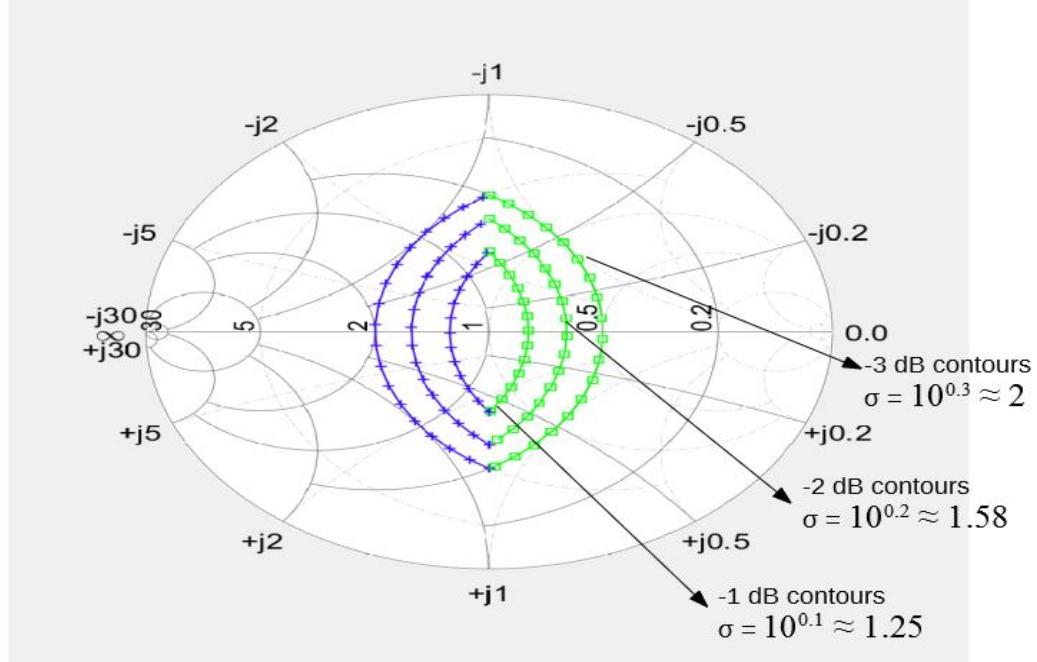

| Figure 2.14 Constant power contours at 1-3 dB back-off. Smith Chart is normalized to $R_{opt}$ . . . . .                                           | 35 |

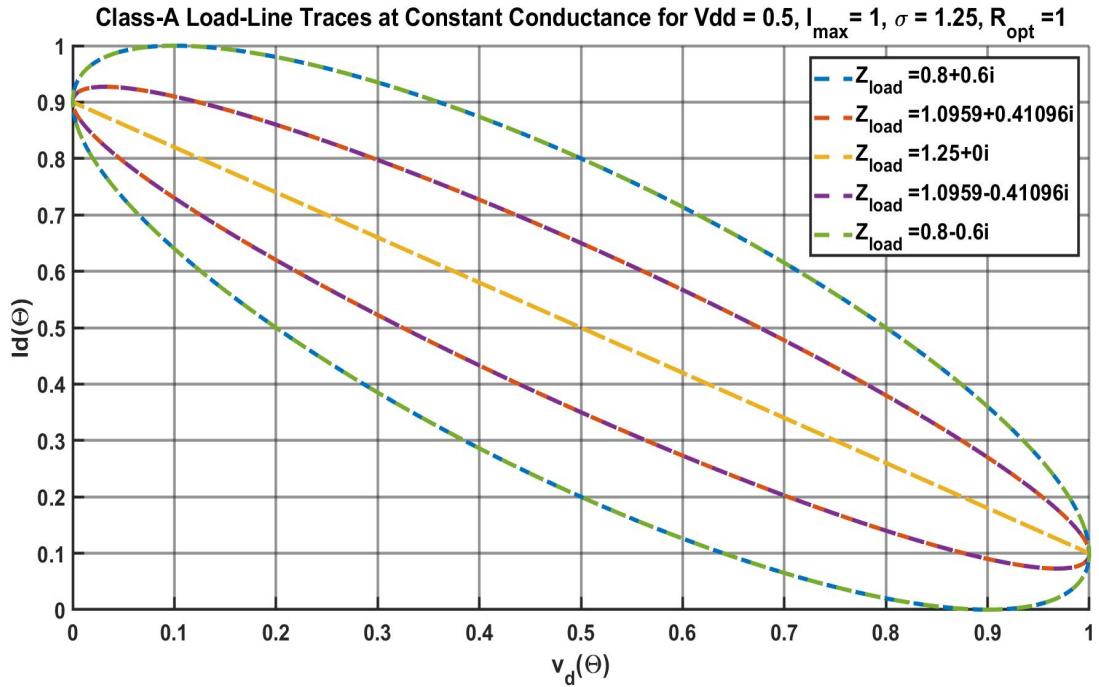

| Figure 2.15 Sample loadlines on the $P_{-1dB}$ impedance contour spanning thorough constant conductance. . . . .                                   | 36 |

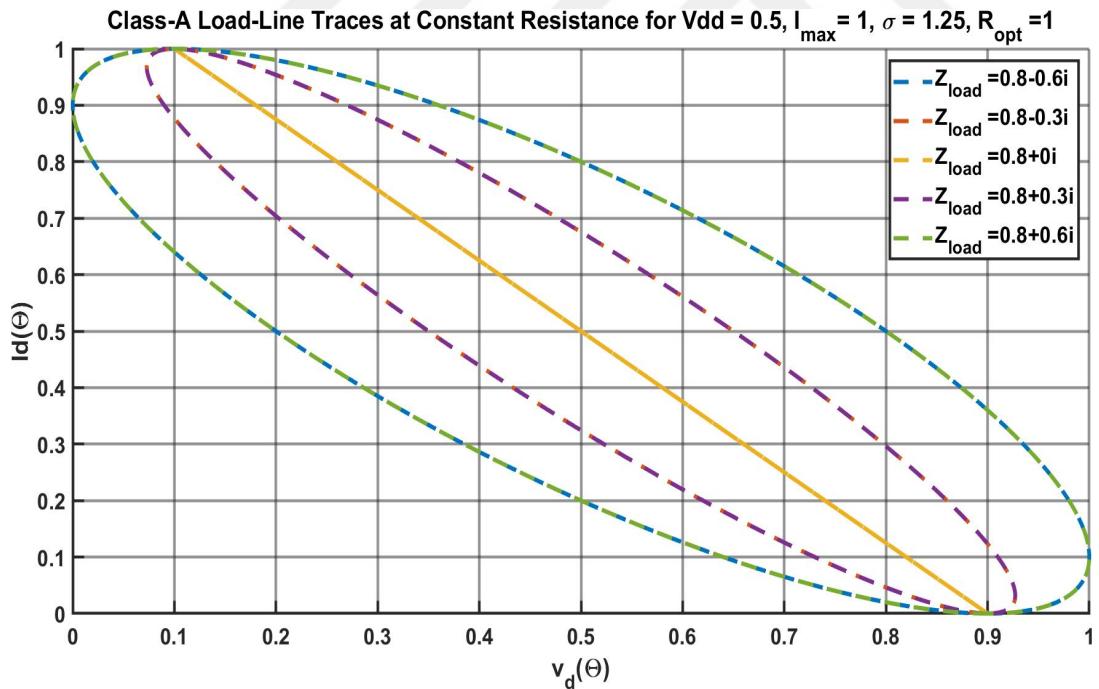

| Figure 2.16 Sample loadlines on the $P_{-1dB}$ impedance contour spanning through constant resistance. . . . .                                     | 36 |

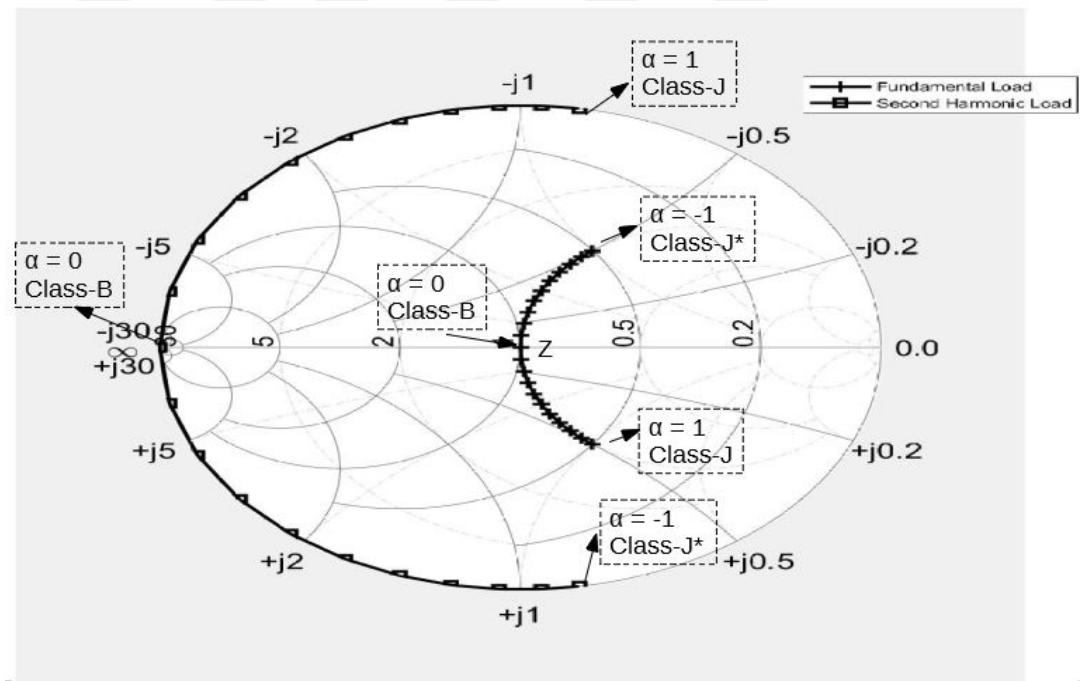

| Figure 3.1 Fundamental and second harmonic impedance set for varying $\alpha$ values . . . . .                                                     | 41 |

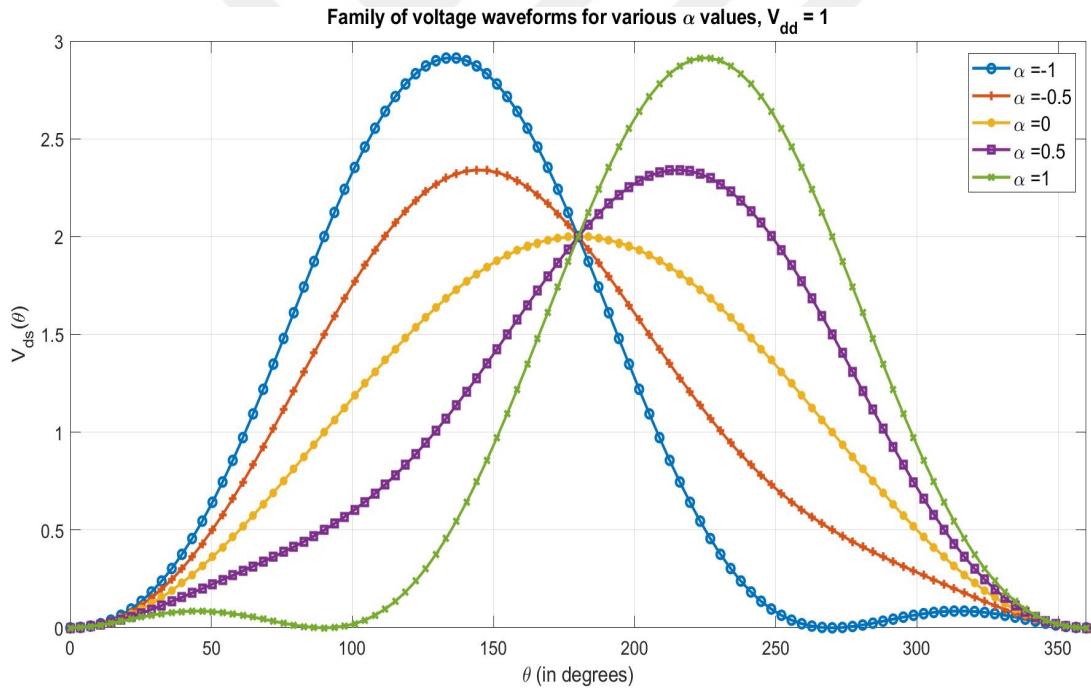

| Figure 3.2 $\alpha$ family of voltage waveforms . . . . .                                                                                          | 42 |

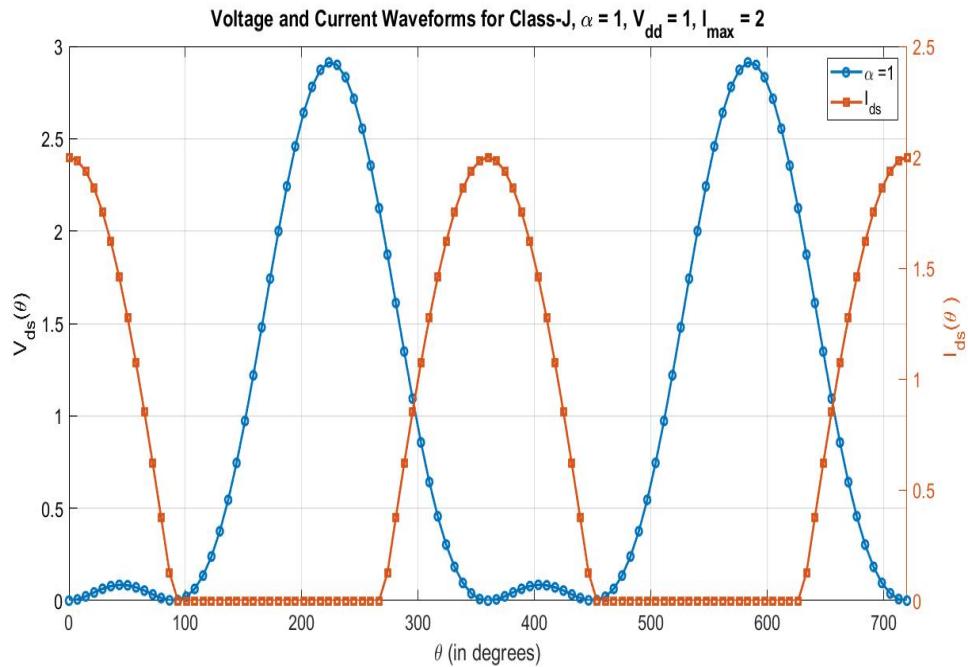

| Figure 3.3 Class-J Voltage and Current Waveforms . . . . .                                                                                         | 43 |

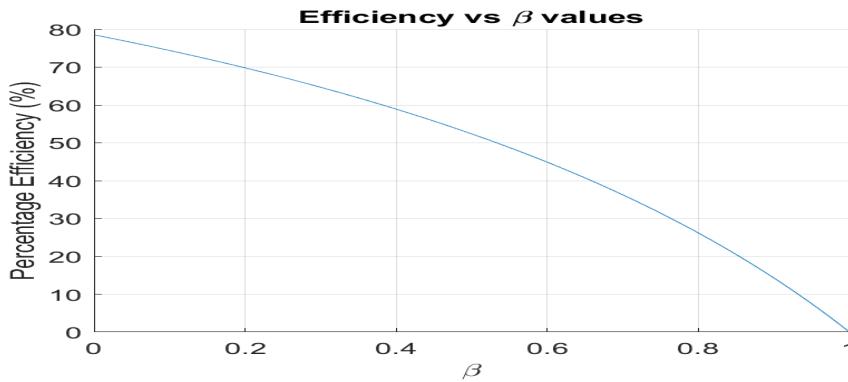

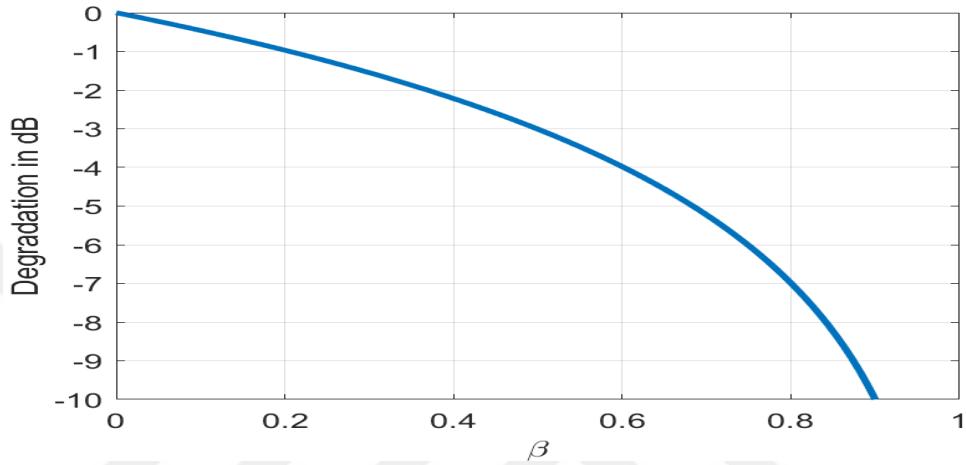

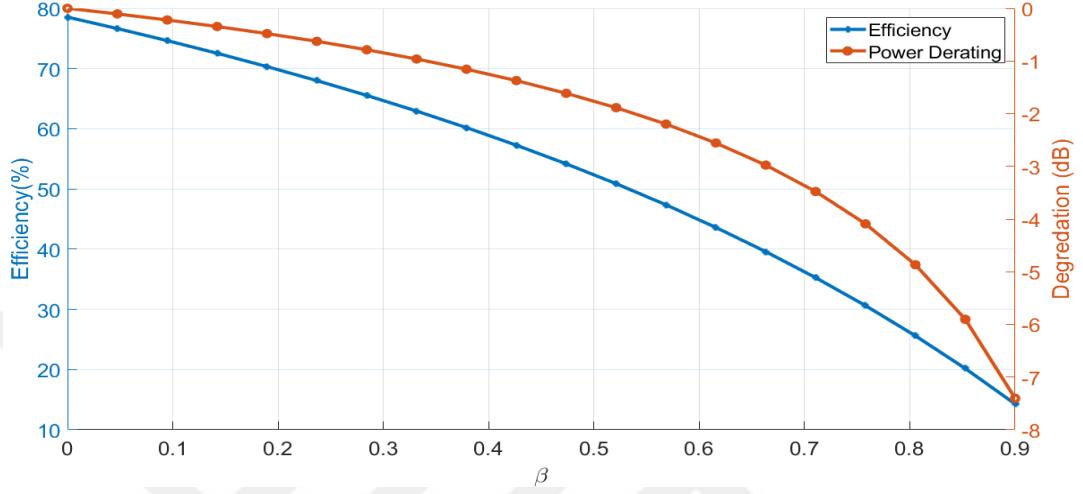

| Figure 3.4 $\beta$ vs efficiency . . . . .                                                                                                         | 46 |

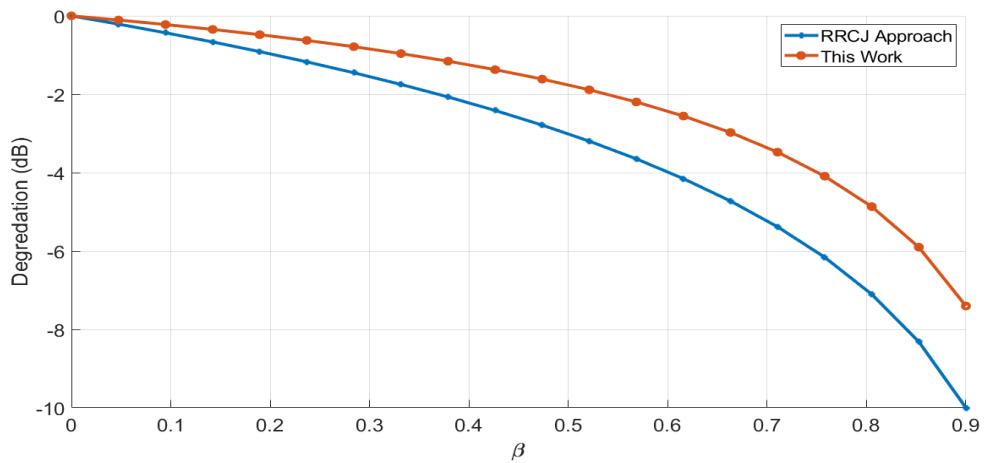

| Figure 3.5 $\beta$ vs power degradation curve. . . . .                                                                                             | 47 |

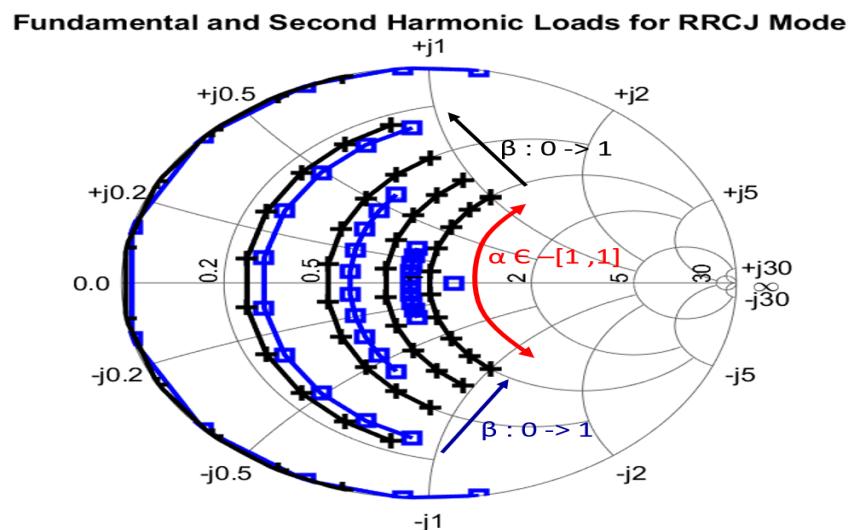

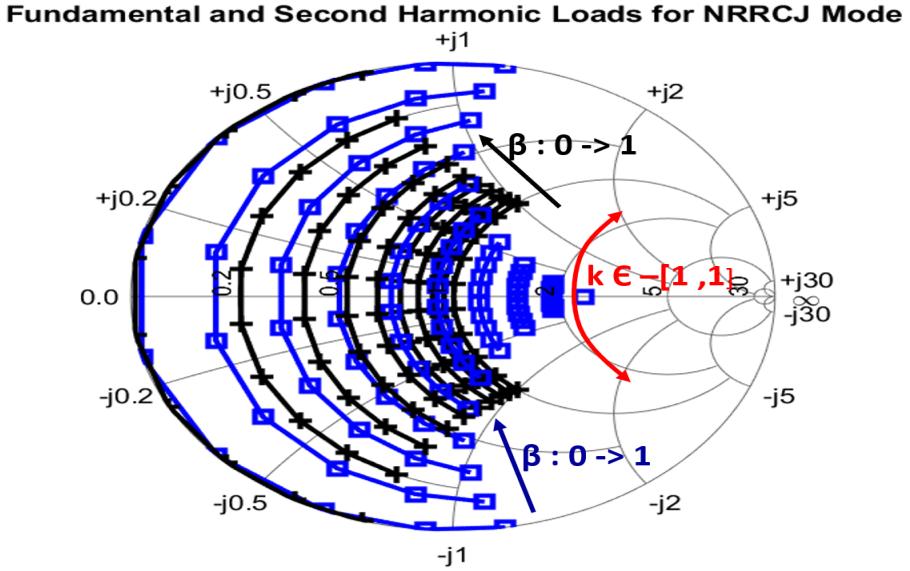

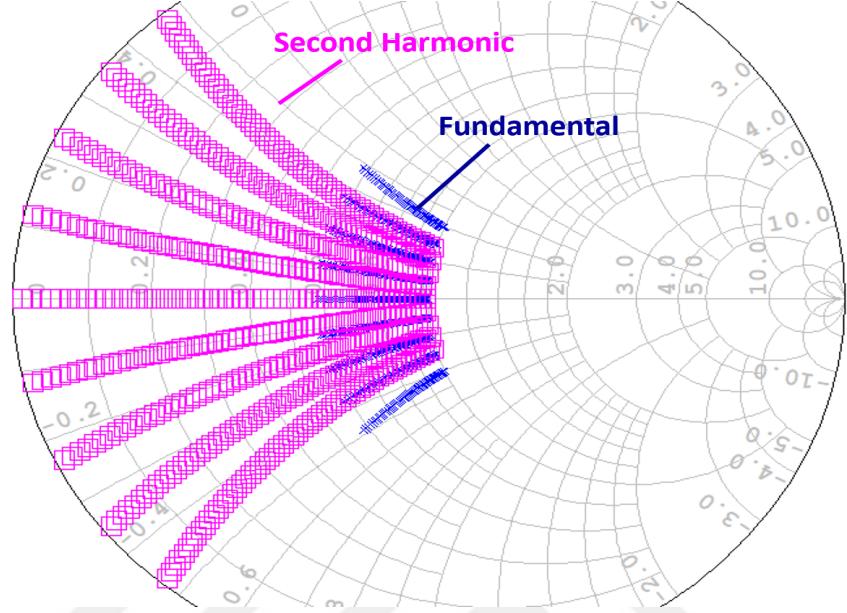

| Figure 3.6 $\beta$ and $\alpha$ swept for fundamental and harmonic impedances(black "+" : fundamental, blue "□" : second harmonic loads) . . . . . | 47 |

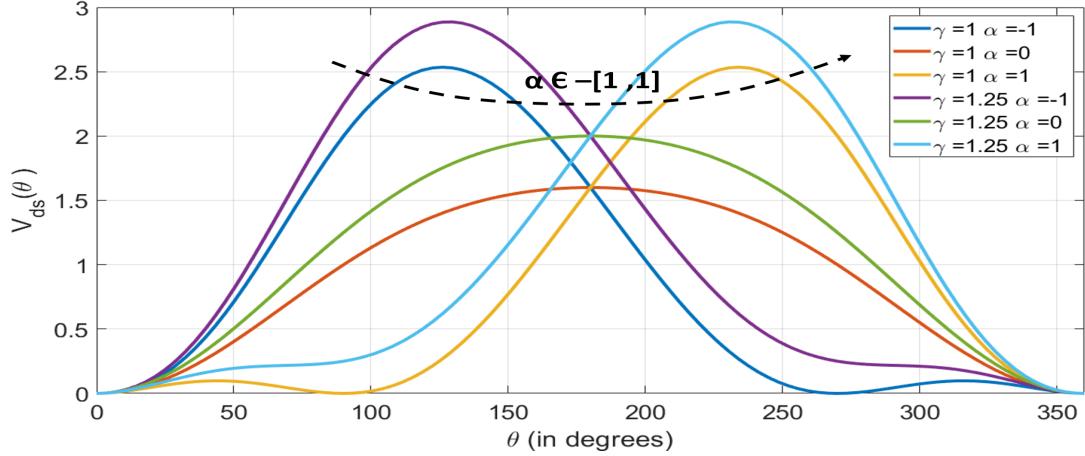

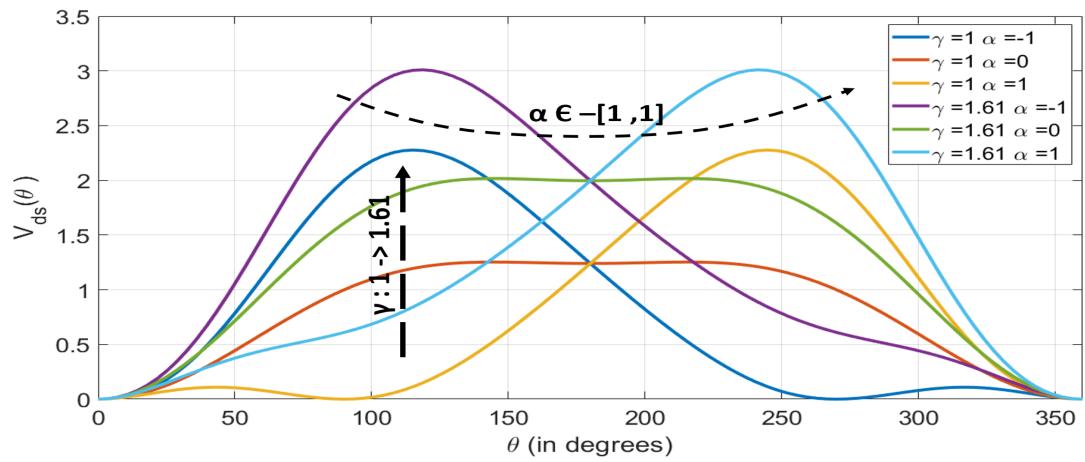

| Figure 3.7 Family of voltage curves for ERCB/J modes . . . . .                                                                                     | 50 |

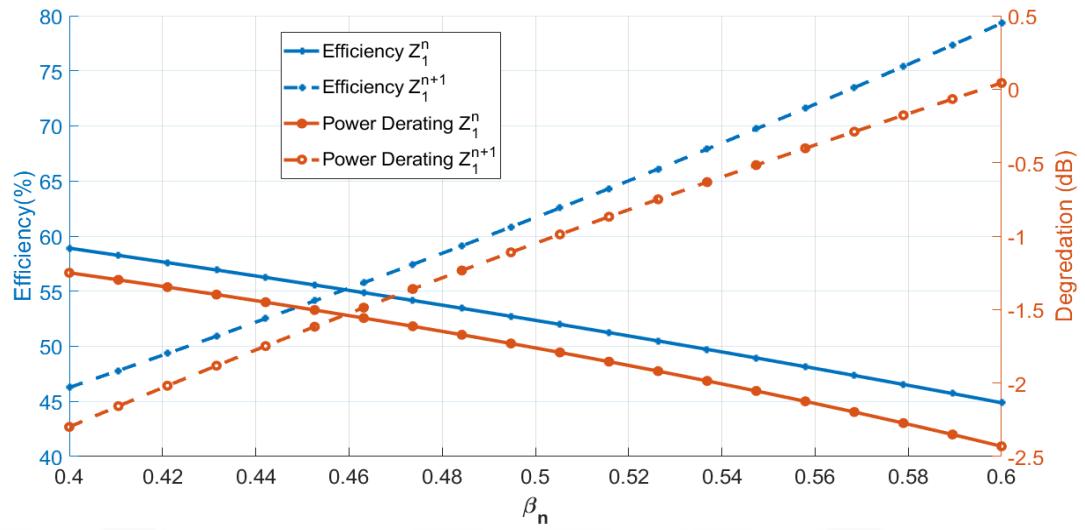

| Figure 3.8 Efficiency and power derating dependence on $\beta$ . . . . .                                                                           | 53 |

| Figure 3.9 Power derating curve comparison with RRCJ and our NRRCJ approach . . . . .                                                              | 53 |

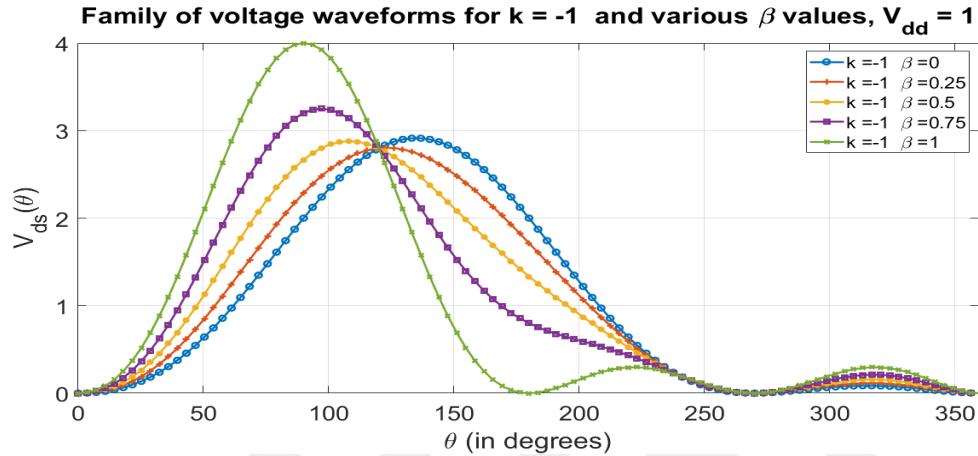

| Figure 3.10 Family of voltage waveforms for $k = -1$ and $\beta$ swept over $[0,1].(V_{dd} = 1)$ . . . . .                                         | 54 |

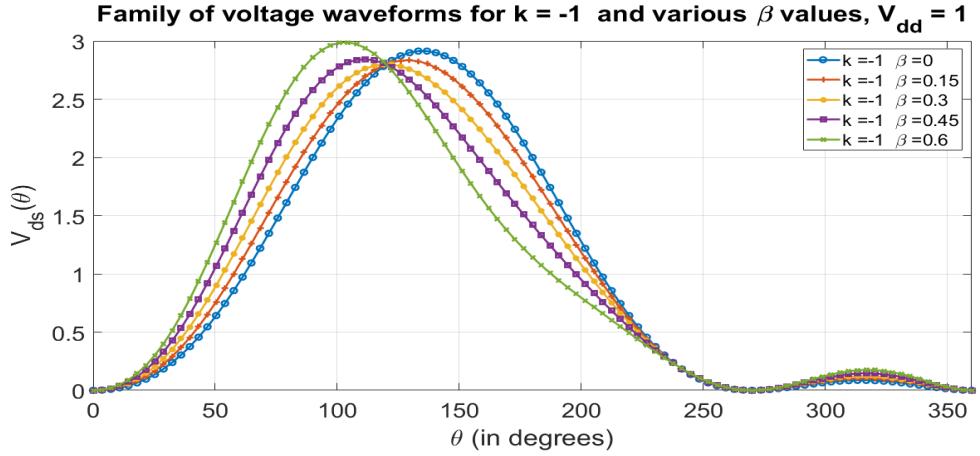

| Figure 3.11 Family of voltage waveforms for $k = -1$ and $\beta$ swept over $[0,6].(V_{dd} = 1)$ . . . . .                                         | 55 |

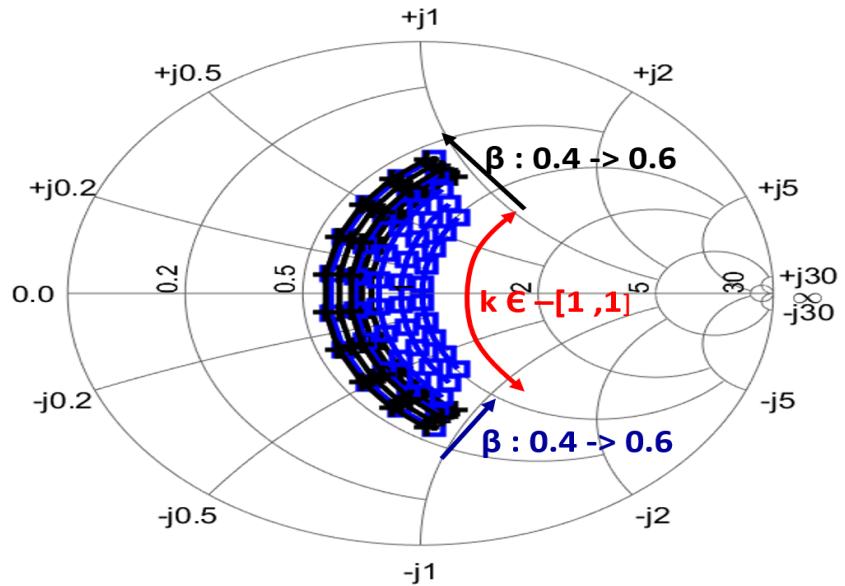

| Figure 3.12 $\beta$ and $k$ swept for fundamental and harmonic impedances(black "+" : fundamental, blue "□" : second harmonic loads) . . . . .     | 56 |

|                                                                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.13 Reduction in power and efficiency for fundamental impedance of successive octaves of NRRCJ mode. . . . .                                                      | 57 |

| Figure 3.14 $\beta \in [0.4, 0.6]$ and $k$ swept for fundamental and harmonic impedances(black "+" : fundamental, blue "□" : second harmonic loads . . . . .              | 57 |

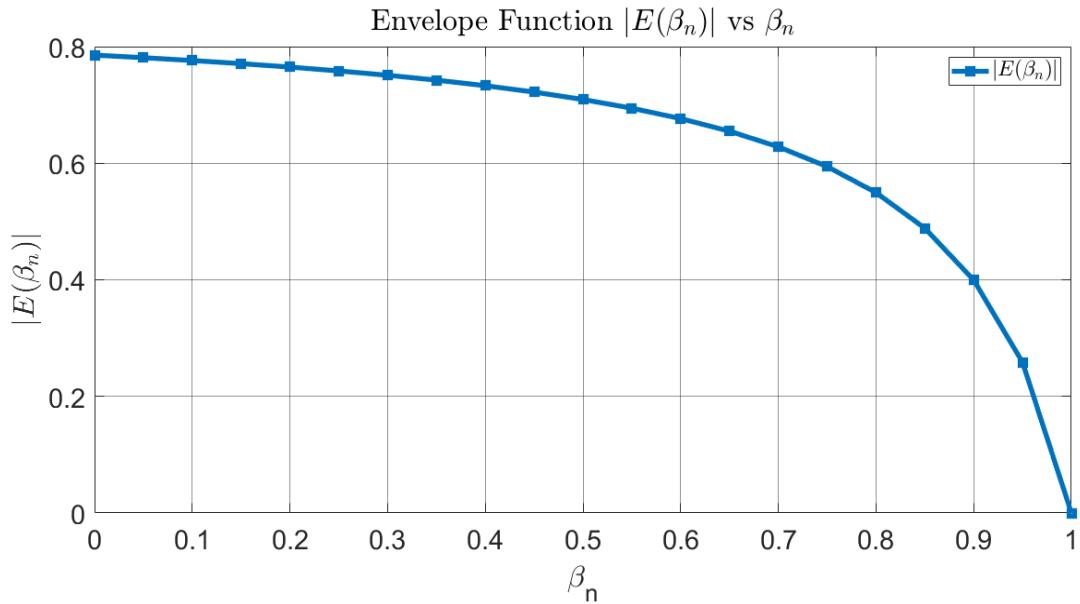

| Figure 4.1 $ E(\beta_n) $ vs $\beta_n$ . . . . .                                                                                                                          | 62 |

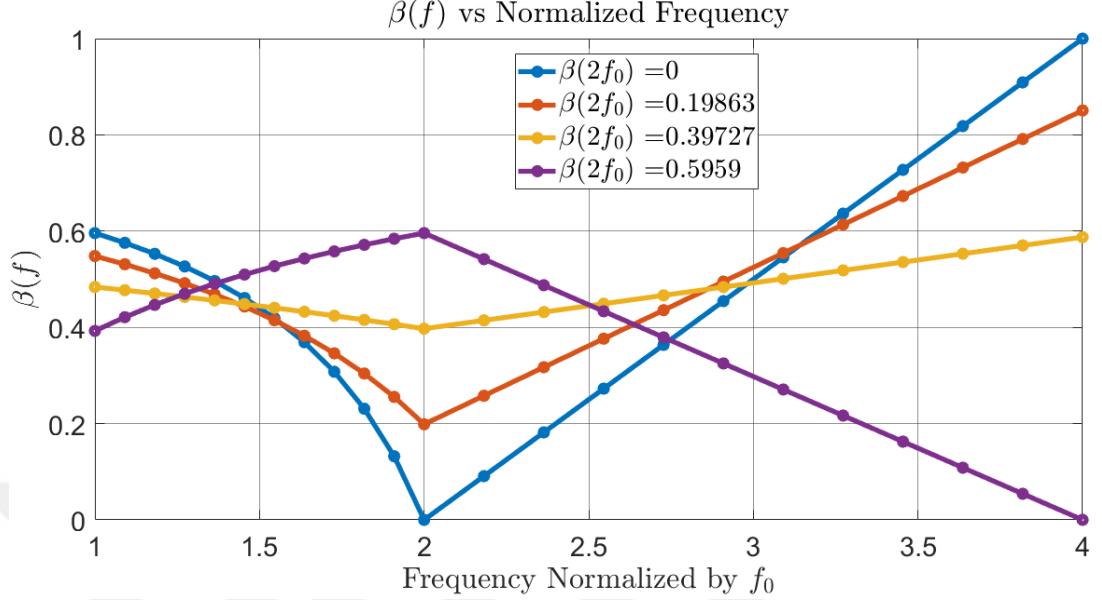

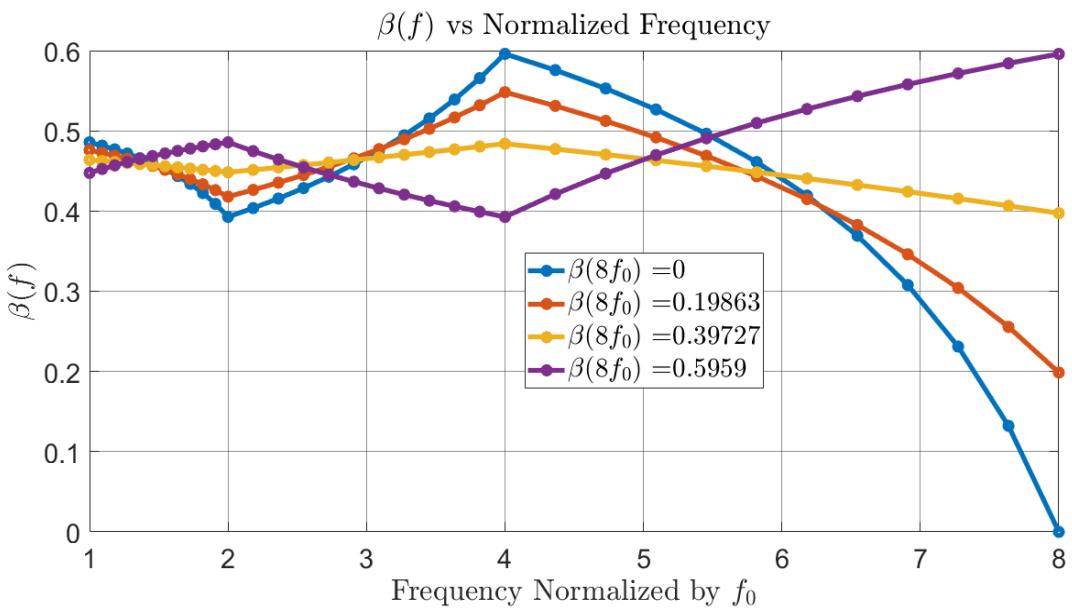

| Figure 4.2 $\beta(f)$ for different boundary conditions set at $\beta(2f_0)$ . . . . .                                                                                    | 63 |

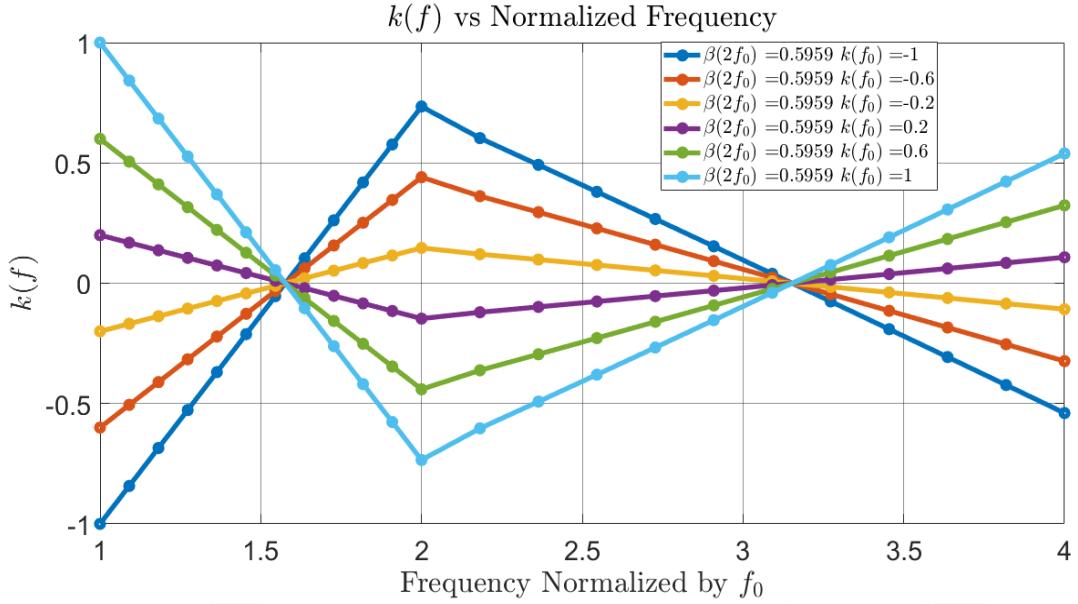

| Figure 4.3 $k(f)$ for different boundary conditions set at $\beta(2f_0) = 0.5959$ . .                                                                                     | 64 |

| Figure 4.4 $\beta(f)$ for different boundary conditions set at $\beta(8f_0)$ . . . . .                                                                                    | 65 |

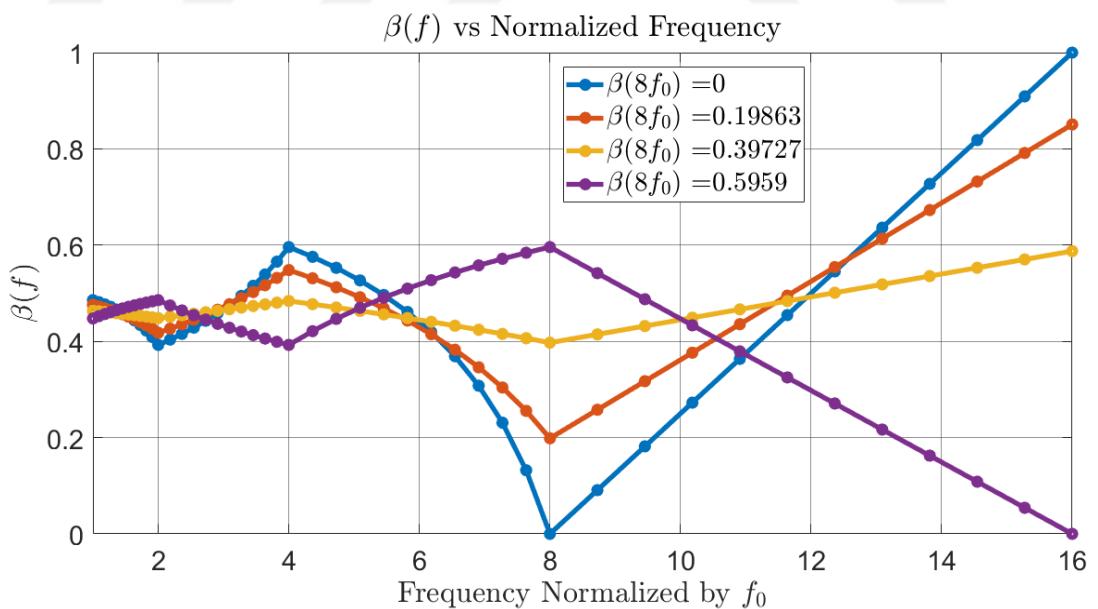

| Figure 4.5 $\beta(f)$ for different boundary conditions set at $\beta(8f_0)$ plotted in $[f_0, 16f_0]$ . . . . .                                                          | 65 |

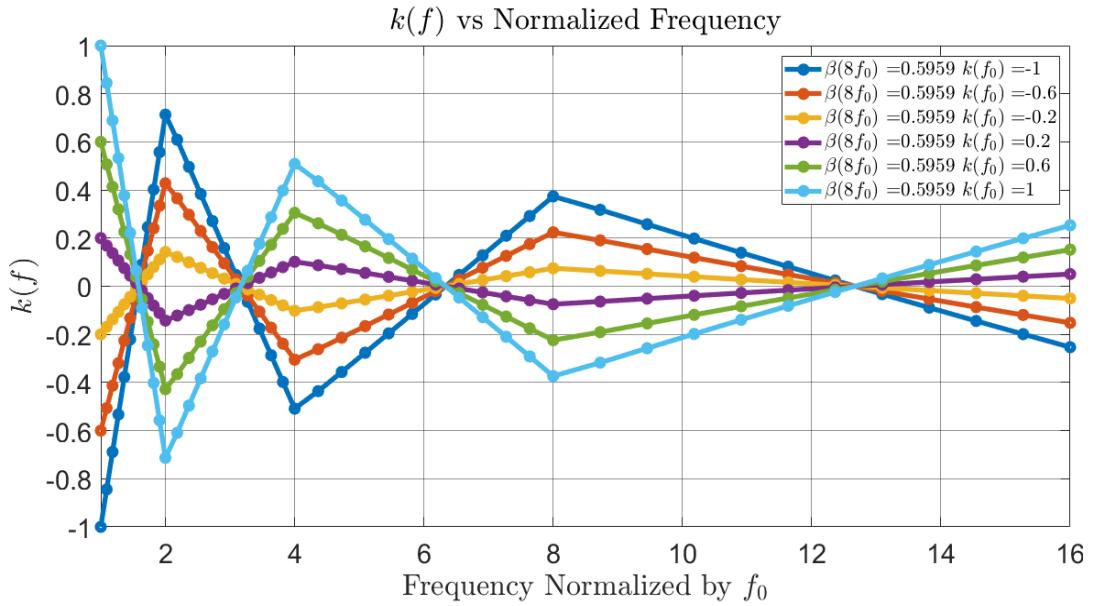

| Figure 4.6 $k(f)$ for different boundary conditions set at $\beta(8f_0) = 0.5959$ . .                                                                                     | 66 |

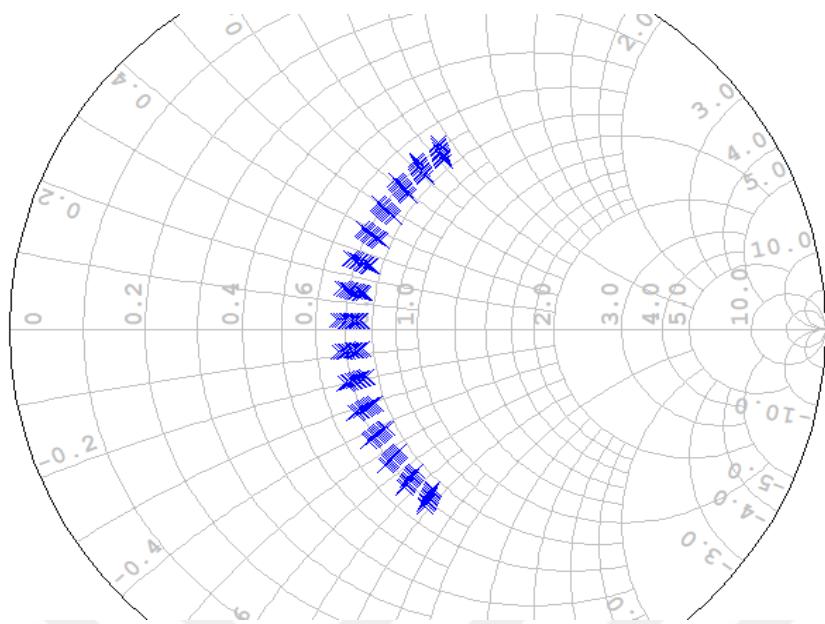

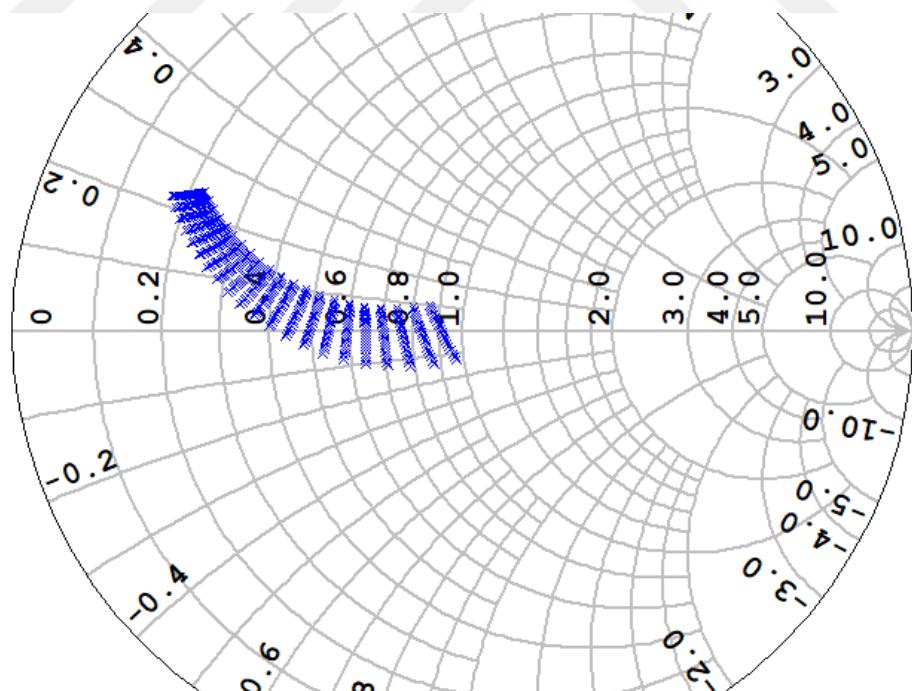

| Figure 4.7 First octave impedance space at intrinsic plane. ( $Z_0 = R_{opt}$ ) . . .                                                                                     | 68 |

| Figure 4.8 Second octave impedance space at intrinsic plane. ( $Z_0 = R_{opt}$ ) . .                                                                                      | 68 |

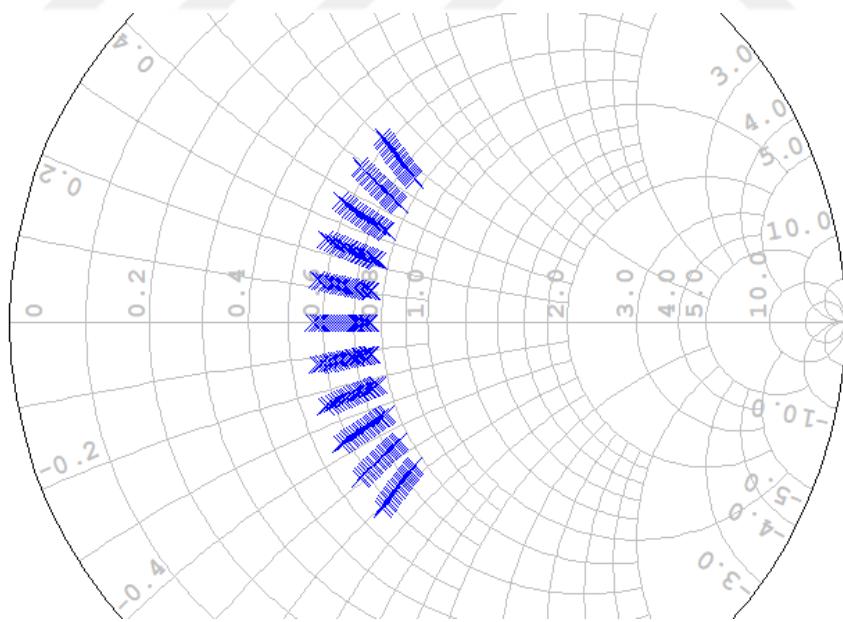

| Figure 4.9 Third octave fundamental and harmonic design space at intrinsic plane. ( $Z_0 = R_{opt}$ , blue "x" : fundamental, pink "□" : second harmonic loads) . . . . . | 69 |

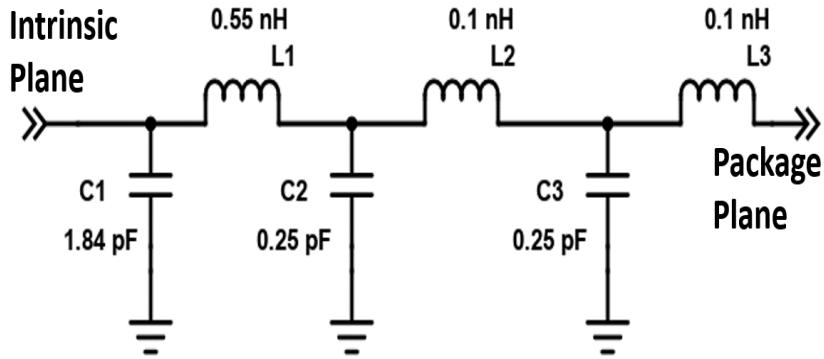

| Figure 4.10 Package parasitics equivalent circuit of CG2H40010F (modified from CGH40010F model) . . . . .                                                                 | 70 |

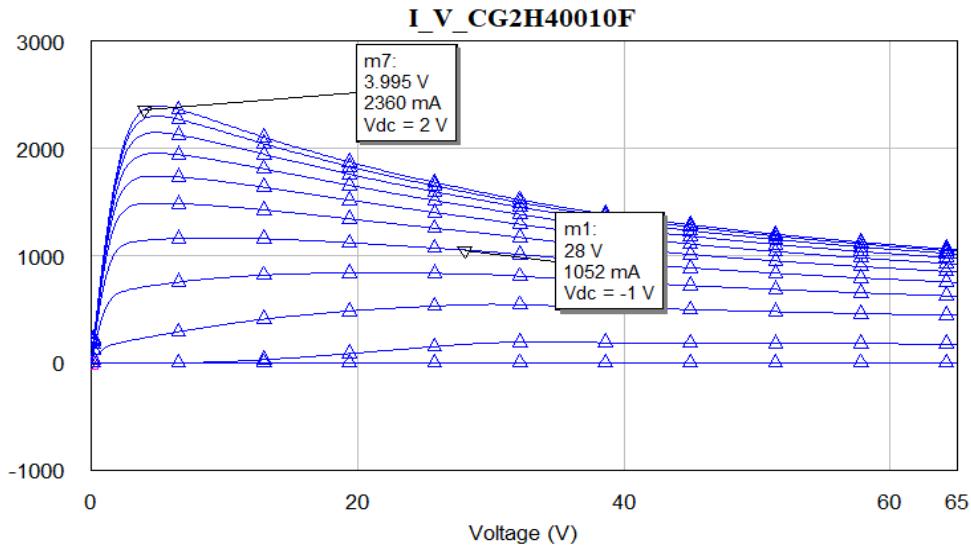

| Figure 4.11 Static I-V curve of CG2H40010F under condition of 25 $C^0$ base temperature with $R_{JC} = 8$ . . . . .                                                       | 70 |

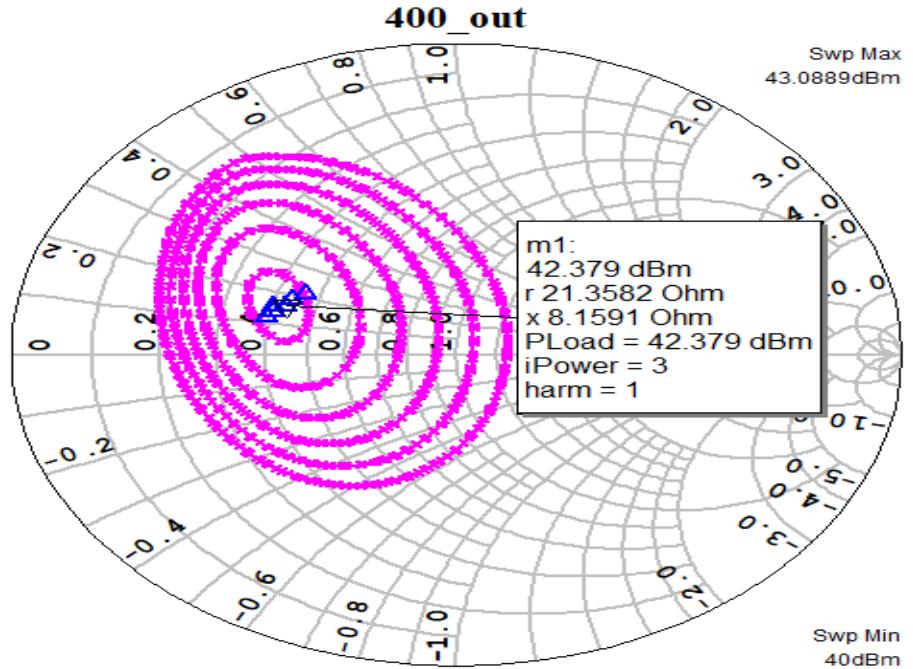

| Figure 4.12 0.4 GHz load contours at package plane with 0.5 dB increments from 40 to 42 dBm. . . . .                                                                      | 71 |

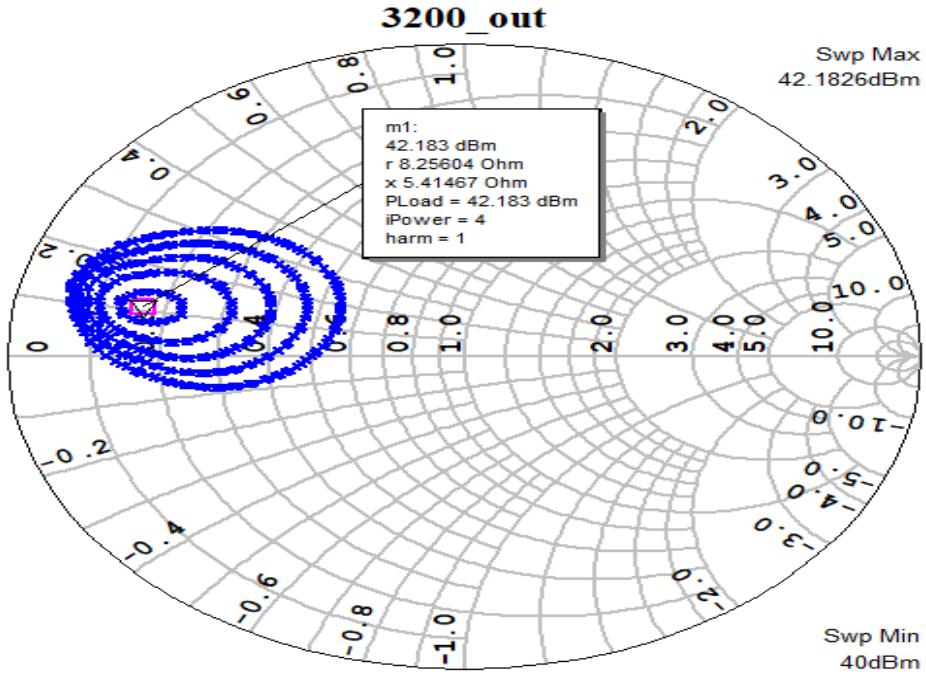

| Figure 4.13 3.2 GHz load contours with 0.5 dB increments from 40 to 42 dBm. 72                                                                                            |    |

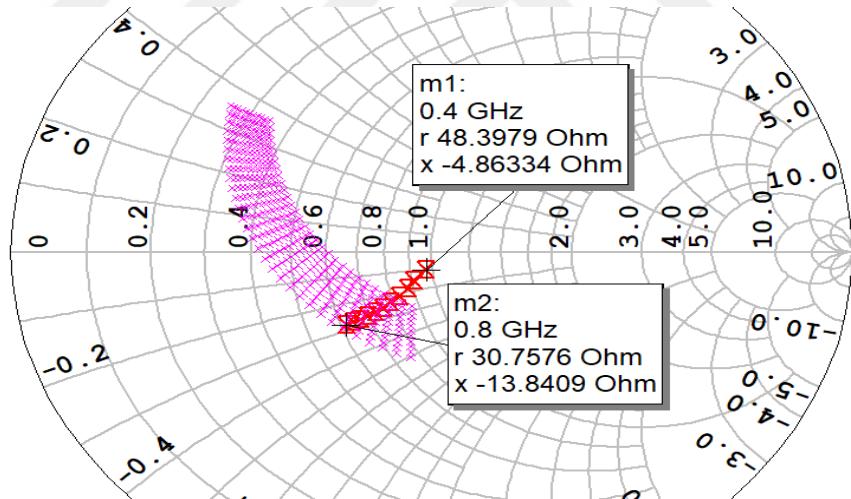

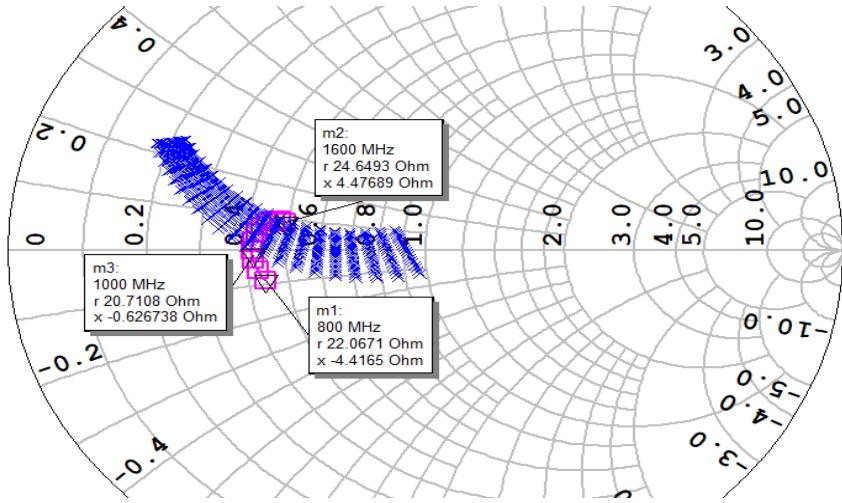

| Figure 4.14 First octave loads de-embedded at 800 MHz. . . . .                                                                                                            | 73 |

|                                                                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

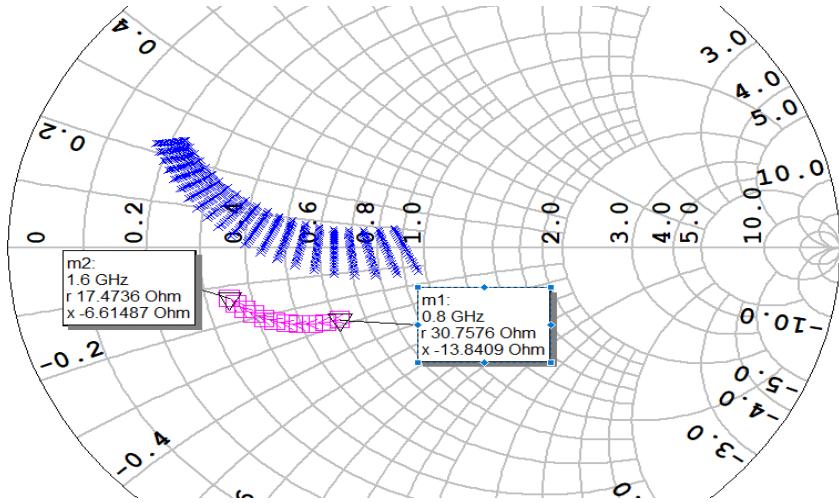

| Figure 4.15 Second octave loads de-embedded at 1600 MHz. . . . .                                                                                                       | 73 |

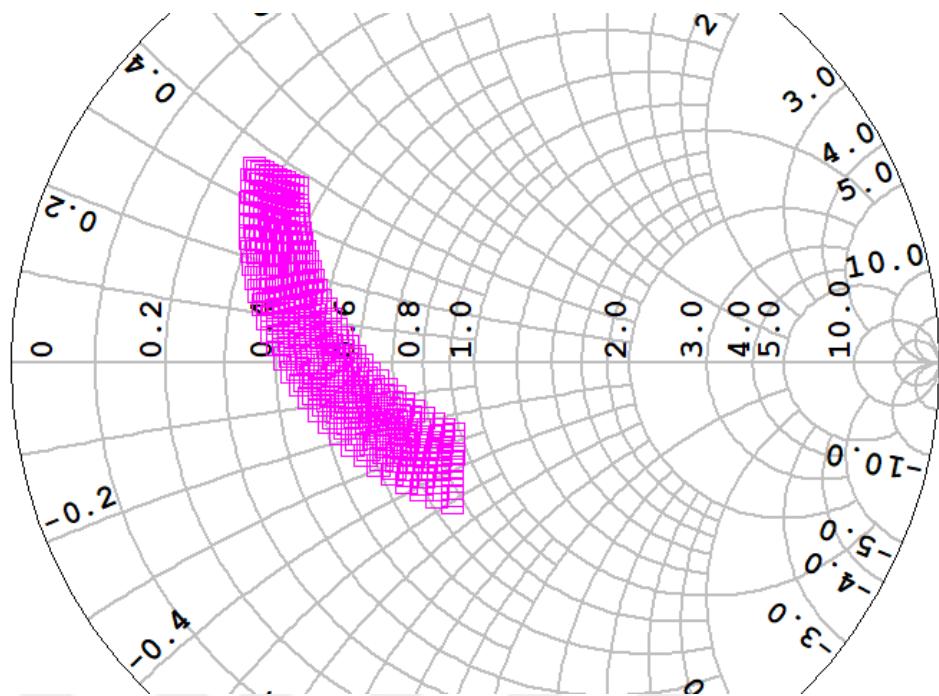

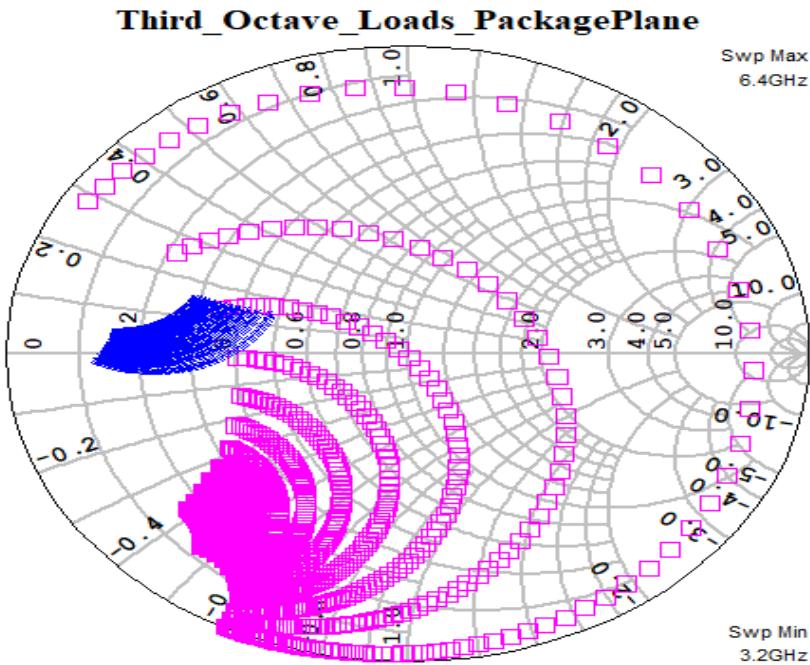

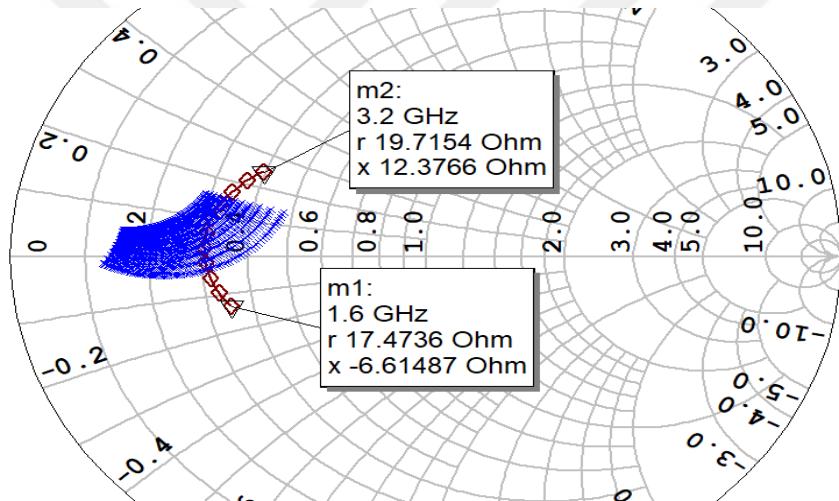

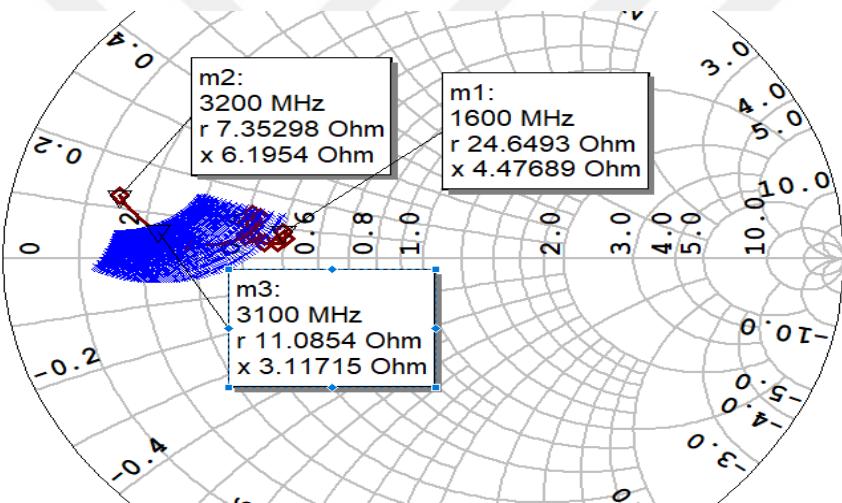

| Figure 4.16 Third octave loads de-embedded at 3200 MHz with second harmonic de-embedded at 6400 MHz(blue "x" : fundamental, pink "□" : second harmonic loads). . . . . | 74 |

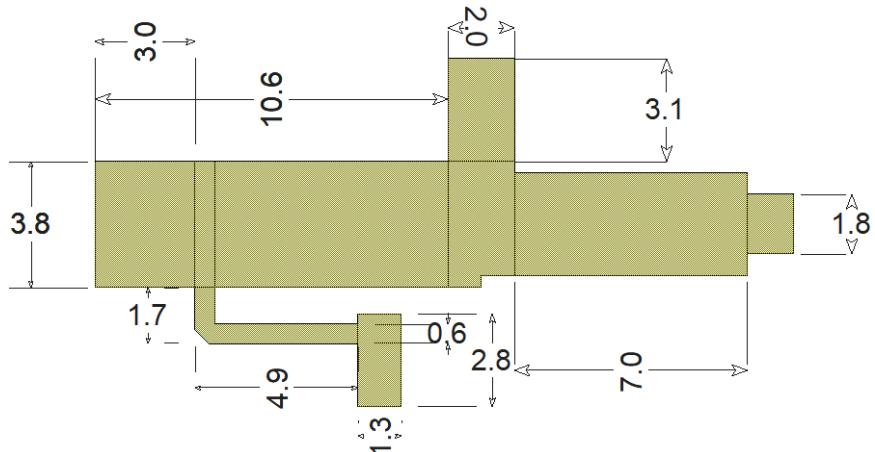

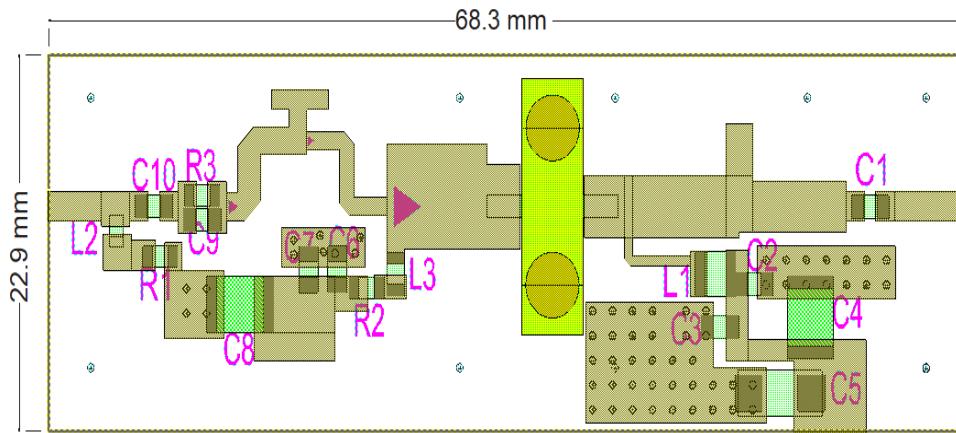

| Figure 4.17 Prototype 1 layout dimensions of the output matching (dimensions are in mm). . . . .                                                                       | 75 |

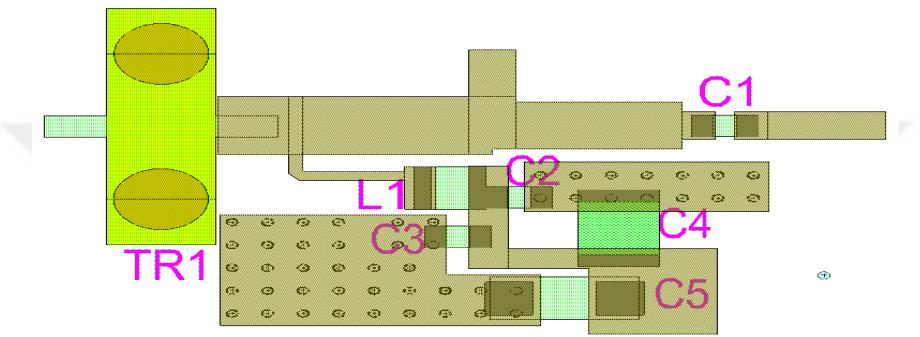

| Figure 4.18 Output matching layout with reference numbers of components. .                                                                                             | 76 |

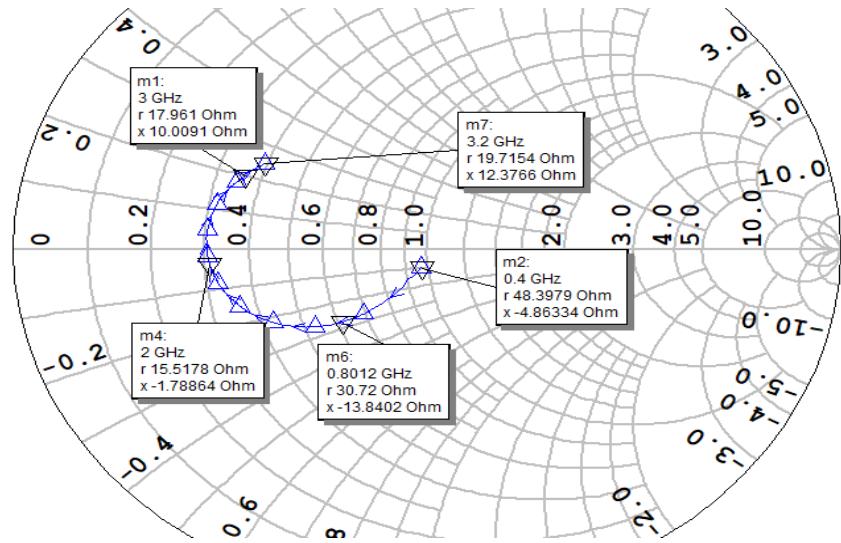

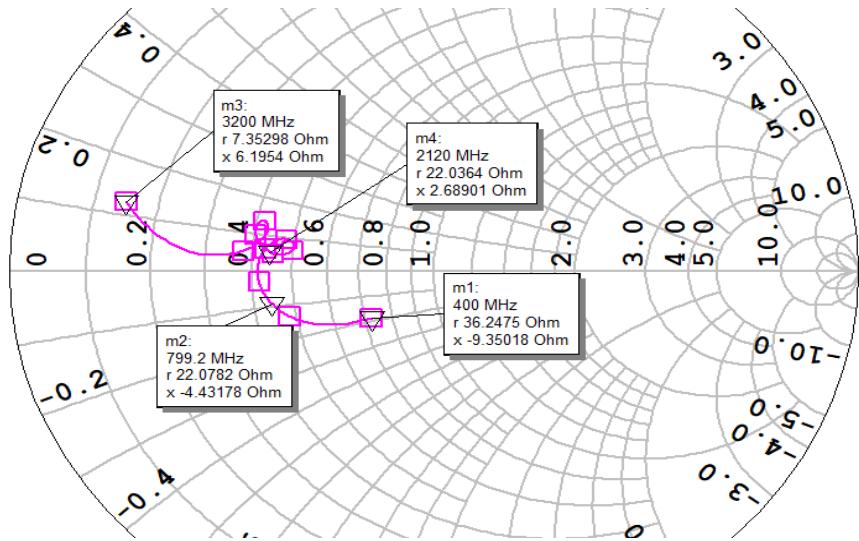

| Figure 4.19 Output impedance seen from the package plane( $Z_0 = 50\Omega$ ) . . .                                                                                     | 77 |

| Figure 4.20 Compared impedances at the package plane for de-embedded first octave space at 800 MHz.( $Z_0 = 50\Omega$ ) . . . . .                                      | 77 |

| Figure 4.21 Compared impedances at the package plane for de-embedded second octave space at 1600 MHz.( $Z_0 = 50\Omega$ ) . . . . .                                    | 78 |

| Figure 4.22 Compared impedances at the package plane for de-embedded third octave space at 3200 MHz.( $Z_0 = 50\Omega$ ) . . . . .                                     | 78 |

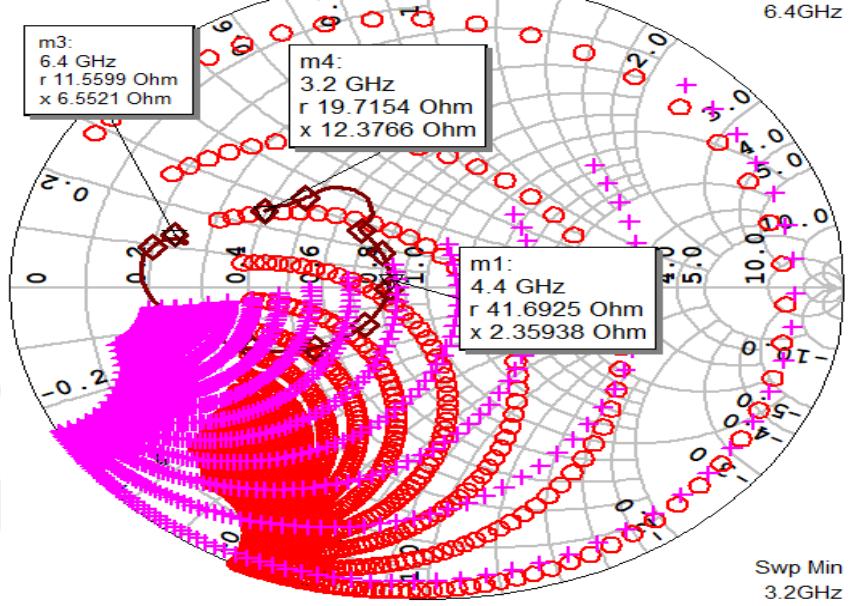

| Figure 4.23 Third octave harmonic space comparison.(red "○": 6.4 GHz, pink "+": 4.4 GHz, brown "◇": matching circuit) ( $Z_0 = 50\Omega$ ) . . . . .                   | 79 |

| Figure 4.24 Full layout and occupied space for matching network of prototype I . . . . .                                                                               | 80 |

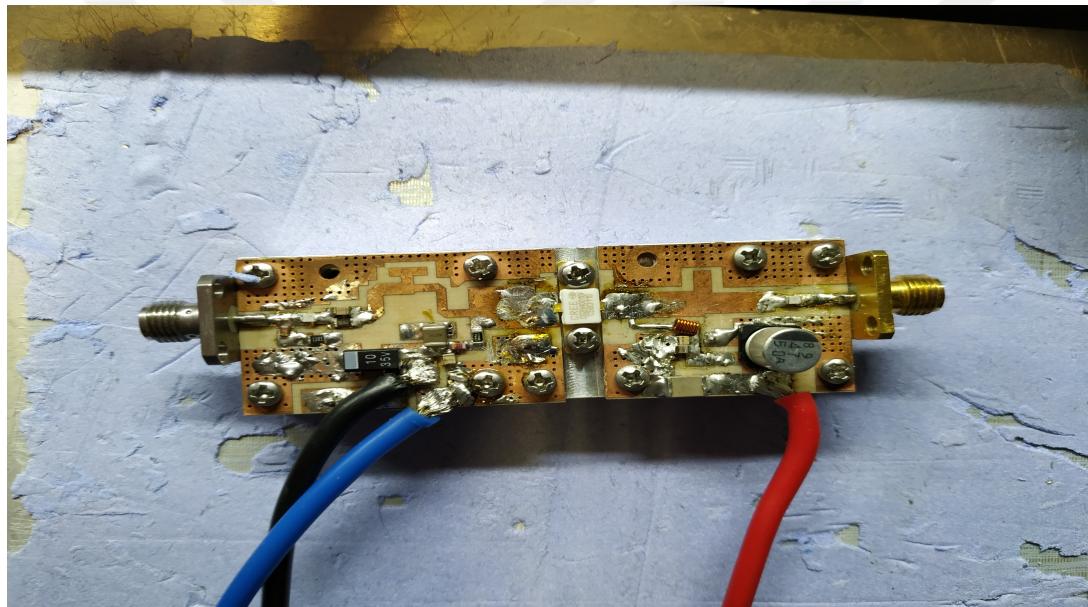

| Figure 4.25 First fabricated version (small version) (Dimension are 68 mm x 23 mm) . . . . .                                                                           | 80 |

| Figure 4.26 Manufactured connectorized version . . . . .                                                                                                               | 81 |

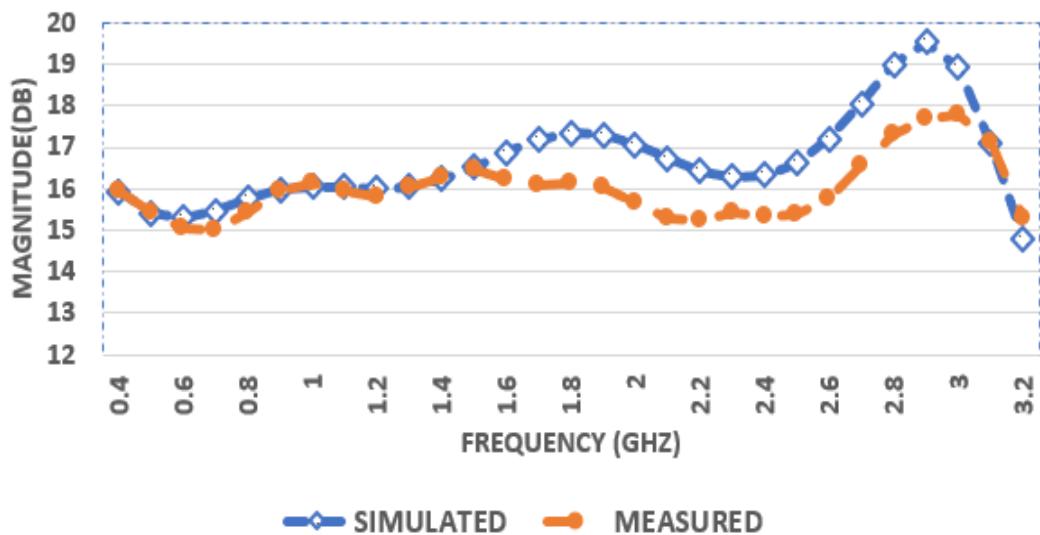

| Figure 4.27 Simulated and measured small-signal gain . . . . .                                                                                                         | 82 |

| Figure 4.28 Simulated and measured S11 . . . . .                                                                                                                       | 82 |

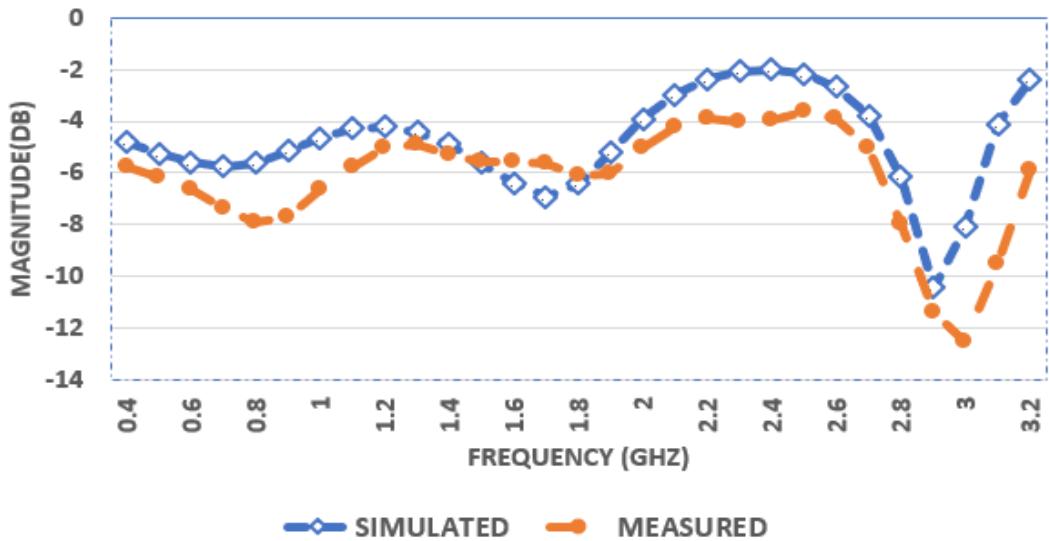

| Figure 4.29 Large Signal Measurement Setup . . . . .                                                                                                                   | 83 |

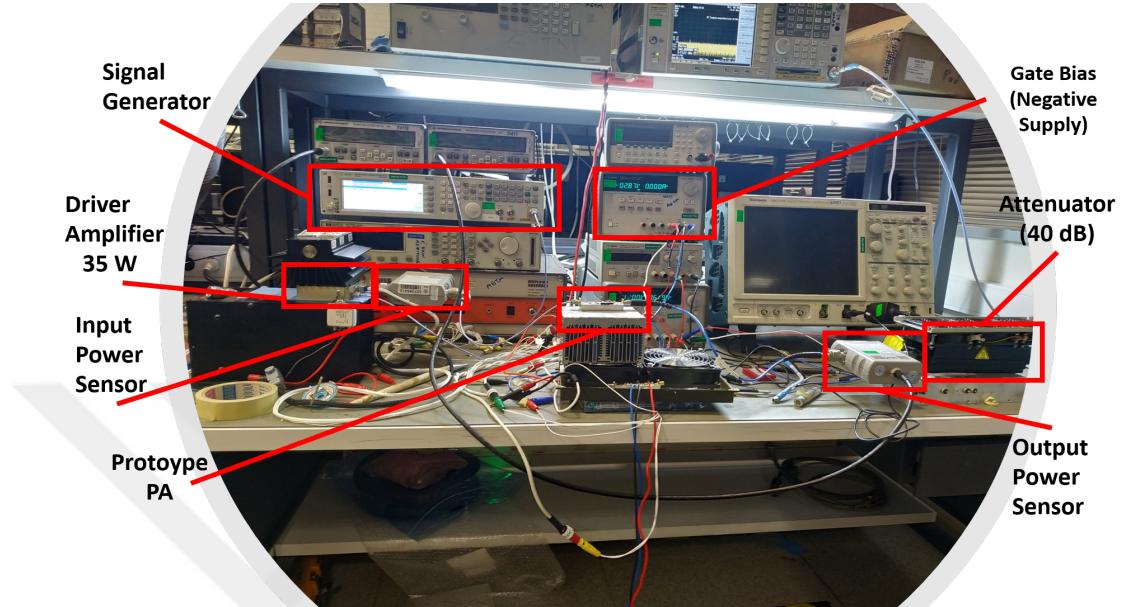

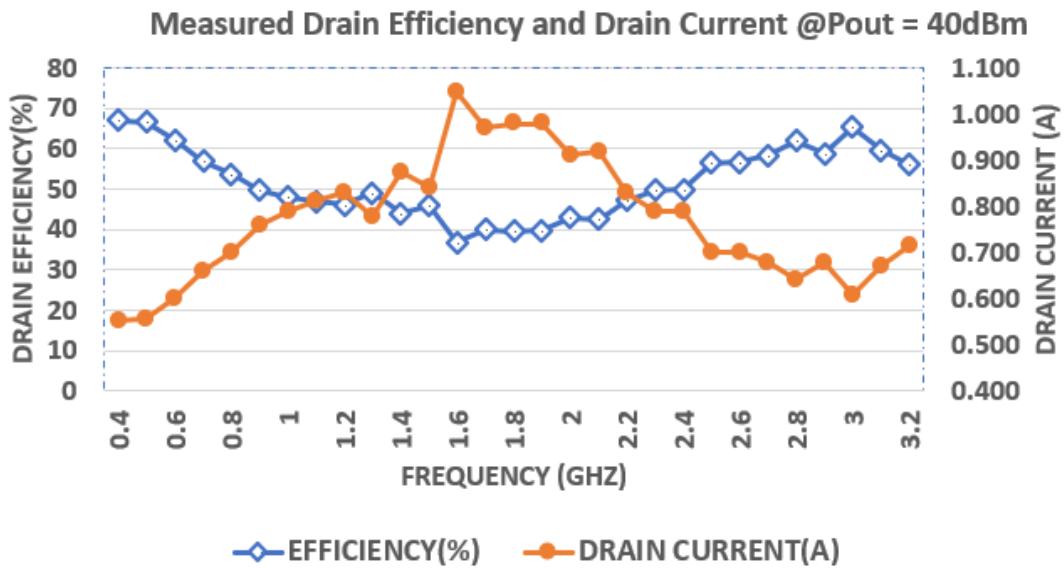

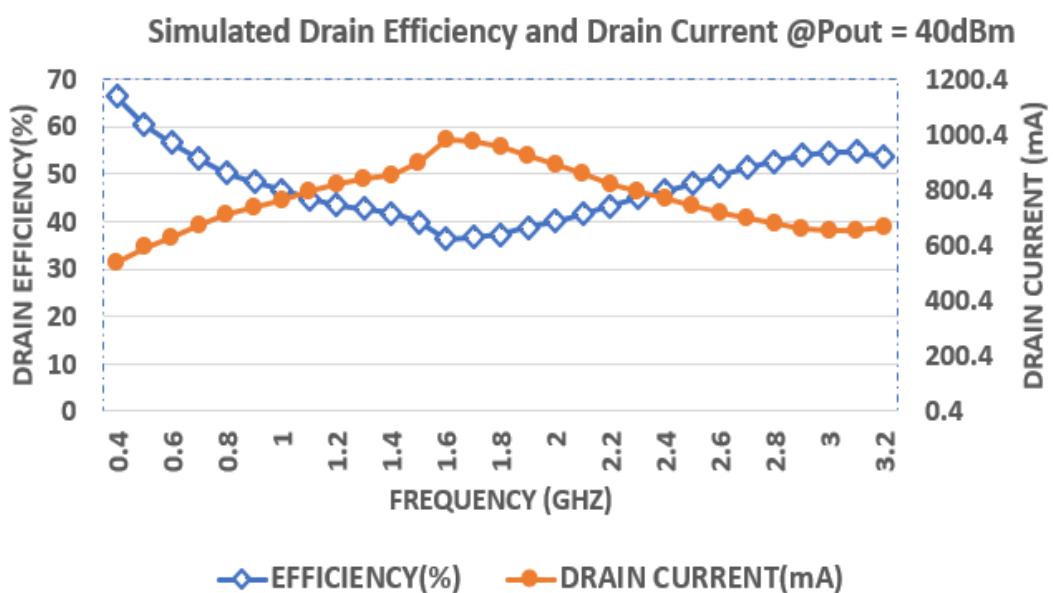

| Figure 4.30 Measured drain efficiency and current for $P_{out} = 40dBm$ . . . . .                                                                                      | 84 |

|             |                                                                                                                                             |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.31 | Simulated drain efficiency and current for $P_{out} = 40dBm$ . . . . .                                                                      | 84 |

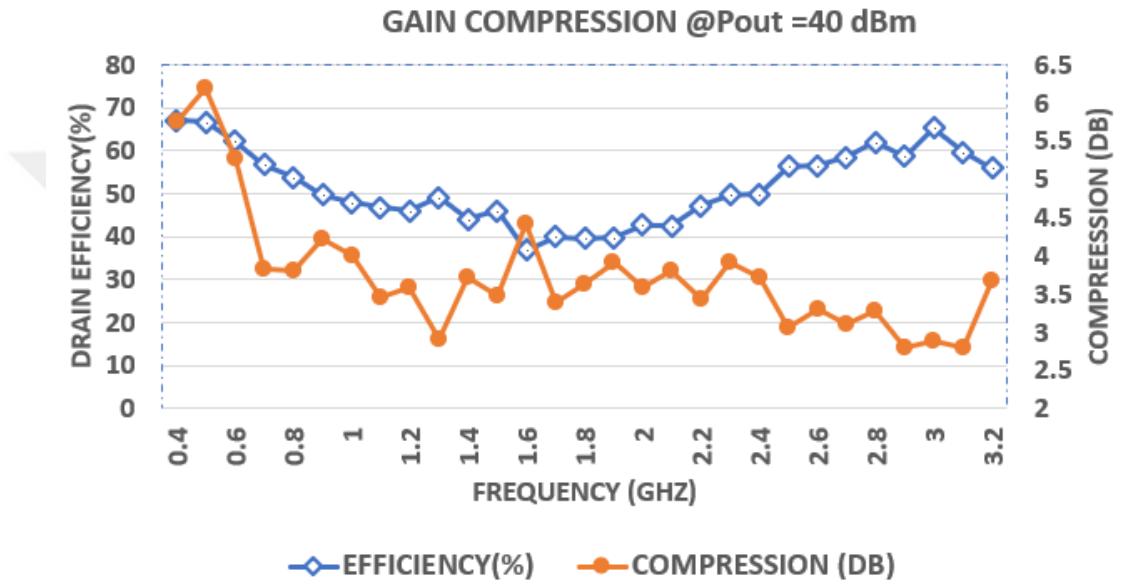

| Figure 4.32 | Measured gain compression vs drain efficiency for $P_{out} = 40dBm$                                                                         | 85 |

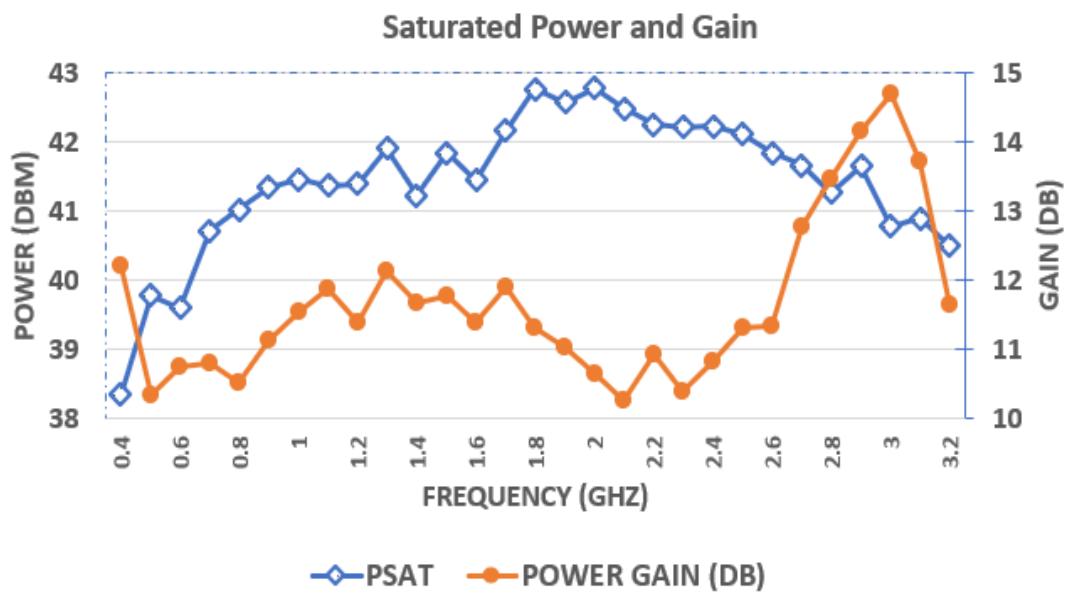

| Figure 4.33 | Measured saturated output power and gain . . . . . . . . . . .                                                                              | 86 |

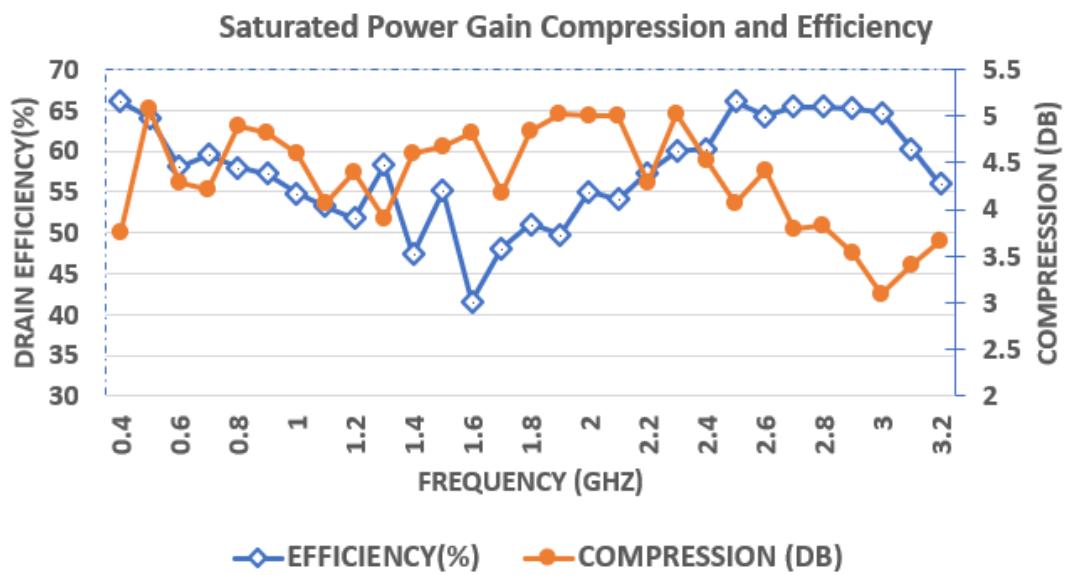

| Figure 4.34 | Measured drain efficiency and gain compression at saturated output power . . . . . . . . . . .                                              | 86 |

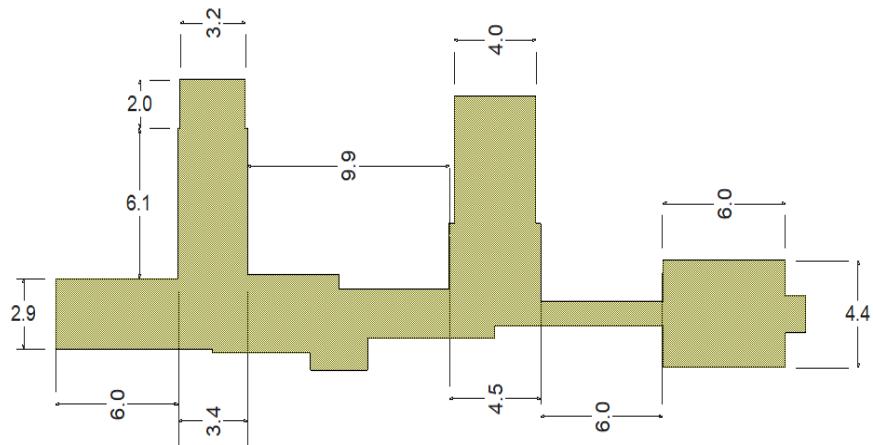

| Figure 4.35 | Prototype 2 output layout rough dimensions (mm) . . . . .                                                                                   | 87 |

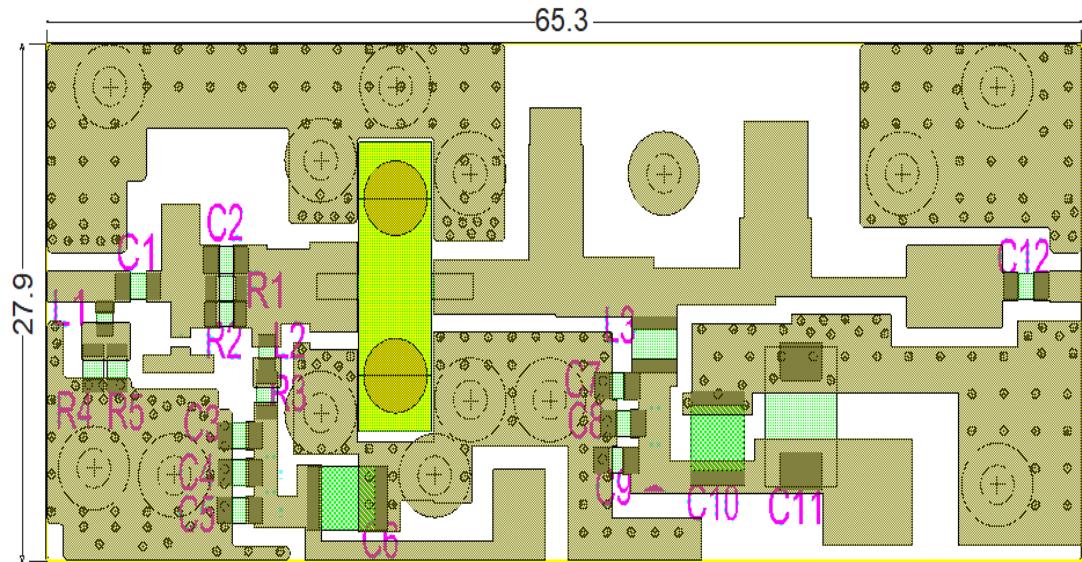

| Figure 4.36 | Prototype 2 full layout and dimensions(mm) . . . . . . . . .                                                                                | 88 |

| Figure 4.37 | Output impedance of prototype 2 ( $Z_0 = 50\Omega$ ) . . . . .                                                                              | 89 |

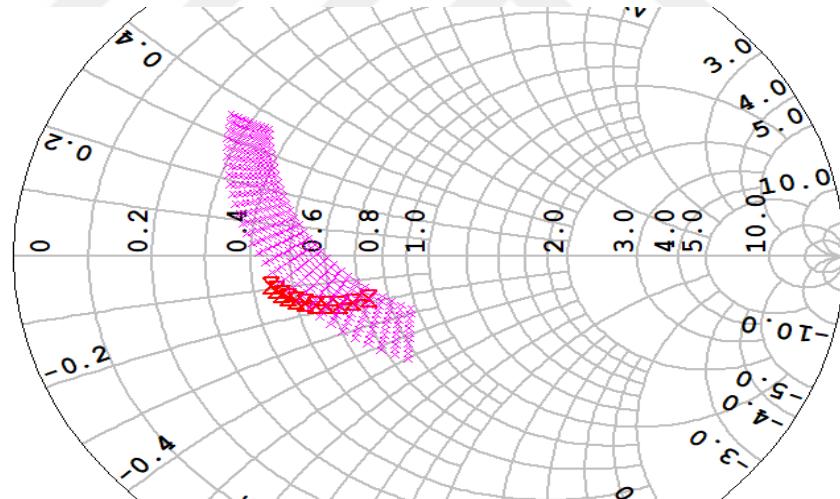

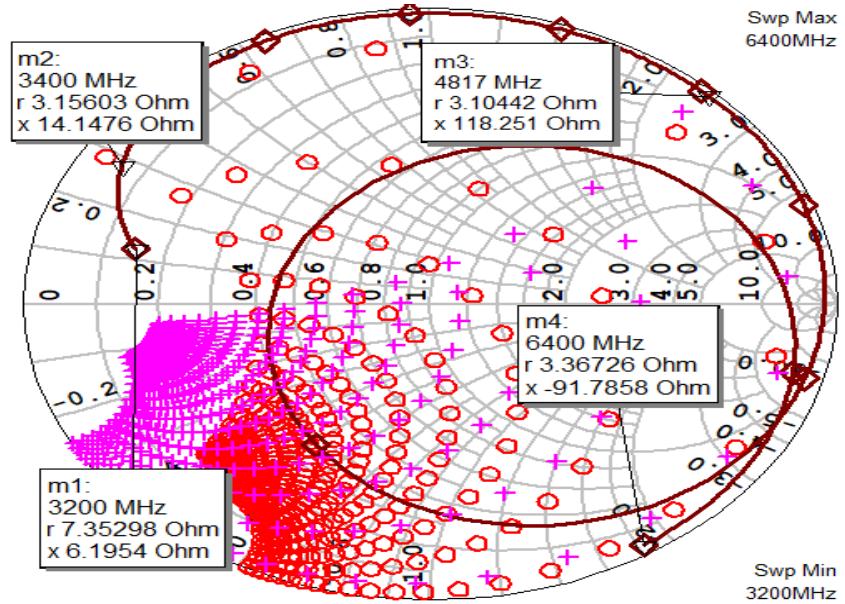

| Figure 4.38 | Prototype 2 first octave impedance and NRRCJ space de-embedded at 800 MHz. ( $Z_0 = 50\Omega$ ) . . . . . . . . . . .                       | 89 |

| Figure 4.39 | Prototype 2 second octave impedance and NRRCJ space de-embedded at 1600 MHz. ( $Z_0 = 50\Omega$ ) . . . . . . . . . . .                     | 90 |

| Figure 4.40 | Prototype 2 third octave impedance and NRRCJ space de-embedded at 3200 MHz. ( $Z_0 = 50\Omega$ ) . . . . . . . . . . .                      | 90 |

| Figure 4.41 | P2 third octave harmonic space comparison.(red "o": 6.4 GHz, pink "+": 4.4 GHz, brown "◇": matching circuit) ( $Z_0 = 50\Omega$ ) . . . . . | 91 |

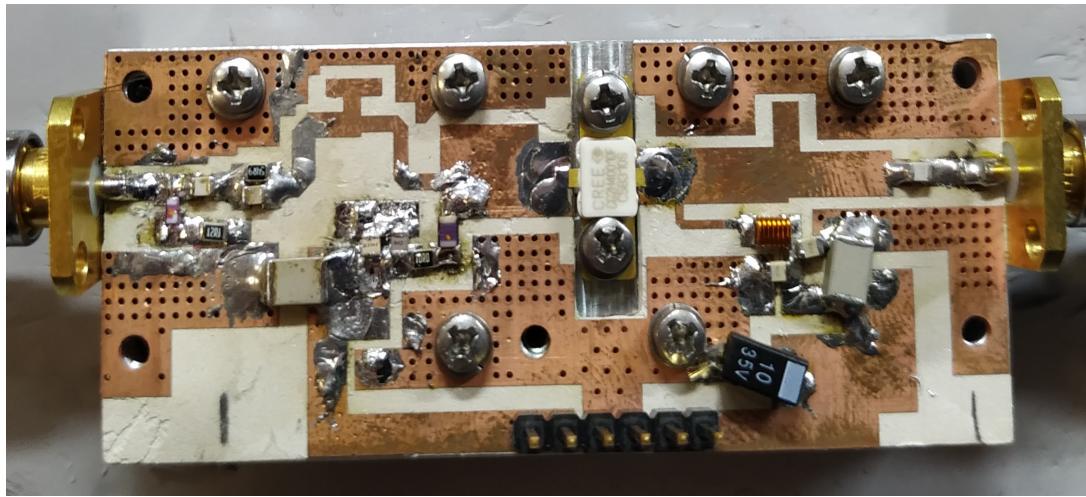

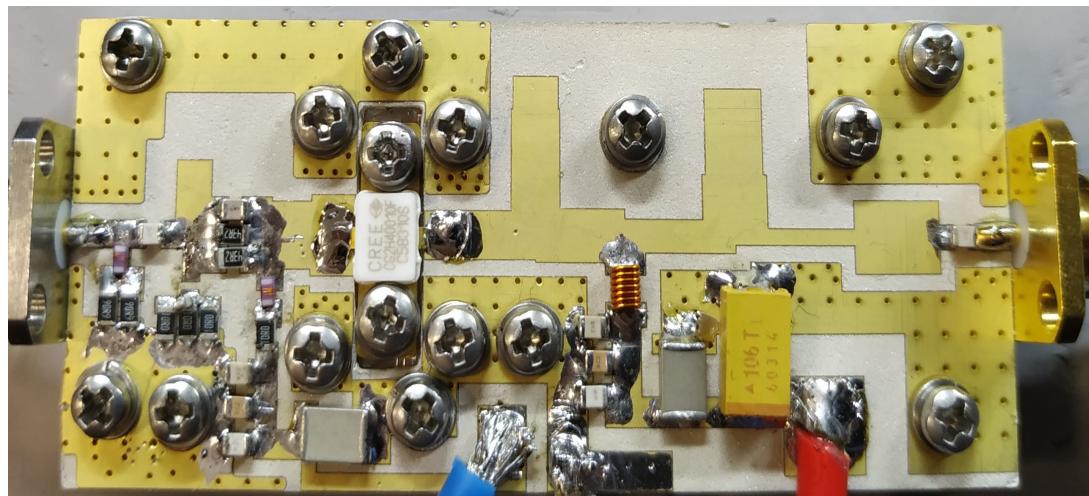

| Figure 4.42 | Prototype 2 assembled photograph . . . . . . . . . . .                                                                                      | 92 |

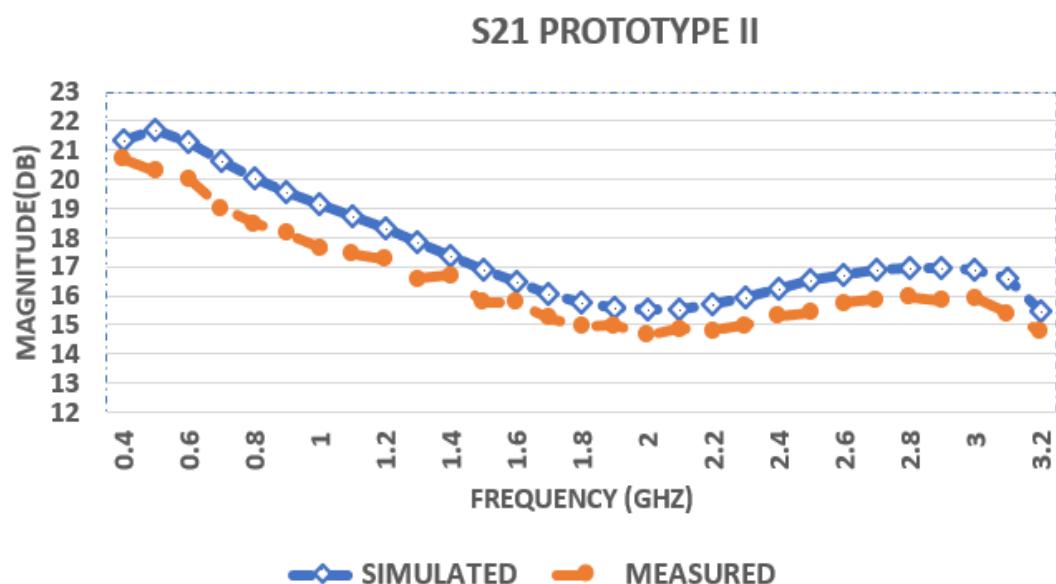

| Figure 4.43 | Measured and simulated gain of prototype 2 . . . . .                                                                                        | 92 |

| Figure 4.44 | Measured and simulated return loss of prototype 2 . . . . .                                                                                 | 93 |

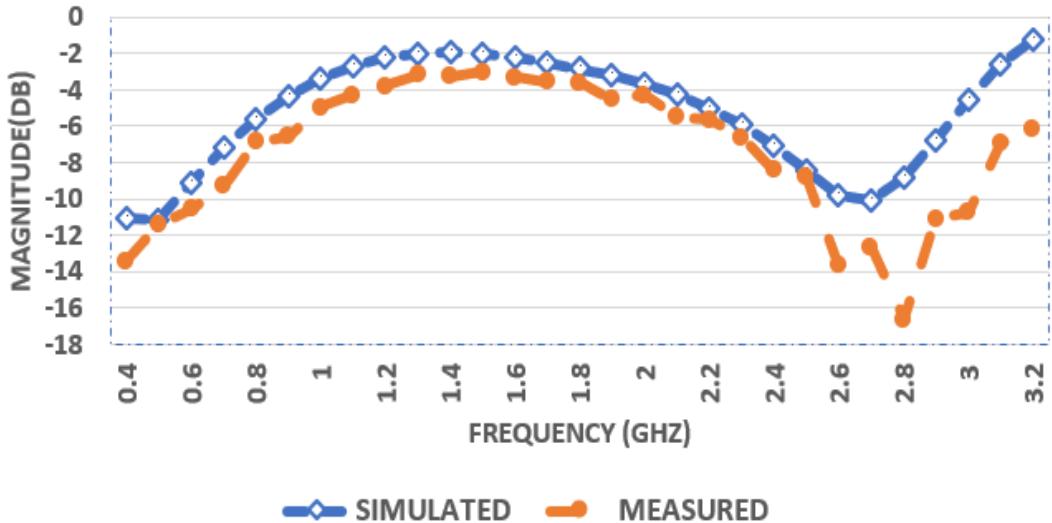

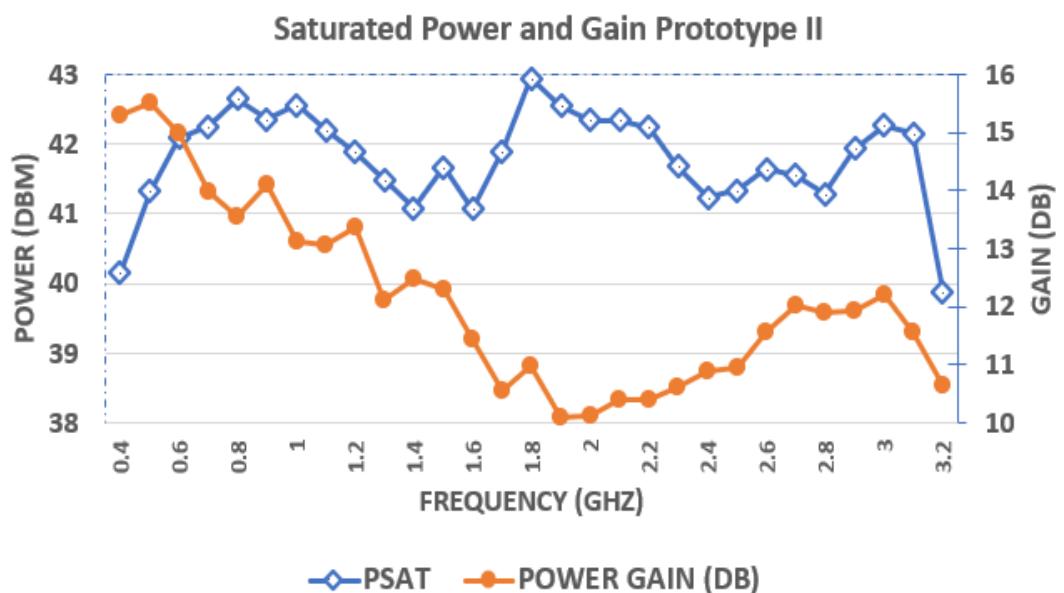

| Figure 4.45 | Measured saturated output power and gain of prototype II . . . . .                                                                          | 94 |

| Figure 4.46 | Measured saturated gain compression and drain efficiency of prototype II . . . . . . . . . . .                                              | 94 |

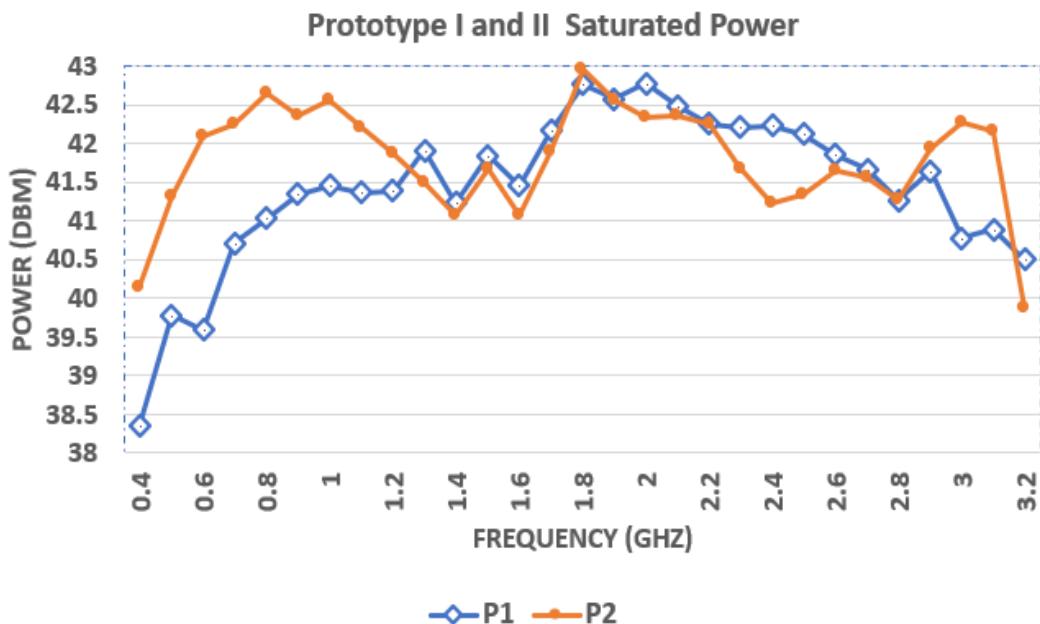

| Figure 4.47 | Measured saturated output power results of prototypes . . . . .                                                                             | 95 |

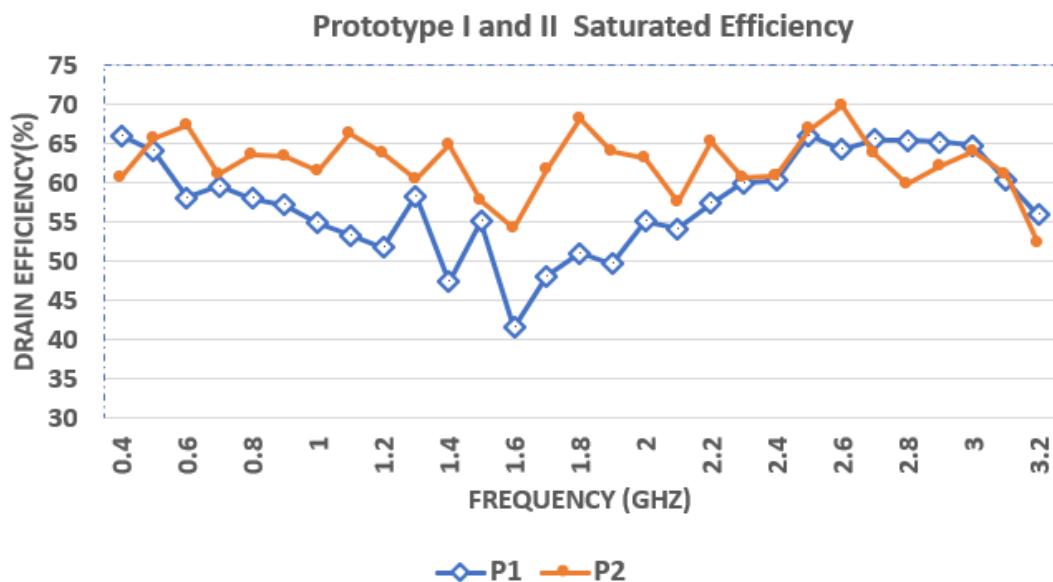

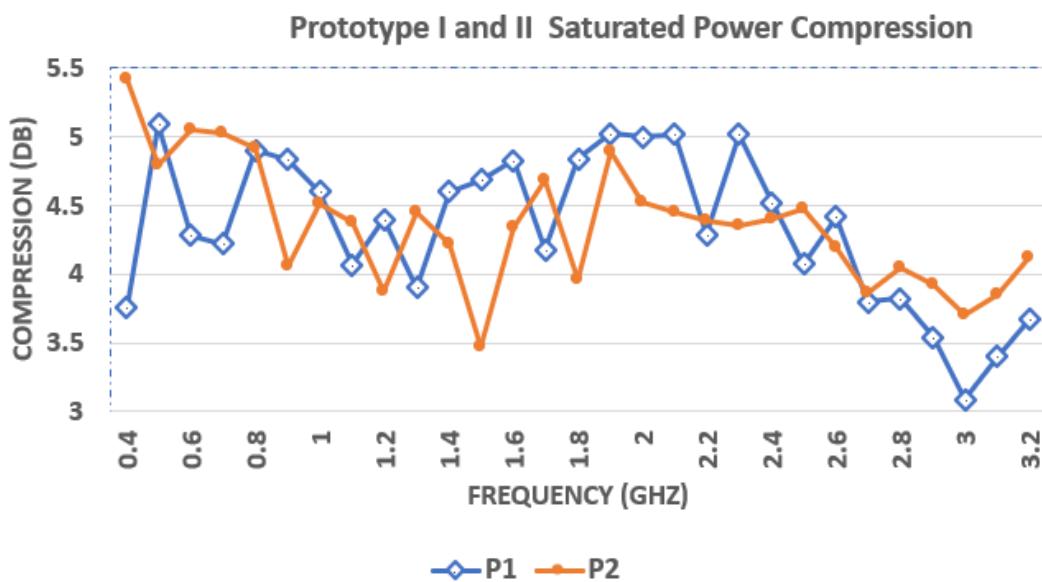

| Figure 4.48 | Measured saturated efficiency results of prototypes . . . . .                                                                               | 96 |

|             |                                                                   |     |

|-------------|-------------------------------------------------------------------|-----|

| Figure 4.49 | Measured saturated power gain compression of prototypes . . . . . | 96  |

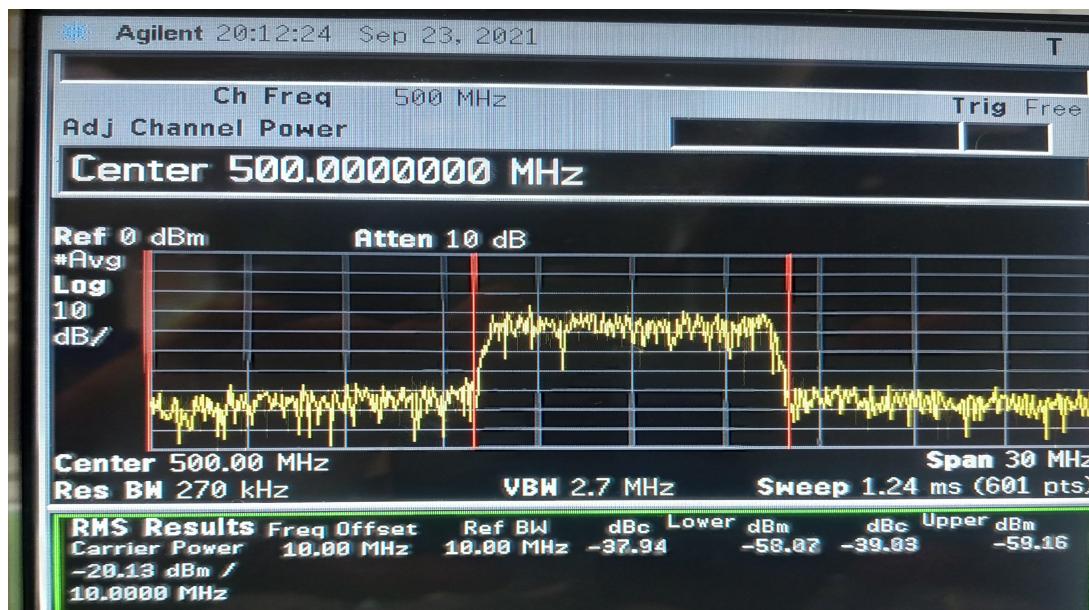

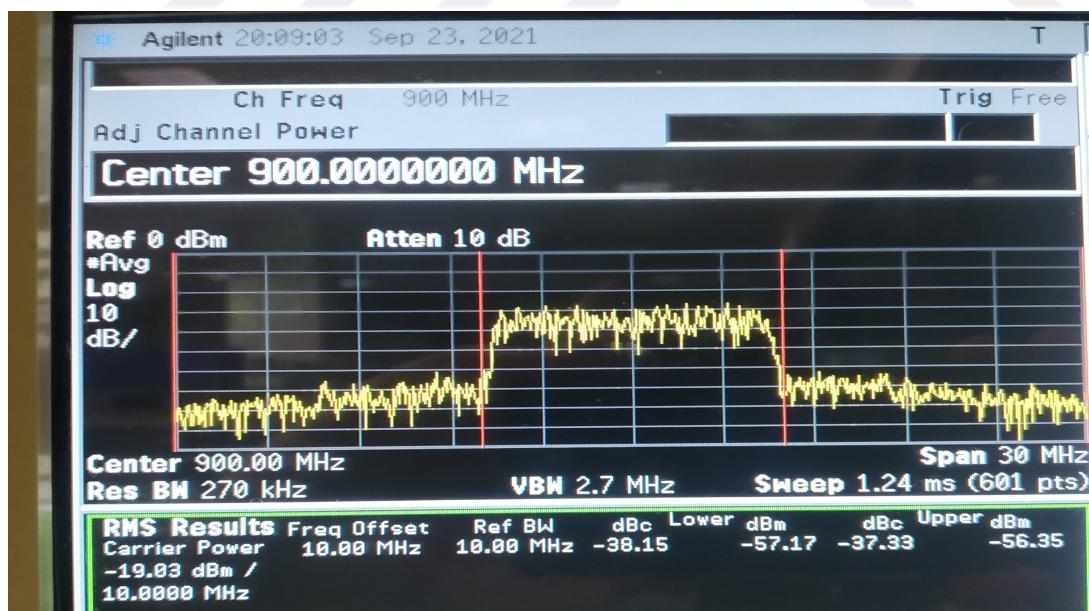

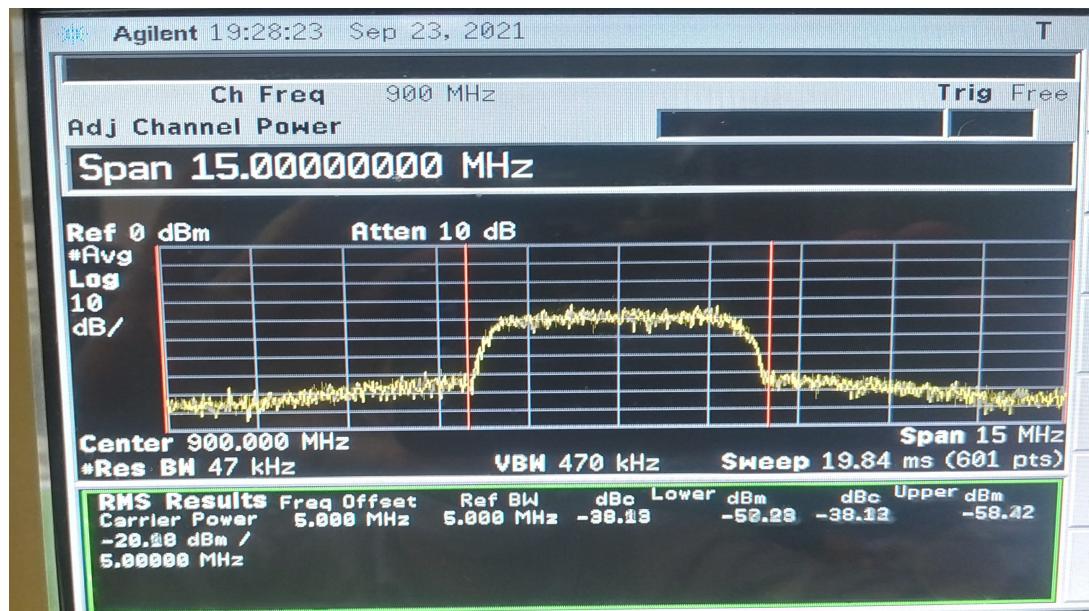

| Figure 4.50 | Measured ACLR with 500 MHz LTE . . . . .                          | 98  |

| Figure 4.51 | Measured ACLR with 900 MHz LTE . . . . .                          | 98  |

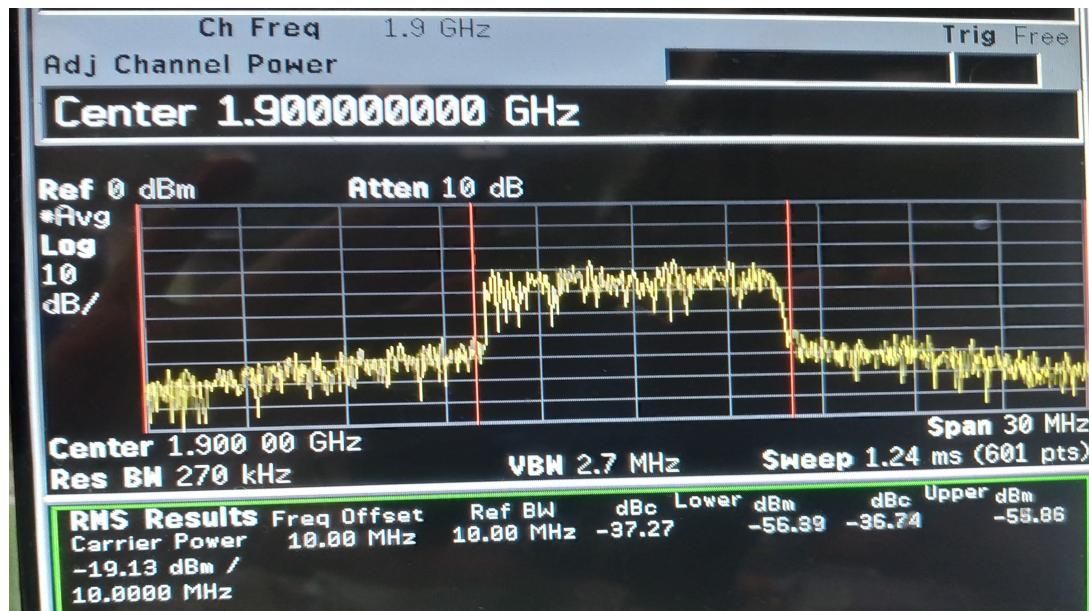

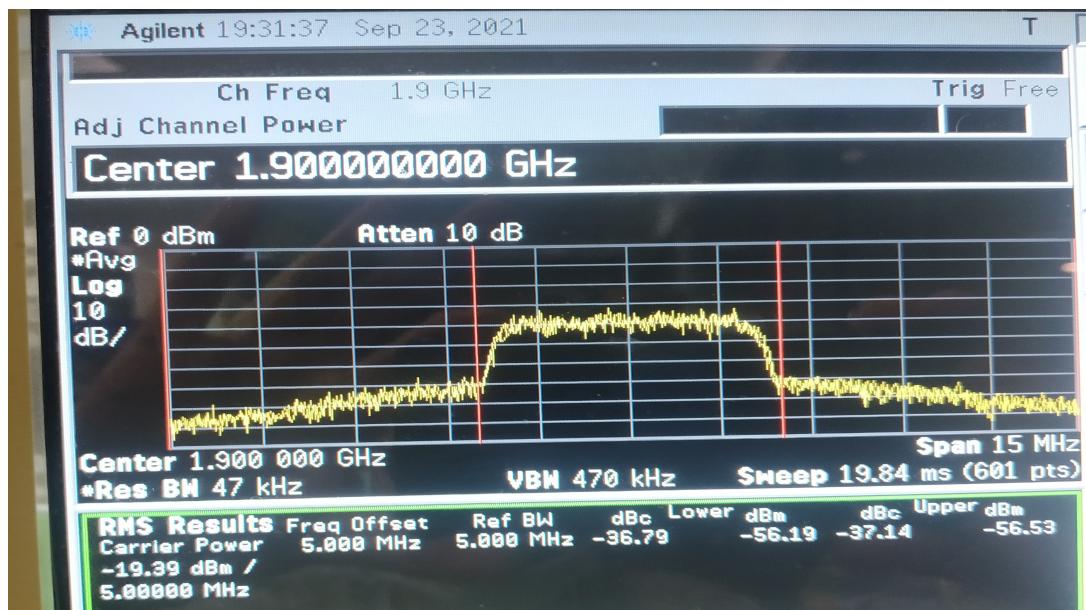

| Figure 4.52 | Measured ACLR with 1900 MHz LTE . . . . .                         | 99  |

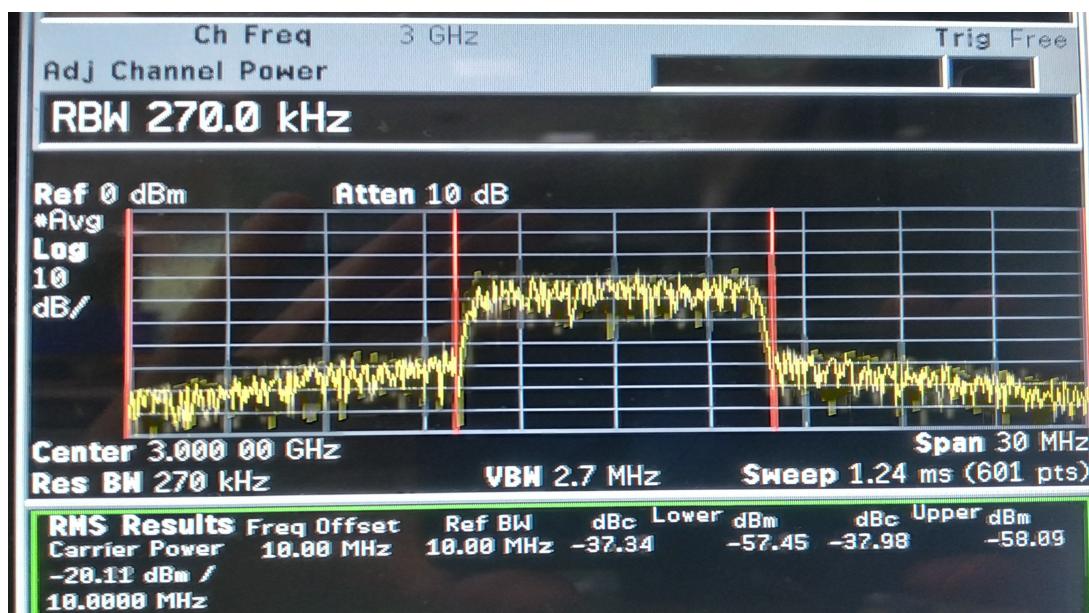

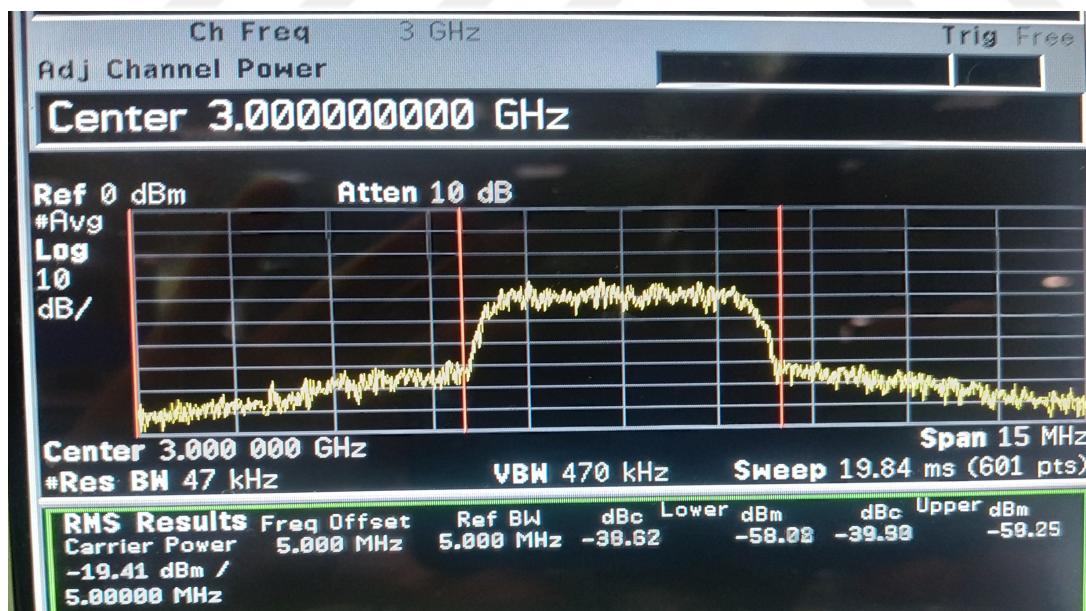

| Figure 4.53 | Measured ACLR with 3000 MHz LTE . . . . .                         | 100 |

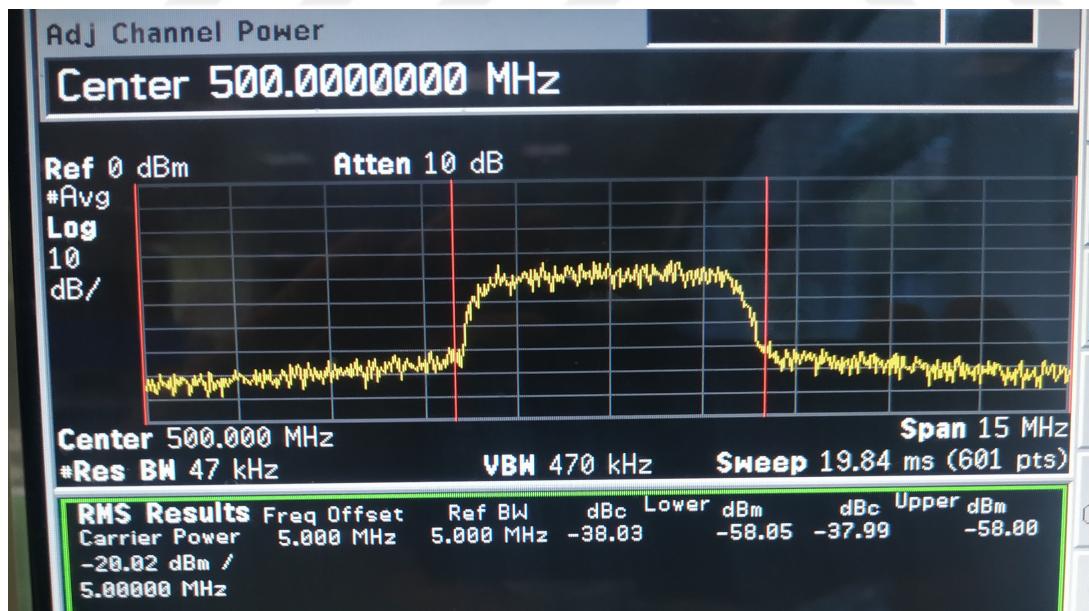

| Figure 4.54 | Measured ACLR with 500 MHz WCDMA . . . . .                        | 100 |

| Figure 4.55 | Measured ACLR with 900 MHz WCDMA . . . . .                        | 101 |

| Figure 4.56 | Measured ACLR with 1900 MHz WCDMA . . . . .                       | 102 |

| Figure 4.57 | Measured ACLR with 3000 MHz WCDMA . . . . .                       | 102 |

## **LIST OF ABBREVIATIONS**

|         |                                            |

|---------|--------------------------------------------|

| GaN/GAN | Gallium-Nitride                            |

| HEMT    | high electron-mobility transistor          |

| RRCJ    | resistive-reactive class-J                 |

| NRRCJ   | normalized resistive-reactive class-J      |

| PA      | power amplifier                            |

| SSPA    | solid-state power amplifier                |

| RF      | radio frequency                            |

| VSWR    | voltage standing wave ratio                |

| MMIC    | monolithic microwave integrated circuit    |

| ACPR    | adjacent channel power ratio               |

| ACLR    | adjacent channel leakage ratio             |

| PAR     | peak to average ratio                      |

| AM      | amplitude modulation                       |

| PM      | phase modulation                           |

| EVM     | error-vector magnitude                     |

| TWTA    | traveling-wave tube amplifier              |

| VED     | vacuum electronic device                   |

| OFDM    | orthogonal frequency-division multiplexing |

| LTE     | long-term evolution                        |

| WCDMA   | wideband code division multiple access     |

| CW      | continuous working                         |

| FET     | field effect transistor                    |

| VCVS    | voltage-controlled current source          |

# CHAPTER 1

## INTRODUCTION

### 1.1 RF Power Amplifiers

Though RF power amplifier design is a very old subject in the literature, the need for an RF power amplifier is inevitable in most of the microwave systems such as radars, jammers, medical imaging applications, and telecommunications. To put in simplest words, RF power amplifier is an instrument that magnifies the applied input RF signal amplitude using the fed-in DC energy by a gain factor throughout proper transistors whose size depend on the required power at the output of the amplifier. Purpose of using an RF power amplifier is to obtain high RF signal amplitude levels, which cannot be obtained using oscillators or frequency synthesizers, within a predetermined band of frequencies. Due to ongoing and increasing demand for power versus cost issues, the field has been kept always at the heart of the research and advancement in terms of power utility factor, cost effective solutions and ruggedness. The power utility factor is an important subject because it expresses the extent to which the technology of choice for the implementation of power amplifier can be exploited, safely. It generally determines the physical design space for the PA implementation, without any consideration of DC-RF conversion efficiency. The ruggedness and cost-effectiveness are strongly correlated with the power utility factor, mostly being in a trade-off relationship.

#### 1.1.1 Technologies and Terminologies Used in Design of RF Power Amplifiers

In this section of thesis, we aim to give a brief background information about up-to-date technologies and usual parameters for convenience with the later chapters.

Since GaN HEMT technology is chosen for the application of thesis subject, a short overview is presented.

At the heart of any RF power amplifier, there is a transistor technology which pre-determines the limits of the design parameters. The main design parameters of an RF PA can be listed as below.

- Frequency Band

- Bandwidth

- RF Power Output

- Gain

- Efficiency

- Ruggedness

- Thermal Management

- Cost

Parameters mentioned above can be identified as first-pass design goals for RF engineer. At the beginning of the design process, specifications are basically described in terms of these fundamental parameters. Choosing the appropriate technology is actually a milestone in the course of design because it will eliminate most of time consuming work and wasted budget. RF PA design requires expensive measurement equipment and qualified engineering experience together with the costly circuit materials such as transistors, resistors, capacitors. All of these resources are expected to be consumed, optimally.

Transistor technologies used to satisfy particular requirements relating some of the preliminary design goals, are generally fixed. For instance, the frequency band of which the transistor is operating, is the first thing to note. Since an attempt to use the device beyond the frequency limit is not meaningful, correct selection of semiconductor technology is necessary. Device manufacturers give the frequency information by indicating the cut-off frequency or providing frequency set in which transistor is internally matched to enable reasonable gain.

RF output power is the result that pays back all the investment in design. Hence the maximum RF power that can be both handled and safely extracted from device, makes this indication rather valuable. This thesis focuses on the technologies so-called discrete transistors, mostly unmatched. To build an SSPA(solid-state power amplifier), MMIC(monolithic microwave integrated circuit) or discretely packaged transistors may be cascaded. All of the cascade, combining operations and device decisions are made based on obtaining the required output power. MMIC technology is practical when device has matched input and output but it may not fit demands for RF power. It can require combination of large amount of MMICs, along with unpalatable combination loss, decreasing the efficiency of whole system, leading to increased monetary budget. After these brief considerations, designer ends up with a reasonable architecture, such as balanced amplifier topologies, single-ended amplifier topology, etc. One may, of course, raise whether every topology providing same RF output power is acceptable. A major debate can be conducted on such a subject, however there are lots of other criterion which can be justified only after constructing it, such as the ACPR, AM/PM distortion rate, EVM and linearity measurements, etc. This is a matter of experience for the designer. Transistor manufacturers also guide designers through the process, because manufacturers generally pinpoint certain set of applications and outstanding features of their devices to ease marketing.

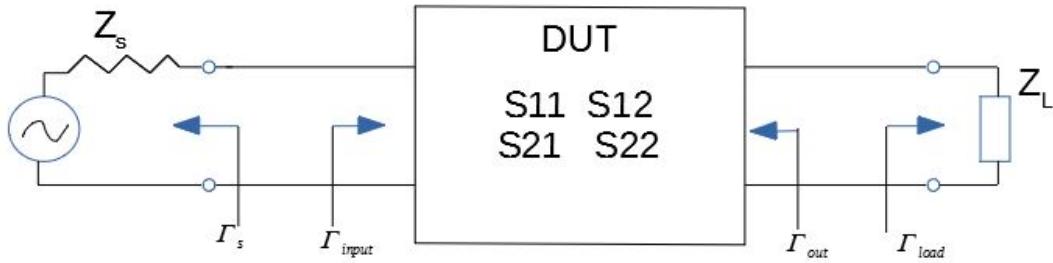

There exists various kinds of gain definitions in the literature. RF PA designer, in particular for high power business, is usually concerned with the large signal gain, but it shows strong dependence on design periphery elements. To justify the anticipated performance of the transistor at first glance, small-signal gain parameters are evaluated. Common gain parameters and their brief descriptions with representations in terms of S-parameters are given below with reference to [1]. A simple schematic representation is given in figure 1.1 for better understanding of reflection planes.

- Transducer Gain ( $G_T$ )

- $G_T$  is defined as the ratio of power delivered to the load  $P_L$  to the available power from the source  $P_{av}$ . It is formulated as in (1.1).  $G_T$  is the general gain parameter which describes the gain without any matching effort. Meaning that input and output matching networks are not necessary.

Figure 1.1: Reflection Plane Definitions with a Device Under Test (DUT)

ily designed, it reflects the response of the bare device to the measurement impedance environment, usually 50-ohm.

$$G_T = \frac{P_L}{P_{av}} = \frac{(|S_{21}|)^2(1 - |\Gamma_s|^2)(1 - |\Gamma_L|^2)}{(|1 - \Gamma_s \Gamma_{in}|)^2(|(1 - S_{22} \Gamma_L)|)^2} \quad (1.1)$$

- Operating Power Gain ( $G_p$ )

–  $G_p$  is defined as the ratio of power delivered to the load  $P_L$ , to the power delivered from source to the input of device  $P_{delivered}$ . It is formulated as in (1.2).  $G_p$  describes the gain at the condition of matched generator impedance to the input impedance. In other words, generator mismatch is not taken into account. As it is shown in equation (1.2), it only depends on S-parameters of the device and load reflection coefficient  $\Gamma_L$ , since  $\Gamma_{in}$  is dependent on S-parameters and  $\Gamma_L$ . Moreover, it can be deduced from equation (1.1) by setting  $\Gamma_s = \Gamma_{in}^*$ .

$$G_p = \frac{P_{load}}{P_{delivered}} = \frac{(|S_{21}|)^2(1 - |\Gamma_L|^2)}{(1 - |\Gamma_{in}|^2)|1 - S_{22} \Gamma_L|^2} \quad (1.2)$$

- Available Power Gain ( $G_a$ )

–  $G_a$  is defined as the ratio of power available from the 2-port network  $P_{avn}$ , to the power available from source  $P_{avs}$ . It is formulated as in (1.3).  $G_a$  describes the gain at the condition of matched output impedance to the load impedance. In other words, load mismatch is not taken into account. As it is shown in equation (1.3), it only depends on S-parameters of the

device and source reflection coefficient  $\Gamma_s$ , since  $\Gamma_{out}$  is dependent on S-parameters and  $\Gamma_s$ .

$$G_a = \frac{P_{avn}}{P_{avs}} = \frac{(|S_{21}|)^2(1 - |\Gamma_s|^2)}{(1 - |\Gamma_{out}|^2)|1 - S_{11}\Gamma_s|^2} \quad (1.3)$$

Applying the above gain definitions, designer is provided with a clue about the small-signal characteristics of the device. In a real application, frequency dependent behavior is the major consideration. Today, manufacturers have strong motivation to present accurate large and small-signal models of the devices. With the help of simulation software, it is easy to get preliminary evaluation of the devices. Large-signal characteristic is the next and most important step in decision process of transistors.

Large-signal capabilities of the transistor and PA determine the final product's performance with various aspects such as signal distortion properties mentioned before. Hence, application-oriented design methods are employed. The optimization of PA occurs throughout the large-signal design steps. Despite the fact that RF PA is a complex device that has many applications and specific requirements, efficiency parameter cannot be overlooked. It is valuable as output power, indeed. It shapes the parameters reflected directly on the cost budget of project. Efficiency affects the thermal management requirements, thermal load of the device thereby the lifetime of device, and power supply capacity. Usually the minimum efficiency that should be maintained in operation can be calculated easily, because device thermal junction to case resistance, maximum allowable junction temperature and thermal load sustainable with the cooling system are well-defined by device manufacturers and system architecture. Employed technology manufacturers exhibit extensive test effort to make sure lifetime specifications are correctly presented. There are reports describing the elaborated qualification process such as [2]. Detailed efficiency related discussions and calculations are provided through the next chapters of this thesis.

For the purposes of verification and qualification of any design, ruggedness is always an issue in terms of PA designer and device manufacturers. Heart of any good design is a reliable transistor with proven capabilities such as V<sub>ds</sub> breakdown voltage, gate stability and degradation curves under harsh RF, DC, thermal and environmental circumstances. In the literature, various efficiency enhancing methods are shown, but they come along with trade-offs, such as in Class-J method; peaking voltage wave-

forms that may cause irreversible damage to device. About the breakdown mechanisms, extensive investigations can be found in the literature such as the thesis work [3]. Moreover, having the particular interest of this thesis as Class-J approach, specialized study of [4] analyze the hot electron densities and their possible effects on device failure by comparison of DC loading, RF Class-B operation and Class-J operation. It finds out the degradation tendency due to high electric field stress (high  $V_{ds}$ ), is higher in Class-J operation, possibly affecting the MTBF values. Other than device level tests, PA products are also subject to meet certain constraints one of which is the bad VSWR loading conditions due to antenna itself or in case of a load failure. In short, ruggedness of the amplifier is constantly questioned with particular interest by design process starting from device selection to end-user product.

To sum up, general design parameters and discussion with literature examples are presented within this subsection. A practical approach is adopted to motivate “efficiency” considerations and preliminary ideas about trade-offs. Detailed expressions are left for the next chapters.

### **1.1.2 GAN HEMT Technology**

During the history of RF PA design, various kinds of technologies have been deployed. One of the oldest technology for PA realization is vacuum electronic devices such as TWTA(traveling-wave tube amplifiers), magnetron, and klystron. Vacuum devices have been utilized for amplification, high-speed switching, and rectifying applications. Their ability to handle high-power makes VEDs good candidates for military and space applications such as RADAR signaling and satellite communications. Along with the benefits they present, some drawbacks are unpalatable such as excessive heat dissipation, bulky structure, high power supply, and complex grid control management [5]. In particular, TWTA have found a wide range of application areas in satellite communications as downlink power amplifiers, in the 1960s [6]. Though TWTA technology has been the choice over solid-state power amplifiers(SSPA) in space missions due to their unique high rated power and frequency availability[7], SSPAs have been displacing TWTA counterparts rapidly in mid-power radar, jamming [8]. High power particle accelerators are also in demand for SSPA replacements

[9]. Turning to SSPA in those fields are closely related to lower power supply voltages required than TWT operation, design cost, and sustainability issues[8]. Hence the SSPA experiences great advancements in recent years due to increasing market shares and potential usage.

Improvements in semiconductor technologies which are major constituents of SSPA have a significant impact on design dynamics. One of the recent breakthrough materials showing remarkable features is GaN(gallium-nitride). The material has a wider bandgap that is around 3.4 eV, than its competitors as Si(silicon) with 1.12 eV and GaAs(gallium-arsenide) with 1.42 eV [10]. That brings about a higher breakdown voltage which enables operation with a higher drain supply voltage. Higher supply voltage for a specific RF output power means lower current and high output impedance so that it decreases the design complexity of matching networks. Moreover, high saturated drift velocities lead to high power densities, often expressed in watts per unit gate peripheral size. Thereby it takes fewer devices to combine for the specific output power levels than the competing technologies. Reduction in the number of combined devices results in lower capacitance per watts, making the overall device suitable for broadband and high-frequency applications[10]. Table 1.1 shows a comparison of particular parameters for different semiconductor technologies [11].

Table 1.1: Parameters for Microwave Semiconductor Materials

| Characteristic Parameter \ Semiconductor Materials             | Silicon | Gallium Arsenide | Indium Phosphide | Silicon Carbide | Gallium Nitride |

|----------------------------------------------------------------|---------|------------------|------------------|-----------------|-----------------|

| Bandgap (eV)                                                   | 1.1     | 1.42             | 1.35             | 3.25            | 3.49            |

| Electron Mobility at 300 <sup>0</sup> K (cm <sup>2</sup> / Vs) | 1500    | 8500             | 5400             | 700             | 1000-2000       |

| Saturated Electron Velocity (cm / s) x10 <sup>7</sup>          | 1       | 1.3              | 1                | 2               | 2.5             |

| Breakdown Field (MV / cm)                                      | 0.3     | 0.4              | 0.5              | 3               | 3.3             |

| Thermal Conductivity (W/cm <sup>0</sup> K)                     | 1.5     | 0.5              | 0.7              | 4.5             | 1.5             |

| Relative Dielectric Constant ( $\epsilon_r$ )                  | 11.8    | 12.8             | 12.5             | 10              | 9               |

The higher power density of the material requires careful thermal management to utilize devices safely with optimum performance. For this purpose, GaN is grown upon substrates with reasonable thermal conductivities such as SiC(silicon carbide),

sapphire, and silicon [12]. Accounting for the superior properties of GaN, it seems to be a proper choice for the peaking amplifier classes such as class-J [13]. In summary, GaN technology is gradually improving in its way to challenge existing competents. Although vacuum devices remain the only choice for many high-power applications above kW levels, designers show a strong tendency to employ GaN devices for mid-power and broadband applications in the last decade, especially.

## 1.2 Research Motivations and Objectives

As mentioned in the previous section, an RF PA comes with a large criterion list. The system which involves RF PAs should be carefully established by considering those outlined parameters. The application areas such as jamming, radar, telecommunication, or multi-mission tasks require different conditions to fulfill. In literature, the most prominent parameter is efficiency. Efficiency enhancement methods by continuous modes defining proper harmonic terminations accommodate a remarkable portion of the research. The continuous class-J mode approach is one of the popular subjects of study. J-mode's relatively wide-band potential, almost one-octave, itself, has been investigated to develop methods broadening the bandwidth.

The broadband high-power PAs are attracted to designers for several reasons. Having an amplifier covering a wide range of frequencies decreases the physical size and complexities at the system level. For example, in a jamming application, amplifiers are operated to counteract a particular set of frequency bands. Instead of having multiple narrowband amplifiers, one broadband amplifier does the job more efficiently. Multiple amplifiers require a bulky cable harness, a set of synthesizer RF outputs, and time shared frequency hopping embedded in programming structure and multiple separate antennas leading to shadowing problems. Hence reducing the number of amplifiers by increasing the bandwidth coverage is preferable over multiple PA solutions.

This thesis is not focused on a specific application, though it is generally at the most used communication bands (400-3200 MHz). These frequencies are also the potential targets for jamming in military applications. The communication waveforms have

intrinsic properties such as ACPR(adjacent channel power ratio), PAPR(peak to average power ratio), certain modulation types like OFDM in LTE. In terms of a complete evaluation of linearity, the general design approach of this thesis may remain insufficient to assess the performance of the PA. So, this thesis is not focused on applications demanding high linearity. However, we put high efficiency and broadband in the center of this work, which is the ultimate target for applications in the field of CW(continuous working) amplifiers. The prototype of thesis work is a fine candidate for jamming applications. Although there exists conceptually no burden to use in radar applications, frequency bands in this work are not the same as the well-known military radar bands.

Through this work, we review the existing literature of modified class-J approaches proposing methods to adjust harmonic terminations with resistive parts, with a particular focus on broadband efficiency performance. We combine different perspectives by stating critical measures of performance. A new modification called NRRCJ, "normalized resistive-reactive class-J", is proposed. The theoretical aspects of the approach are analyzed in depth. A design flow for a three-octave amplifier is suggested. The established theoretical flow is experimented with by constructing a prototype RF PA operating in 400-3200 MHz.

The main objectives of this work are declared as:

- Investigate the continuous mode class-J approach methodologically to enhance operational bandwidth up to more than one octave.

- Present a novel mathematical analysis and comprehension of the proposed method.

- Submit an engineering approach within a detailed design procedure.

- Outline the strong and weak sides of the theory in an objective way.

- Provide the comparison of experimental results and theoretical expectations.

### 1.3 Contributions

Our contributions are as follows.

- A detailed literature review is presented in the second chapter of this work.

- Existing resistive-reactive class-J proposals are reviewed in detail.

- A novel modification is suggested to remove the "changing DC component" conflict of the theory.

- A novel mathematical analysis is provided by integration of frequency into iterative parametric relations.

- It is shown by theory and applications that there exists a broadband applicable impedance space capable of high efficiency and satisfactory RF output power, without requiring a varying DC component in the voltage waveform.

- A three-octave medium power RF PA , which is operating in the frequently used region of spectrum, is prototyped.

- Similar literature examples are compared with the final prototype.

- Future work ideas are suggested to encourage further research on the subject.

#### 1.4 The Outline of the Thesis

In chapter 1, a brief description of RF power amplifiers and basic amplifier parameters are introduced. SSPA and vacuum electronics technologies are compared by considering their usage areas. GaN HEMT technology and other semiconductor technologies are compared by literature search. Thesis motivations and objectives are described. Contributions to the literature are summarized.

Chapter 2 provides an extensive literature review on classical operation modes. The notation convention adopted throughout the theoretical analysis of this work is introduced. Assumptions commonly used in the literature are listed and explained. The load-line theory is described with a detailed explanation.

In chapter 3, we present the modified class-J approaches. The perspectives in the literature are examined. The NRRCJ "normalized resistive-reactive class-J" approach is proposed. Iterative impedance equations are introduced. Voltage waveforms and

impedance spaces are investigated at the current generator plane. Efficiency and power derating curves are introduced with comparsion to existing methods.

Chapter 4 describes the integration of NRRCJ iterative equations into design scheme, at first place. Design parameters are mapped to frequency dependent function forms. To the best of the author's knowledge, a novel parametric analysis is conducted on the subject. After mathematical analysis, a practical procedure is outlined for three-octave PA design. Two prototypes are designed. Simulation and measurement results are discussed. Final prototype is shown to have concurrent performance with the expectations.

Chapter 5 discusses comparison of the similar prototype results with this work. Com-

parsions show that final prototype shows superior performance than counterparts in many aspects. Achievements of the study, encountered difficulties through the thesis work, strong and weak sides of the study are summarized in conclusions. Some future work ideas are suggested to enhance the research on the subject of this thesis.

## CHAPTER 2

### LITERATURE REVIEW

This chapter reviews the literature and includes preliminary analysis. Analysis equations are referenced in later chapters, as well. The basic amplifier topologies are overviewed. Basic load-line theory is recalled.

#### 2.1 Conventional Modes of Operation

The classical modes of operation in PA theory is built on ideal FET model which presumes the transistor as a voltage-controlled current source. The assumptions of the ideal FET model are given under classes of operation. Class A, B, AB power amplifiers and general amplifier topology with the widely used parameters are introduced.

##### 2.1.1 Class-A, B and A/B

The basic PA theory starts with the class-A design topology. Conventional classes are generally named in accordance with conduction angle and the loading conditions which shape the matching circuitry at the output. Gain is not considered often since transistors have satisfying gain, mostly. All the features defined for the classes are regarding the ideal transistor model which assumes it as a voltage-controlled current source. The VCCS model assumptions are clearly stated in this section.

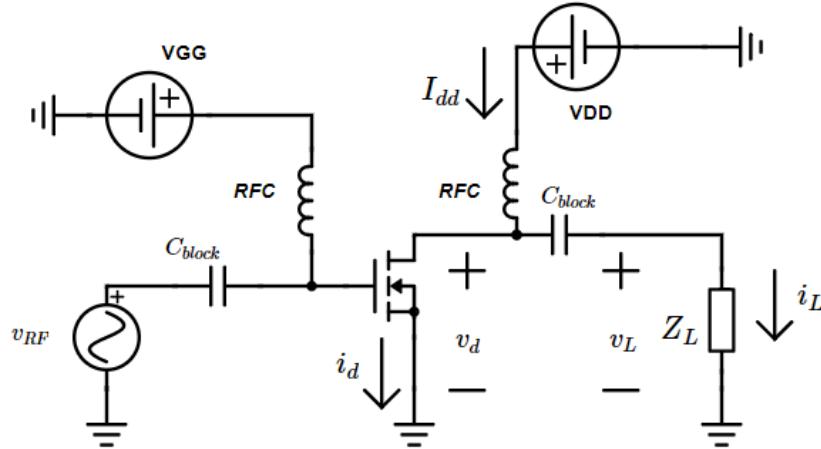

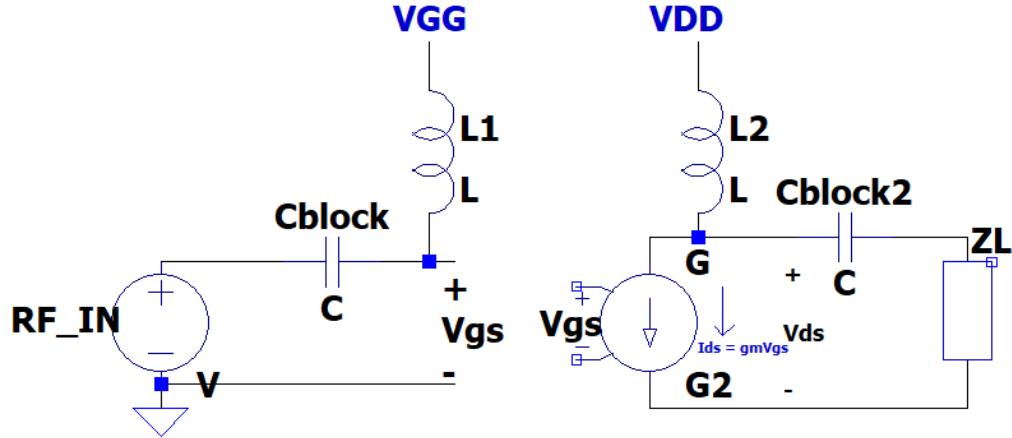

For the explanation and analysis of the classes, we use a common circuit schematic in figure 2.1, so that voltage polarities and current directions are consistent. Before going into circuit terms, we recall the fourier series representation of signals for the simplicity of later discussion.

The time harmonic representation of the drain and voltage waveforms can be written as Fourier series expansions of sinusoids. Since both current and voltage are real signals, we use the property of Fourier series given in (2.1)-(2.3).

$$x(t) = \sum_{n=-\infty}^{\infty} c_n \exp(j2\pi f_0 n t) \quad (2.1)$$

If  $x(t)$  is real, then equation (2.1) becomes:

$$x(t) = c_0 + 2 \operatorname{Re} \left( \sum_{n=1}^{\infty} |c_n| \exp(j\varphi_n) \exp(j2\pi f_0 n t) \right) \quad (2.2)$$

Where  $c_n$  is the complex Fourier series coefficient and can be written as  $c_n = a_n + jb_n$ , equation (2.2) is rearranged as in (2.3).  $c_0$  is the average(dc) value of the real signal.  $\varphi_n$  is the phase of the nth harmonic content.

$$x(t) = c_0 + 2 \left( \sum_{n=1}^{\infty} a_n \cos(2\pi f_0 n t) - b_n \sin(2\pi f_0 n t) \right) \quad (2.3)$$

Figure 2.1: Transistor and surrounding RF circuit diagram showing used current conventions.

Using the above short recall, we can define time harmonic expansion of drain voltage  $v_d(\theta)$  and drain current  $i_d(\theta)$  by absorbing the factor “2” into the coefficients. Figure 2.1 is the reference for all of the circuit equations in this section.

$$v_d(\theta) = V_{dd} + \left( \sum_{n=1}^{\infty} V_{n,r} \cos(n\theta) - V_{n,q} \sin(n\theta) \right) \quad (2.4)$$

$$i_d(\theta) = I_{dd} + \left( \sum_{n=1}^{\infty} I_{n,r} \cos(n\theta) - I_{n,q} \sin(n\theta) \right) \quad (2.5)$$

Equations (2.4)-(2.5) express the current and voltage waveforms by in-phase and quadrature parts, where  $\theta = 2\pi f_0 t$ . Current and voltage waveforms are all assumed at the intrinsic current generator plane of the transistor. Intrinsic current generator is a hypothetical plane of reference in VCCS model, which will be elaborated under subsection 2.1.2. DC block capacitor in figure 2.1 is assumed ideal so that voltage drop across it is zero. The circuit nodal equations are simply written as in (2.6)-(2.7)

$$i_d(\theta) = I_{dd} - i_L(\theta) \quad (2.6)$$

$$v_d(\theta) = V_{dd} + v_L(\theta) \quad (2.7)$$

Using (2.4) - (2.7), we find load voltage and current expressions at the generator plane.

$$v_L(\theta) = \left( \sum_{n=1}^{\infty} V_{n,r} \cos(n\theta) - V_{n,q} \sin(n\theta) \right) \quad (2.8)$$

$$i_L(\theta) = - \left( \sum_{n=1}^{\infty} I_{n,r} \cos(n\theta) - I_{n,q} \sin(n\theta) \right) \quad (2.9)$$

$$I_n = I_{n,r} + jI_{n,q} \quad (2.10)$$

$$V_n = V_{n,r} + jV_{n,q} \quad (2.11)$$

Equations (2.8)-(2.11) shows the general phasor domain expressions which will be exploited in calculations of impedance, power and efficiency.

$$Z_n = - \frac{V_{n,r} + jV_{n,q}}{I_{n,r} + jI_{n,q}} = - \frac{|V_n|}{|I_n|} e^{(j\varphi_{n,v} - \varphi_{n,i})} \quad (2.12)$$

$$P_n = - \frac{1}{2} \operatorname{Re}\{V_n I_n^*\} = - \frac{1}{2} (V_{n,r} I_{n,r} + V_{n,q} I_{n,q}) \quad (2.13)$$

We presented the fundamental equations that we are going to address in explanation of classes. We could move on to identify the classes.

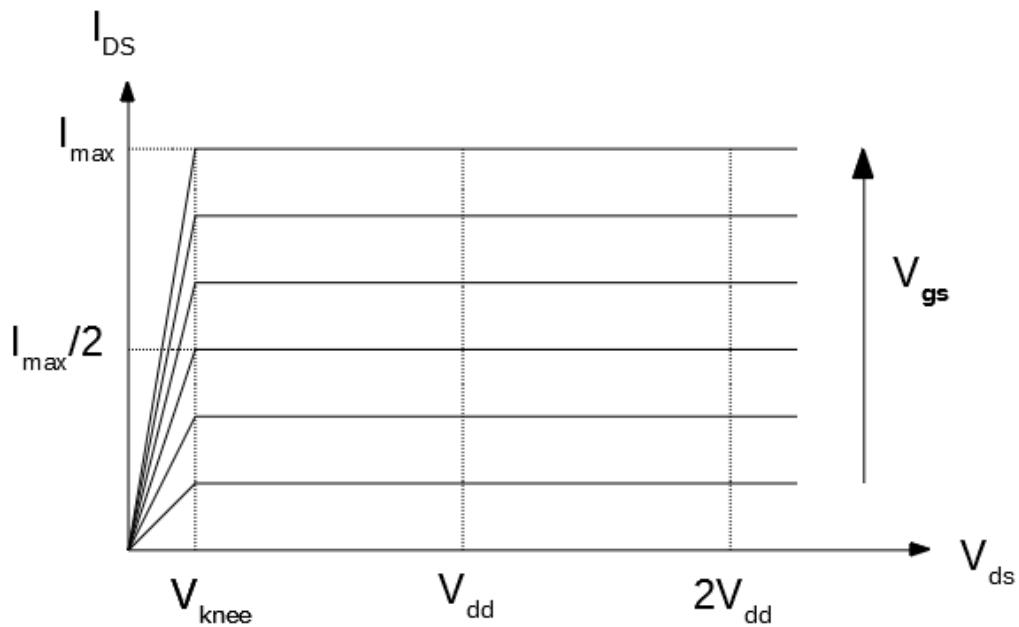

Class-A is generally understood as ideal linear amplifier in the PA designer community. The reason is that the Class-A amplifier output spectrum doesn't include any harmonics, theoretically. Of course, theory is defined such that the overdrive above the linear region of amplifier is not allowed. After a certain drive level it also becomes naturally a nonlinear amplifier. To understand the class-A definition, a generic I-V curve profile is given in figure 2.2. The horizontal axis is the drain-to-source voltage and the vertical axis is the drain current drawn from the supply.

Figure 2.2: I-V current profile of a simple FET

Figure 2.2 reflects a rough representation of a FET DC I-V characteristic.  $I_{max}$  is the maximum current that the device can support.  $V_{knee}$  is the critical drain-source voltage below where device current is a strong function of  $V_{gs}$  and  $V_{ds}$ . That region is called the "triode" or "knee region". Above knee voltage level, transistor is in saturation regime and device current is strongly function of  $V_{gs}$  with neglected effect of  $V_{ds}$ . For any amplifier topology, the gate bias point, which is the constant dc voltage applied to gate, and the drain bias point, which is the supply voltage, determine the "quiescent" point. Q-point is actually a DC boundary condition that should be satisfied by RF load-line. When RF signal is applied to gate, it causes a current and voltage swing at drain terminals around Q-point. In order to have a harmonic-free spectrum, the

current and voltage swing should not be distorted or clipped upto  $I_{max}$  and before reaching  $V_{knee}$ . Thereby, the Q-point of Class-A is adjusted to the half of maximum drain current. In process of biasing, supply voltage  $V_{dd}$  is generally predetermined at the system level, what remains is to decide on gate voltage. By equations (2.6) - (2.13), the RF signal is superimposed onto DC signal and the complex impedance of the load constraints the amplitude and phase of the current and voltage swing.

At this point we should state the assumptions made in the upcoming analysis:

- (a) Drain current is directly related to gate voltage excursion by constant transconductance.

- (b) Knee region (triode region) where channel current is a strong function of drain-source voltage  $v_d(\theta)$  is neglected.

- (c) Due to (b),  $R_{on}$ , which is on resistance of the channel is neglected.

- (d) "DC-RF" dispersion, or alternately referred as "knee walkout" phenomenon; on which there is a great effort to include into transistor models with the studies as in [14], is neglected.

- (e) Voltage and current at the intrinsic plane cannot be negative. Since intrinsic plane is hypothetical, this is stated as an assumption. Lots of research and achievements can be found in the literature to model the voltage and current nonnegative at this plane, such as the extensive thesis study in [15].

In the light of assumptions (a)-(e), a basic constant transconductance VCCS model schematic is given in figure 2.3 for the sake of discussion. For the class-A bias we can express the voltage and current equations by modifying (2.6) - (2.11).

$$i_d(\theta) = \frac{I_{max}}{2} - I_L \cos(\theta) \quad (2.14)$$

$$v_d(\theta) = V_{dd} + V_L \cos(\theta + \varphi) \quad (2.15)$$

(2.14) and (2.15) are the general waveform expressions of which amplitude changes with the driving RF signal level. In addition, (2.15) includes a free phase variable  $\varphi$  that depends on the fundamental load impedance. The phase shift of voltage is an

Figure 2.3: Basic Constant Transconductance VCCS Model

important parameter because it directly affects fundamental power delivered to load, thereby, the efficiency.

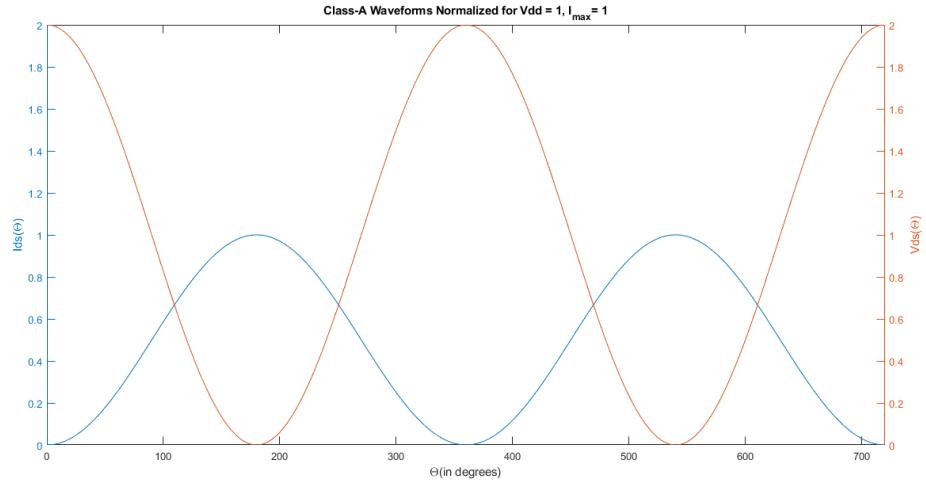

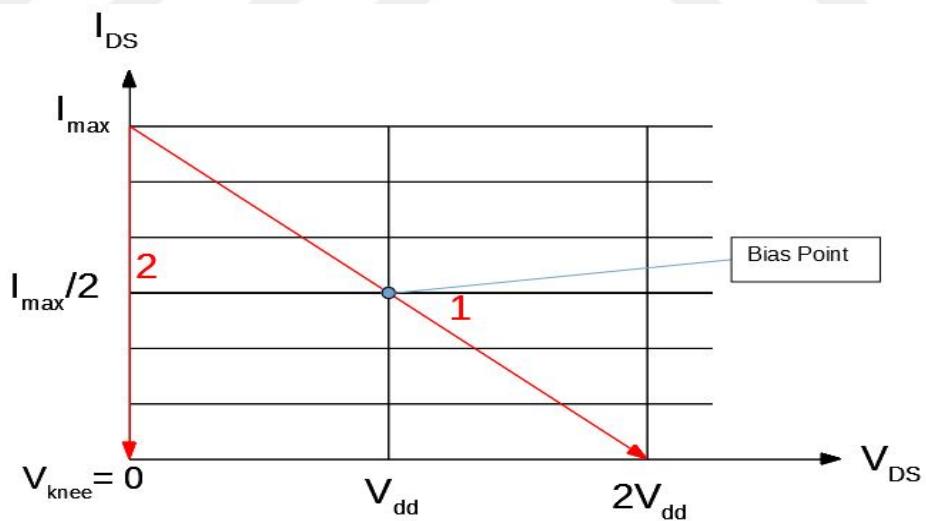

Equation (2.14) tells us the DC power consumption in Class-A is independent of the drive level or output power. It means the more RF power delivered to load, the more efficiency is obtained. Class-A reaches its maximum efficiency point at maximum linear drive level, where it happens at  $I_L = I_{max}/2$ . To maximize the RF power dissipated at the load, we should have a completely resistive optimum load which won't cause the voltage swing below zero when current is maximum. Hence the maximum value of  $V_L = V_{dd}$  should be reached for the optimum output power, as well. We should emphasize that the knee voltage is assumed as "0". The drain current and voltage waves at maximum drive level are shown in the figure 2.4, in normalized amplitudes. The voltage, current,  $P_{RF}$ ,  $P_{DC}$  and efficiency calculations are expressed in (2.16) - (2.20). The calculations are done, setting  $\varphi = 0$ . The RF load-line superimposed onto DC I-V curve is seen in figure 2.5.

$$i_d(\theta) = \frac{I_{max}}{2} - \frac{I_{max}}{2} \cos(\theta) \quad (2.16)$$

$$v_d(\theta) = V_{dd} + V_{dd} \cos(\theta) \quad (2.17)$$

$$P_{RF} = \frac{V_{dd} I_{max}}{4} \quad (2.18)$$

Figure 2.4: Class-A Drain and Current Waveforms for  $V_{dd} = 1$ ,  $I_{max} = 1$

$$P_{DC} = \frac{V_{dd}I_{max}}{2} \quad (2.19)$$

$$\eta_{max} = \frac{P_{RF}}{P_{DC}} = \%50 \quad (2.20)$$

Figure 2.5: Red-line paths showing dynamic I-V loadline. The knee voltage is zero.

In figure 2.5, the I-V trace is divided into two paths numbered as 1, 2. Indeed, path 1 and 2 form a complete one path, but the path 2 is only traced when the amplifier

is overdriven from the gate. Path 2 is a special case which will be reported in the next section. As long as nominal drive signal is applied, the path 1 is traced equidirectional. Agreement is easily seen compared with figure 2.4. The reason of setting  $\varphi = 0$ , is having the maximum power at the load, thereby maximizing efficiency. It also implies a purely resistive load, which is so-called "optimum class-A load",  $R_{opt,A}$ . Optimum load is calculated using equation 2.12.

$$R_{opt,A} = \frac{2V_{dd}}{I_{max}} \quad (2.21)$$

Class-B amplifier is the starting point of almost every high efficiency amplifier mode, since it constraints the harmonic loading condition together with the bias state. The outstanding difference from class-A is, high efficiency with the same amount of maximum RF power transfer to the load. In discussion of class-B, "conduction angle" term is widely used in the literature. We will show the conduction angle with  $\alpha$ . Conducting cycle of the transistor means the time or angular time that the transistor drain current  $i_d$  is nonzero. In class-A,  $\alpha = 2\pi$  as seen from figure 2.4. For the class-B case, transistor Q-point is at "zero current" bias point. Hence, device doesn't conduct until an RF input excitation above the transistor gate threshold.

At the first step of Class-B analysis, we assume current waveform doesn't include quadrature components, meaning that  $I_{n,q} = 0$  for all "n". Having quadrature components zero implies the "even" function property around zero conduction angle. The class-B half wave rectified sine current is the usual convention at the beginning of high efficiency mode analysis as in fundamental examples from literature, [16, 17, 18, 19, 20, 21, 22]. In the light of above assumptions (a)-(e), we can express the class-B current waveform and the version of common practical interest which is the class A/B waveform. All the assumptions are valid for class A/B, as well. The class-B waveform can be seen in figure 2.6.

Figure 2.6: Conventional Class-B Waveform (Normalized to Peak Value)

The waveform can be written as a composition of harmonics in equations (2.22) - (2.23). From (2.22) and (2.23), there only exists even harmonics, and waveform can be written in open form as given by (2.24) - (2.25).

$$i_d(\theta) = \frac{I_{max}}{\pi} + \left( \sum_{n=1}^{\infty} I_{n,r} \cos(n\theta) \right) \quad (2.22)$$

$$I_{n,r} = \begin{cases} \frac{I_{max}}{2} & ; n=1 \\ \frac{2I_{max} \cos(n\frac{\pi}{2})}{\pi(1-n^2)} & ; n= 2, 4, 6, \dots \end{cases} \quad (2.23)$$

$$i_d(\theta) = \frac{I_{max}}{\pi} + \frac{I_{max}}{2} \cos(\theta) + \frac{2I_{max}}{3\pi} \cos(2\theta) - \frac{2I_{max}}{15\pi} \cos(4\theta) + \frac{2I_{max}}{35\pi} \cos(6\theta) - \dots \quad (2.24)$$

$$i_L(\theta) = -\frac{I_{max}}{2} \cos(\theta) - \frac{2I_{max}}{3\pi} \cos(2\theta) + \frac{2I_{max}}{15\pi} \cos(4\theta) - \frac{2I_{max}}{35\pi} \cos(6\theta) + \dots \quad (2.25)$$

So far, we did nothing but recall the classical analysis steps of class-B type current waveform by stating underlying assumptions. Efficiency and RF power output considerations become totally dependent on the load impedance  $Z_n$  at fundamental and harmonics.  $I_{max}$  in equations (2.22) - (2.25) expresses the saturated drain

current waveform without clipping. In real conditions, voltage clipping due to harmonic impedances will modify the current waveform, yet we didn't analyze the load impedance. Current waveform is dependent on the drive level (linearly by the assumptions (a)-(e)), and subject to change following the load impedance for reaching the required output power. The load impedance in class-B analysis is assumed to be short circuit at all harmonic frequencies. So, the voltage waveform can be written as in (2.26) and (2.27).

$$v_d(\theta) = V_{dd} + V_{1,r} \cos(\theta) - V_{1,q} \sin(\theta) \quad (2.26)$$

$$V_d(t) = V_{dd} + \sqrt{V_{1,r}^2 + V_{1,q}^2} \cos \left( 2\pi f_0 t + \text{atan2} \left( \frac{V_{1,q}}{V_{1,r}} \right) \right) \quad (2.27)$$

Equation (2.27) can be expressed in a compact way in (2.28).

$$V_d(t) = V_{dd} + V_1 \cos(2\pi f_0 t + \varphi_1) \quad (2.28)$$

Indeed, the formulations with the above analysis cause some constraints on the fundamental load impedance. A few comments must be made at this point for the clarity. These can be ordered as follows:

- Equation (2.28) implies a strong condition on the fundamental swing of drain voltage. By the derivation procedure, we always assumed that voltage clipping doesn't occur and thereby, cannot affect the current waveform shape. If the voltage clipping was accepted, current waveform would be distorted such that it would have the odd harmonics, as well.

- If we would allow the voltage clipping which means to let  $V_1 \geq V_{dd}$ , then (2.27) couldn't not be the frequency domain representation of the voltage signal. Since we set the load as short circuit for harmonics it could mean infinite current at the harmonics, which is impossible. By forcing load at shorted harmonics, we are confronted with following cases:

- (i) Current waveform should go to zero immediately whenever voltage clipping occurs (trying to go below zero). This implies a discontinuity at I-V waveforms which is physically not possible.

- (ii) An instant discontinuity forces voltage wave with non-zero harmonics and this breaks the conditions at the load plane such that harmonic impedances become undefined.

- (iii) If the fundamental load magnitude is higher than optimal load, the voltage wave is forced to zero instantly, when maximum drive from input is applied

In figure (2.7), the knee voltage “zero” assumption and the possible trajectories of the I-V curve is plotted in red. Trajectory 1 is analyzed under linear calculations. But in cases where (i-iii) happens, trajectory 2 remains as the only path and, the discontinuity must be defined. Thereby, in order to analyze the overdrive or unconstrained load conditions some assumptions should be released. Before going into that, behavior in path 1 is going to be studied.

Figure 2.7: Zero-knee load-line trajectory for class-B

By setting  $\varphi_1 = 0$ , and  $V_1 = -I_1 Z_1 = -V_{dd}$  in (2.28); we find the optimum load for maximum power and efficiency expressed in (2.29 - 2.30).

$$R_{opt,B} = Z_1 = \frac{2V_{dd}}{I_{max}} \quad (2.29)$$

$$\eta_{max} = \frac{P_L}{P_{dc}} = \frac{V_{dd}^2 / (2R_{opt,B})}{V_{dd}I_{max}/\pi} = \frac{\pi}{4} \approx \%78.5 \quad (2.30)$$

Due to the current direction adopted in figure 1, the equation (2.28) is re-written for the maximum drive at optimum load in (2.31).

$$V_d(t) = V_{dd} - V_{dd}\cos(2\pi f_0 t) ; V_d(\theta) = V_{dd} - V_{dd}\cos(\theta) \quad (2.31)$$

The current and voltage waveforms drawn on top of each other is given in figure (2.8), and the correlation with the I-V curve presented in figure (2.7) can be easily interpreted, whereas path 2 in figure (2.7) is absent.

Figure 2.8: Class-B voltage and current waveforms normalized to their peak value ( $R_{opt} = 1, V_{dd} = 0.5, I_{max} = 1$ )

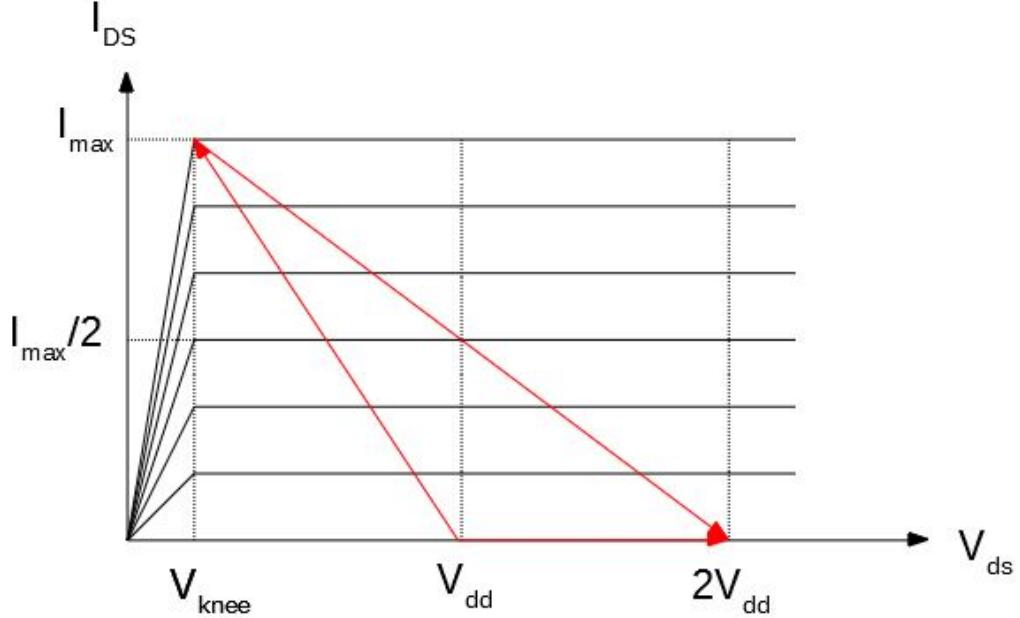

In order to encapsulate the overdrive cases in which voltage or current clipping occurs, a knee-region model must be used. Generally, the transistor I-V curve, so-called “fan diagram” looks like in figure (2.9). Dynamic load-line of class-A and B drawn over the figure, as well.

So far, in our review, the region where the drain voltage drops down the knee voltage is not considered, whereas practical linear RF power output and the efficiency is limited by the knee region. Though linearity is not only dependent on the how much the amplifier’s operation is into the knee region, the strongest constraint seems as the knee region due to neglected gate and drain nonlinearities. In Rhodes’ work [17],

Figure 2.9: Non-zero knee voltage fan diagram

this discontinuity is modeled with a simple delta function. This model is given by equations (2.32) - (2.33) as for a quick reference.

$$H(\theta) = -I_{max}\varepsilon\delta(\theta) \quad ; 0 \leq \theta \leq 2k\pi \quad (2.32)$$

Where  $\varepsilon$  is the proportionality constant of delta discontinuity for the drain current. We chose to re-write the discontinuity at  $\theta = 0$  to be consistent with our analysis approach of which the transition from linear to knee region is at this point, whereas it is defined at  $\theta = \frac{\pi}{2}$  in [17]. Equation (2.33) shows the cosine series form. (2.34) is the current waveform after superposition of the delta discontinuity.

$$H(\theta) = \frac{-I_{max}\varepsilon}{(2\pi)} \left[ 1 + 2\cos(\theta) + 2 \sum_{n=2,3,4,\dots}^{\infty} \cos(n\theta) \right] \quad (2.33)$$

$$\tilde{i}_d(\theta) = i_d(\theta) + H(\theta) \quad (2.34)$$

The modified efficiency, optimum load, RF output power equations for the class-B loading according to (2.34) can be written as in (2.35 - 2.38).

$$P_L = \frac{I_{max}}{(4\pi)}(\pi - 2\varepsilon)V_{dd} \quad (2.35)$$

$$P_{DC} = \frac{I_{max}}{(4\pi)}(2 - \varepsilon)V_{dd} \quad (2.36)$$

$$\hat{R}_{opt} = \frac{2V_{dd}}{I_{max}} \left( \frac{\pi}{\pi - 2\varepsilon} \right) \quad (2.37)$$

$$\hat{\eta}_{max} = \frac{\pi}{4} \left( \frac{1 - 2\varepsilon/\pi}{1 - \varepsilon/2} \right) \quad (2.38)$$

Efficiency and optimum load change vs. proportionality constant are plotted in figure (2.10).

Figure 2.10: Normalized optimum load and efficiency change vs  $\varepsilon$  factor

By showing this model, we are not justifying the accurateness but emphasizing the effect of knee transition on efficiency. From figure 2.10, it is easily understood that optimum load and efficiency aggressively react to even a small perturbation of drain current. Efficiency approaches from %78 to %58 and optimum required load rises to nearly threefold. In short, the model of the knee region becomes particularly impor-

tant when it comes to drive the PA into saturation region. There are various studies which are involving behavioral or purely mathematical models such as [23, 24, 25]. The brief discussion of this simple zero-knee model is provided for better comprehension of the following sections of the thesis.

Having class-A and B discussion above, we can continue with the class A/B analysis which is the most used class group in practice because of the gain advantages. Up to now, gain is not considered as a parameter for discrimination of classes so as in literature. The gain of the amplifier is an important metric in practical applications as much as power and efficiency but the discussion of gain enforces to account for the gate and drain relation together. We are not going to elaborate on the gain in the theoretical analysis. With very practical thinking, as the conduction angle decreases the gain proportionally decreases since for the same drive level, less fundamental power is generated at the output. The current conduction angle is an important parameter for the drain and CCA(current conduction angle) derivation will be illustrated.

CCA is angular time portion that the transistor drain conducts current. In figure 2.11, the conducting cycle in a period is illustrated with the even current function as it is done in class-B analysis. Equation (2.39) shows the waveform mathematical expression as a piecewise continuous function, where  $I_{pk}$  is a temporary variable used to resemble cosine function [26]. In equations (2.40)-(2.42), CCA definition in terms of  $I_{dq}$  auxiliary drain bias current and  $I_{max}$  is derived. (2.43) gives the fourier series expansion coefficients as in (2.5). Since we maintained the even function property of the current, quadrature components  $I_{n,q} = 0$  is still valid.

$$i_d(\theta) = \begin{cases} I_{dq} + I_{pk}\cos(\theta) & ; -\frac{\alpha}{2} \leq \theta \leq \frac{\alpha}{2} \\ 0 & ; \text{otherwise} \end{cases} \quad (2.39)$$

$$i_d(\theta = 0) = I_{max} = I_{dq} + I_{pk} \quad , \text{by figure 2.11} \quad (2.40)$$

$$i_d\left(\theta = \frac{\alpha}{2}\right) = 0 = I_{dq} + I_{pk}\cos\left(\frac{\alpha}{2}\right) \quad , \text{by figure 2.11} \quad (2.41)$$

$$\cos\left(\frac{\alpha}{2}\right) = -\frac{I_{dq}}{I_{max} - I_{dq}} \quad (2.42)$$

Figure 2.11: Current waveform with  $\alpha$  conduction angle

$$I_n = \begin{cases} \frac{I_{max}}{2\pi} \frac{2\sin\left(\frac{\alpha}{2}\right) - \alpha\cos\left(\frac{\alpha}{2}\right)}{1 - \cos\left(\frac{\alpha}{2}\right)} & ; n = 0 \\ \frac{I_{max}}{2\pi} \frac{\alpha - \sin(\alpha)}{1 - \cos\left(\frac{\alpha}{2}\right)} & ; n = 1 \\ \frac{2I_{max}}{\pi} \frac{\sin\left(n\frac{\alpha}{2}\right)\cos\left(\frac{\alpha}{2}\right) - n\sin\left(\frac{\alpha}{2}\right)\cos\left(n\frac{\alpha}{2}\right)}{n(n^2 - 1)[1 - \cos\left(\frac{\alpha}{2}\right)]} & ; n \geq 2 \end{cases} \quad (2.43)$$

From series coefficients shown in (2.43), it can be easily confirmed that the harmonic amplitudes and phases are strongly dependent on the CCA. Figure (2.12), shwos the current harmonic magnitudes,  $I_0, I_1, I_2, I_3$  normalized to  $I_{max}$  with respect to conduction angle, where  $I_0$  is the DC current.

Figure (2.12) plots the conduction angle from 0 to  $2\pi$ , but the class A/B conduction angle is defined in between  $\pi$  to  $2\pi$ . From (2.43) we see the current fundamental component also varies with  $\alpha$  thereby fundamental optimum resistive load changes, respectively. It is necessary to re-state the assumption that we impose short-circuit condition for the load impedance seen by higher harmonics.

Figure (2.13) illustrates the fundamental optimum load change versus conduction angle  $\frac{\pi}{2} \leq \alpha \leq 2\pi$ . Illustration regime is selected such that the scaling of the graph

Figure 2.12: Conduction angle versus normalized harmonic amplitudes.

remains in reasonable limits. The optimum load deviates from the class-A, or B load around  $\%7$  downwards, at maximum, for  $\pi \leq \alpha \leq 2\pi$ . On the other hand, for  $\alpha \leq \frac{\pi}{2}$ , optimum load increases, drastically. As mentioned before, the advantage for class A/B over class-B is the increased available gain due to the conduction angle increase. If the bias point is closer to class-B, then it is referred as "deep" class A/B [13]. The deep class A/B is the most encountered version in CW(continuous working) amplifiers since biasing transistor close to class-A causes overheating for even short periods, in which no RF signal input is present. Below the conduction angle of  $\pi$ , available maximum RF power decreases due to maximum voltage swing limited to  $V_{dd}$  by the short harmonic load constraints.

Figure 2.13: Conduction angle versus optimum load.

For the conduction angle values below  $\pi$ , other high-efficiency operation modes exist. Whereas high-efficiency classes are categorized with respect to harmonic loading conditions in addition to the conduction angle bias point. One of these high efficiency modes, class-J, is the particular interest of this thesis. Other well-known high efficiency modes, class C, F and  $F^{-1}$  will be roughly mentioned under explanation of class-J theory.

Consequently, this section covered the basic amplifier classes, A, B, A/B which forms the fundamental basis of other classes. The terms, such as knee voltage, transistor operating regimes, conduction angle, load harmonic analysis, vccs model, optimum resistive load, RF output power and efficiency, are explained, in detail with reference to literature. The reader may apply to the resources of this section for further knowledge, whereas the short review of this section is predicted to be sufficient for the upcoming chapters of this thesis.

## 2.2 Load-Line Theory of Ideal Linear Amplifier

In the previous section, we analyzed the conventional PA classes with a purely resistive fundamental load. In particular, only the optimum load which provides highest RF power, was evaluated. This section considers the fundamental complex load conditions and its systematic explanation by the "Load-line theory of ideal amplifier". This chapter actually re-states the article [18] and, the chapter 2.4 of the book [16] in our formulation. In terms of understanding the complex loading condition, this section conveys strong intuition to reader.