REDEFINING PASSIVE ELECTRONICS ON RFICS VIA STRESS-INDUCED

RESTRUCTURING OF PATTERNED THIN FILMS

by

RAYAN BAJWA

Submitted to the Faculty of Engineering and Natural Sciences

in partial fulfilment of

the requirements for the degree of Doctor of Philosophy

Sabanci University

July 2023

© Rayan Bajwa 2023

All Rights Reserved

## ABSTRACT

# REDEFINING PASSIVE ELECTRONICS ON RFICS VIA STRESS-INDUCED RESTRUCTURING OF PATTERNED THIN FILMS

RAYAN BAJWA

Ph.D. Thesis, July 2023

Thesis Supervisor: Prof. Dr. Murat Kaya Yapıcı

**Keywords:** Electrostatic actuator, RF-MEMS switch, thin film, residual stress, bending, bilayer, 3D wavy cantilevers, Microfabrication, Polymer encapsulation, Wafer-level packaging, Microelectromechanical devices, RF-MEMS, Inductor, Q-factor

Manufacturing three dimensional (3D) structures at microscale has been a major challenge in semiconductor fabrication, which heavily relies on planar layer by layer processing of materials. This essentially restricts the geometry of any electronic component to be built on-chip to two dimensions, often at the expense of extreme performance degradation. For instance, passive elements such as inductors or transformers when fabricated monolithically on integrated circuit (IC) chips need to be shape-modified from conventional 3D solenoidal shape to planar two-dimensional spiral shape. While this approach allows easy integration, passive elements built on-chip often suffer from significant reduction in performance compared to their 3D, mm-scale, discrete counterparts.

Aiming to overcome these issues, this thesis herein puts forward a novel IC-compatible technological platform to fabricate complex 3D shapes monolithically on IC chips, thereby opening up new opportunities for the semiconductor industry to explore. We show that residual stresses that are commonly observed in metal thin films used in IC fabrication can be indeed leveraged to achieve controllable out-of-plane bending, thus indicating a pathway to build complex 3D shapes at microscale. Fundamentally, stacking two thin film layers with different residual stress values can lead to bending in either upward or downward direction, once the film stack is released from the substrate. By utilizing this fundamental concept, we have built the 3D variants of two types of electronic components commonly used in radio-frequency circuits i.e., inductors and electromechanical switches. We show that shape modification via stress engineering allows maneuvering the device geometry in three dimensions, hence liberating an additional degree of freedom in the device design process and allowing a better performance optimization, as opposed to traditional 2D-restricted designs. Specifically, our 3D inductors show approximately 300% performance improvement (quantified using quality factor) compared to planar coils. Similarly, RF switches fabricated using the proposed methodology operate at 4 times lower actuation voltage and exhibit 5x better isolation, in comparison with devices available in market. In general, the devices we fabricated outperform the commercial state-of-the-art by a large margin, and these performance improvements are crucial for realizing future high data-rate wireless networks.

In addition, while we have shown the application of proposed technology to only two types of electronic components, the platform is highly scalable and can easily accommodate other components such as capacitors or transformers etc. As such, we believe our efforts indicate an important landmark towards the implementation of high-performance on-chip RF passive devices that are essential for next generation communication systems.

## ÖZET

# PASİF RFIC ELEKTRONİĞİNE İNCE FILMLERİN GERİNİM KONTROLLÜ ŞEKİLLENDİRİLMESİYLE YENİ BİR BAKIŞ

RAYAN BAJWA

Doktora Tezi, Temmuz 2023

Tez Danışmanı: Prof. Dr. Murat Kaya Yapıcı

**Anahtar Kelimeler:** Elektrostatik eyleyiciler, RF-MEMS anahtar, İnce film, Kalıntı gerinim, Eğilme, Çift tabaka, 3B dalgalı kırışlar, Mikrofabrikasyon, Polimer enkapsülasyonu, Altlık seviyesinde paketleme, Mikroelektromekanik aygıtlar, RF-MEMS, İndüktör, Q-faktörü

Üç boyutlu yapıların (3B) mikro ölçekte fabrikasyonu, malzemelerin genellikle katman katman işlendiği yarı iletken teknolojisi için hep bir zorluk oluşturmuştur. Çip üstü elektronik bileşenlerin geometrisini iki boyutlu bir düzlemede kısıtlayan bu durumun, performans üzerinde ciddi bir etkisi olabilmektedir. Entegre devre (IC) çipleri üzerinde monolitik olarak üretilen indüktör veya transformatör gibi bobin elemanlarının klasik üç boyutlu selenoid şeklärinden düzlemsel iki boyutlu spirallere dönüştürülmesi gerekliliği buna bir örnektir. Tümleşimleri daha kolay olsa da, bu yaklaşımla üretilen pasif bileşenler üç boyutlu (3B), milimetre üstü, muadillerine kıyasla performanslarında önemli eksiklik gösterir.

Bu sorunun üstesinden gelmek amacıyla, bu çalışmamızda, karmaşık 3B şeklärin entegre devre uyumlu monolitik üretimleri için yeni bir teknolojik platform

geliştirilmiştir. Entegre devre üretimindeki metal ince filmlerin üzerinde yaygın olarak gözlemlenen gerinimlerin, düzlem dışı bükülme elde etmek için kontrol edilebilir şekilde kullanılabileceği ve böylece mikro ölçekte karmaşık 3B şekiller oluşturulabileceği gösterilmektedir. Temel yaklaşımımız, farklı kalıntı gerinim değerlerinde üst üste getirilen iki ince film katmanının altlık yüzeyinden ayrıldıktan sonra yukarı veya aşağı yönde bükülmesine dayanmaktadır. Buradan hareketle, radyo frekans devrelerinde yaygın olarak kullanılan iki tür elektronik bileşenin, induktörlerin ve elektromekanik anahtarların 3B varyantları oluşturulmuştur. Gerinim kontrolü sayesinde aygıt geometrisiyle üç boyutta oynayabilmenin, tasarım sürecinde ek bir serbestlik derecesi getirdiğini ve geleneksel tasarımlara göre daha iyi bir performans optimizasyonunu mümkün kıldığı gözlenmiştir. Özellikle, üretilen 3B induktörler düzlemsel muadillerine karşı neredeyse 3 kat daha yüksek Q-faktörü göstermiştir. Ayrıca önerdiğimiz metodla üretilen RF anahtarlar, ticari ürünlere kıyasla 4 kat daha az çalışma voltajı ve 5 kat daha iyi izolasyon sergilemektedir. Mevcut ticari ürünlere kıyasla gösterilen bu önemli performans farkları, geliştirilen sensörlerin yüksek hızlı kablosuz ağ uygulamaları için kullanılabilirliğine işaret etmektedir.

Önerilen teknoloji iki farklı türde elektronik bileşene uygulanmış olmakla birlikte, oldukça öbeklenebilir olan bu yaklaşımın kapasitörler veya transformatörler gibi başka temel bileşenler için de kolayca uygulanabileceği öngörmektedir. Bu sayede, çalışmalarımızın yansması olarak yeni nesil yüksek hızlı iletişim sistemleri için kritik olan yüksek performanslı RF bileşenlerin üretimine yönelik mihenk taşı oluşturan kazanımların elde edildiği değerlendirilmektedir.

## **ACKNOWLEDGEMENT**

I am immensely grateful to my supervisor, Dr. Murat Kaya Yapici, for his unwavering guidance, mentorship, and belief in my abilities. His exceptional expertise, dedication, and patience have been instrumental in shaping the direction of my research. His insightful feedback, constant encouragement, and high expectations have motivated me to explore new frontiers and strive for excellence. I am truly fortunate to have had the privilege of working under his guidance, and I am grateful for the trust he placed in me throughout this endeavor.

I would also like to extend my heartfelt appreciation to the members of my thesis committee, Prof. Ibrahim Tekin and Prof. Serhat Yesilyurt, for their valuable insights and thoughtful suggestions that have significantly enriched my research. Additionally, I would like to express my deepest gratitude to my lab mates, whose support made this journey not only intellectually stimulating but also immensely enjoyable. Their insightful discussions, constructive feedback, and shared experiences have been invaluable in shaping my research and personal growth. I am indebted to their friendship, encouragement, and willingness to collaborate, which fostered a vibrant research environment that continuously pushed me to excel.

Last but certainly not least, I owe an immeasurable debt of gratitude to my family. Their unwavering love, unwavering support, and unwavering belief in me have been the foundation upon which I have built my academic journey. Their sacrifices, encouragement, and constant motivation have been the driving force behind my perseverance and success. I am forever grateful for their presence in my life and for the countless ways in which they have nurtured and inspired me.

## **DEDICATION**

Dedicated to my wife for her love and support.

## TABLE OF CONTENTS

|                                                                                                                                           |             |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| <b>ACKNOWLEDGEMENT.....</b>                                                                                                               | <b>vii</b>  |

| <b>DEDICATION .....</b>                                                                                                                   | <b>viii</b> |

| <b>LIST OF FIGURES.....</b>                                                                                                               | <b>xii</b>  |

| <b>LIST OF TABLES .....</b>                                                                                                               | <b>xvi</b>  |

| <b>1. INTRODUCTION .....</b>                                                                                                              | <b>1</b>    |

| 1.1. Summary of Contributions.....                                                                                                        | 3           |

| 1.1.1. Fabrication of High-Performance RF Inductors via Stress-Engineering<br>(Chapter 3) 3                                               |             |

| 1.1.2. Development of High-Performance RF-MEMS Switches via Stress-<br>Engineering (Chapter 4) .....                                      | 4           |

| 1.1.3. Machine Learning-Based Design and Optimization of RF-MEMS<br>Components (Chapter 5).....                                           | 5           |

| <b>2. CONTROLLABLE RESTRUCTURING OF THIN FILMS BASED ON<br/>INTRINSIC STRESS .....</b>                                                    | <b>7</b>    |

| 2.1. Concept of Intrinsic Stress-Induced Self-Assembly .....                                                                              | 7           |

| 2.2. Design and Mechanical Modelling .....                                                                                                | 9           |

| 2.3. Fabrication and Characterization .....                                                                                               | 11          |

| <b>3. ORIGAMI-INSPIRED FABRICATION OF HIGH-PERFORMANCE<br/>WAFER-LEVEL PACKAGED THREE-DIMENSIONAL RADIO-FREQUENCY<br/>INDUCTORS .....</b> | <b>16</b>   |

| 3.1. Introduction.....                                                                                                                    | 16          |

| 3.2. Design Concept.....                                                                                                                  | 18          |

| 3.3. Modeling and Fabrication of Self-folded Inductors .....                                                                              | 20          |

|           |                                                                                                    |           |

|-----------|----------------------------------------------------------------------------------------------------|-----------|

| 3.4.      | Wafer-level Packaging of Self-folded Inductors .....                                               | 21        |

| 3.4.1.    | Thick SU-8 Film Process Development .....                                                          | 22        |

| 3.4.2.    | Quasi-static Encapsulation of Self-folded Inductors .....                                          | 23        |

| 3.5.      | High-frequency Characterization of Inductors .....                                                 | 25        |

| <b>4.</b> | <b>WAVY-SHAPED ELECTROSTATIC MICROACTUATORS AS HIGH-PERFORMANCE RADIO-FREQUENCY SWITCHES .....</b> | <b>30</b> |

| 4.1.      | Introduction.....                                                                                  | 30        |

| 4.2.      | Controllable Fabrication of Wavy Cantilevers .....                                                 | 33        |

| 4.3.      | Wavy Cantilevers as High-Performance RF switches .....                                             | 37        |

| 4.4.      | Fabrication of Wavy Switches .....                                                                 | 40        |

| 4.5.      | Electromechanical Response of Wavy Switches .....                                                  | 40        |

| 4.6.      | High-Frequency Performance of Wavy Switches .....                                                  | 42        |

| 4.7.      | Reliability and Power Handling of Wavy Switches .....                                              | 44        |

| 4.8.      | Comparison with the State-of-the-art .....                                                         | 48        |

| 4.9.      | Material and Methods .....                                                                         | 50        |

| 4.9.1.    | Wavy Switch Fabrication .....                                                                      | 50        |

| 4.9.2.    | Electromechanical Characterization .....                                                           | 50        |

| 4.9.3.    | High-Frequency Characterization .....                                                              | 51        |

| 4.9.4.    | Lifetime and Linearity Experiments.....                                                            | 51        |

| 4.10.     | Supplementary Data.....                                                                            | 52        |

| 4.10.1.   | Stress Characterization .....                                                                      | 52        |

| 4.10.2.   | Wavy Beam Configuration.....                                                                       | 53        |

| 4.10.3.   | Bending Simulation .....                                                                           | 53        |

| 4.10.4.   | Electromechanical Simulation of Wavy Switches .....                                                | 54        |

| 4.10.5.   | High-Frequency Simulations of Wavy Switches .....                                                  | 56        |

| 4.10.6.   | Thermomechanical Simulation.....                                                                   | 56        |

| 4.10.7.   | Parameters of Fabricated Wavy Test Structures and Switches .....                                   | 56        |

|                                                                                                               |           |

|---------------------------------------------------------------------------------------------------------------|-----------|

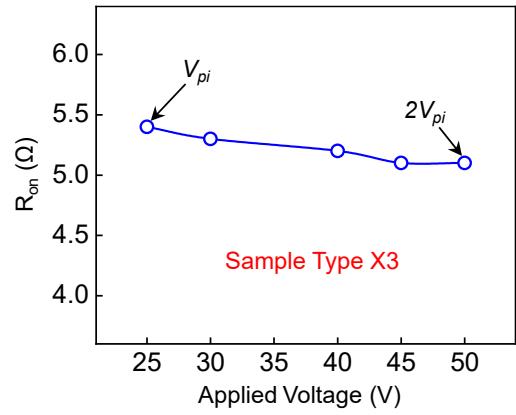

| 4.10.8. ON-state Switch Resistance at Various Voltage Levels.....                                             | 57        |

| 4.10.9. Measurement Setup .....                                                                               | 58        |

| 4.10.10. Supplementary High-Frequency Measurement Results .....                                               | 60        |

| <b>5. MACHINE LEARNING BASED MODELING AND OPTIMIZATION OF RADIO-FREQUENCY ELECTROMECHANICAL DEVICES .....</b> | <b>62</b> |

| 5.1. Introduction.....                                                                                        | 62        |

| 5.2. Proposed Multi-Objective Optimization Methodology .....                                                  | 65        |

| 5.2.1. Problem Definition .....                                                                               | 65        |

| 5.2.2. Finite Element Modeling Framework .....                                                                | 66        |

| 5.2.3. Surrogate Modeling .....                                                                               | 66        |

| 5.2.4. Multi-Objective Optimization .....                                                                     | 68        |

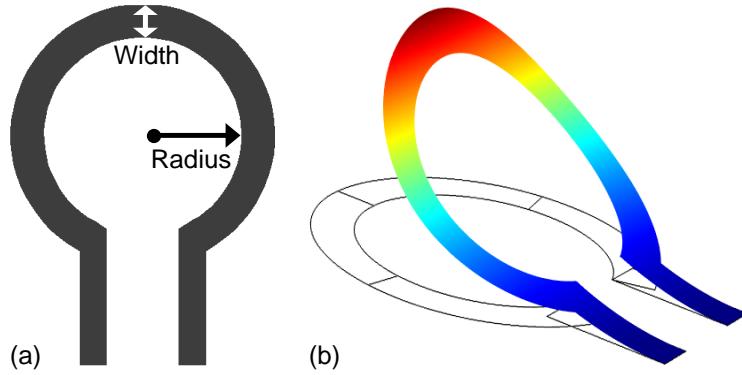

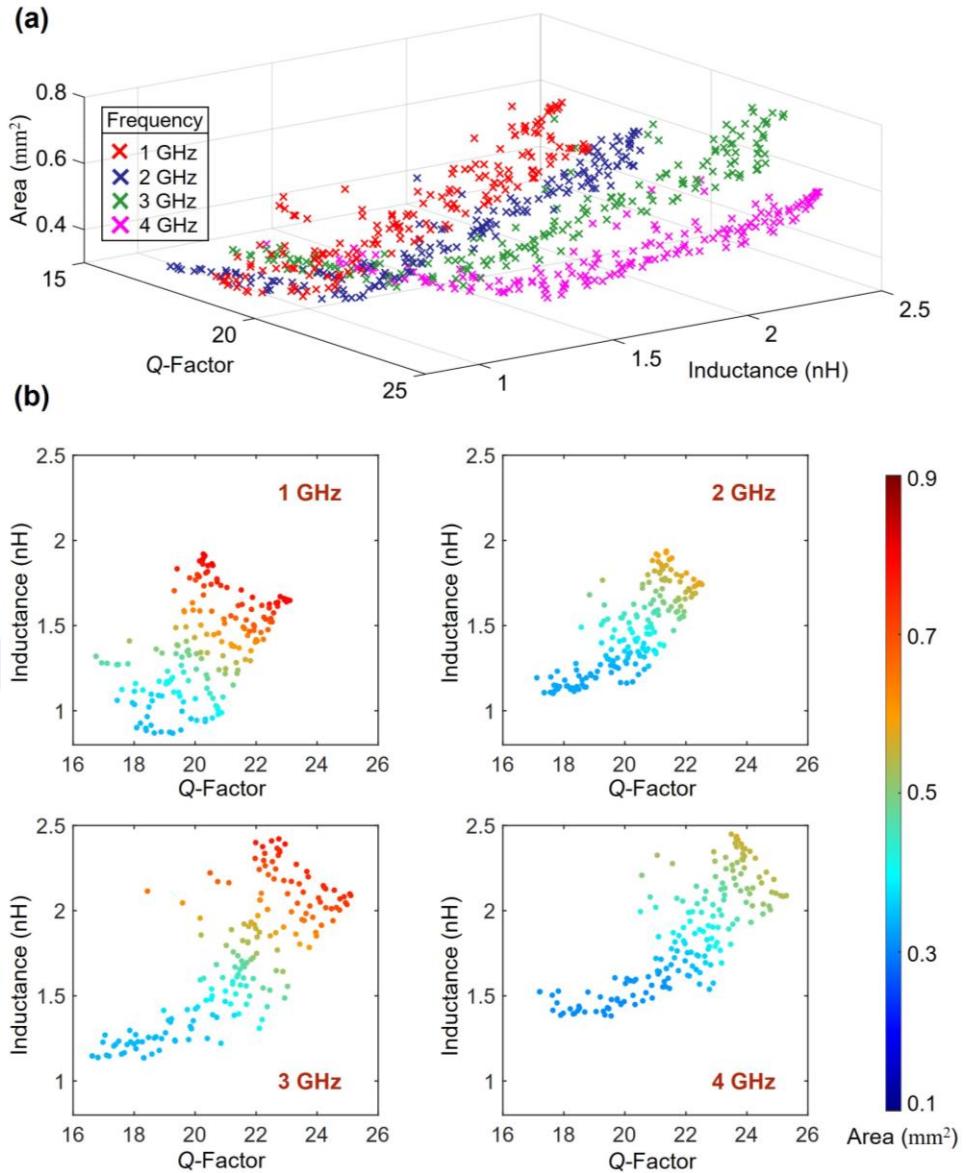

| 5.3. Case Study: RF-MEMS Suspended Inductor Optimization .....                                                | 69        |

| 5.3.1. Finite Element Modeling of RF-MEMS Loop Inductors .....                                                | 71        |

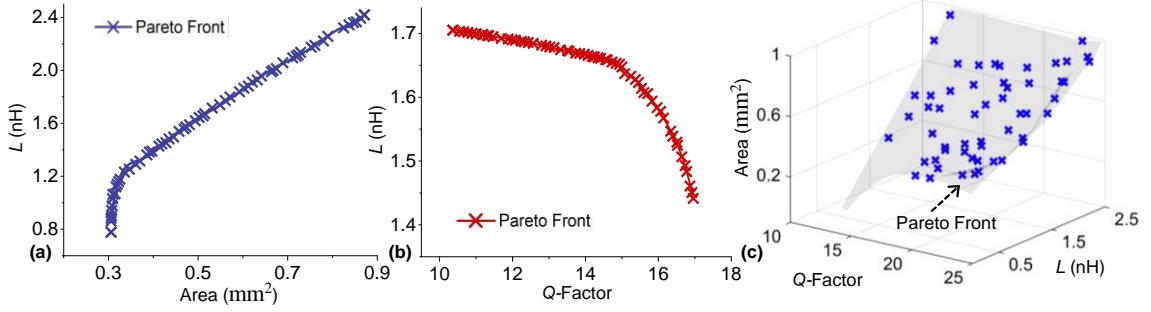

| 5.3.2. Multi-Objective Optimization .....                                                                     | 71        |

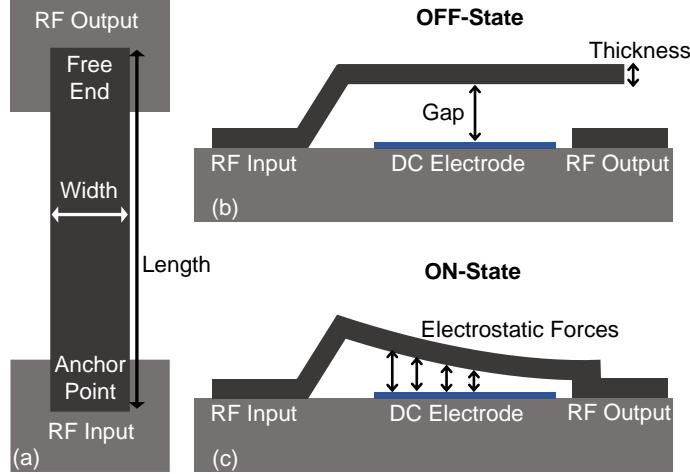

| 5.4. Case Study: RF-MEMS Switch Optimization.....                                                             | 75        |

| 5.4.1. FEM Modeling of RF-MEMS Switches.....                                                                  | 76        |

| 5.4.2. Multi-Objective Optimization .....                                                                     | 78        |

| <b>6. CONCLUSIONS.....</b>                                                                                    | <b>78</b> |

| <b>BIBLIOGRAPHY .....</b>                                                                                     | <b>84</b> |

## LIST OF FIGURES

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1. Concept of residual stress-induced restructuring technique.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3  |

| Figure 1.2. Transforming traditional planar RF coils into out-of-plane wafer-level packaged inductors. ....                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4  |

| Figure 1.3. Schematic illustration of proposed wavy switch and its geometrical differences compared to traditional flat-cantilever switch. ....                                                                                                                                                                                                                                                                                                                                                                                                      | 5  |

| Figure 1.4. ML-based design and optimization methodology for RF-MEMS components. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6  |

| Figure 2.1 Intrinsic stress-induced post-release bending in multi-layer thin film stacks due to tensile and compressive stress gradients.....                                                                                                                                                                                                                                                                                                                                                                                                        | 8  |

| Figure 2.2. Concept of bending angle ( $\theta$ ) based on angular displacement.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9  |

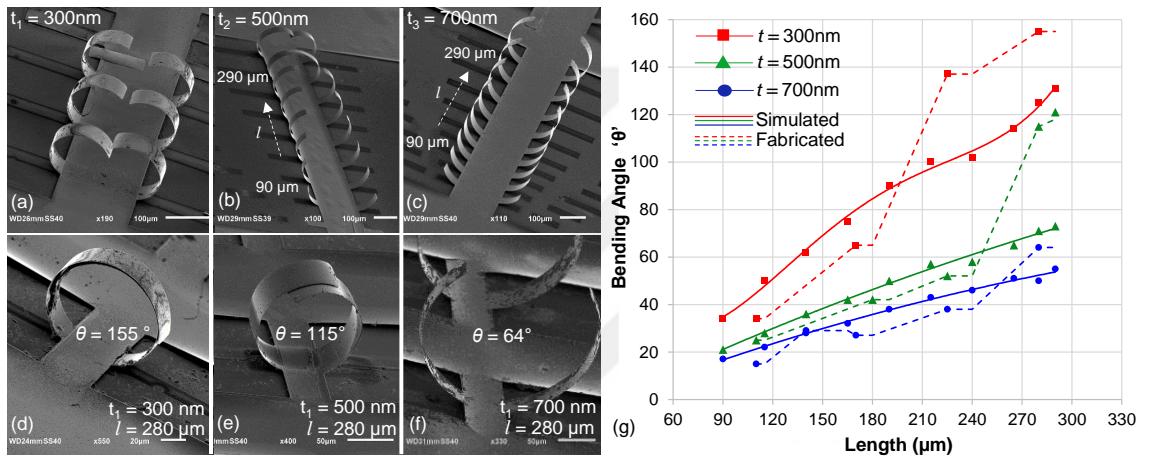

| Figure 2.3. FEA results indicating intrinsic stress induced bending for a set of cantilevers with lengths “ $l$ ” varying from 90 $\mu\text{m}$ to 290 $\mu\text{m}$ and thickness of: (a) $t_1 = 300 \text{ nm}$ ; (b) $t_2 = 500 \text{ nm}$ ; and (c) $t_3 = 700 \text{ nm}$ ; (d-g) zoom-in views of 280 $\mu\text{m}$ -long, two-sided cantilevers for the same thicknesses $t_1$ , $t_2$ , $t_3$ , respectively; and (g) trend of simulated bending angles ( $\theta$ ) with respect to the length of cantilevers for varying thicknesses..... | 11 |

| Figure 2.4. Side-view SEM images of released cantilevers with corresponding bending angles ( $\theta$ ) for three different lengths ( $l_1 = 110 \mu\text{m}$ , $l_2 = 170 \mu\text{m}$ , $l_3 = 225 \mu\text{m}$ ) and thicknesses $t_1 = 300 \text{ nm}$ (a-c); $t_2 = 500 \text{ nm}$ (d-f); $t_3 = 700 \text{ nm}$ (g-i).....                                                                                                                                                                                                                    | 12 |

| Figure 2.5. (a) SEM images of two-sided Cu/Cr cantilever arrays consisting of varying cantilever lengths and fabricated at three different film thicknesses; (b) SEM images of 280 $\mu\text{m}$ long cantilevers fabricated at thicknesses of 700 nm, 500 nm and 300 nm; and (c) comparison of bending data obtained from simulations and fabrication results for cantilevers. ....                                                                                                                                                                 | 13 |

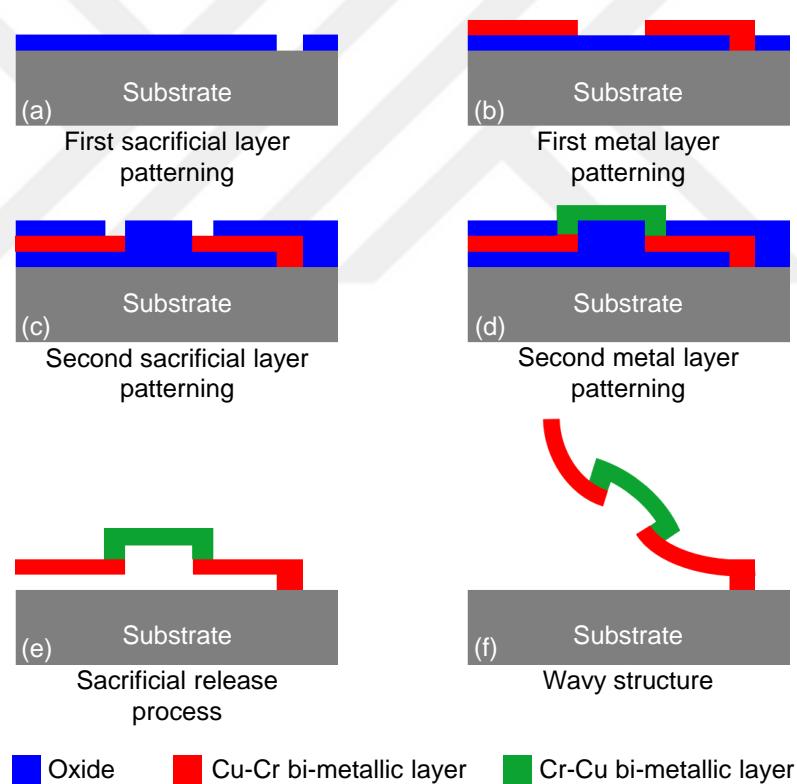

| Figure 2.6. Fabrication process flow of a three-segment cantilever showing opposing stress gradients engineered in each segment for realization of wavy structure. ....                                                                                                                                                                                                                                                                                                                                                                              | 14 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

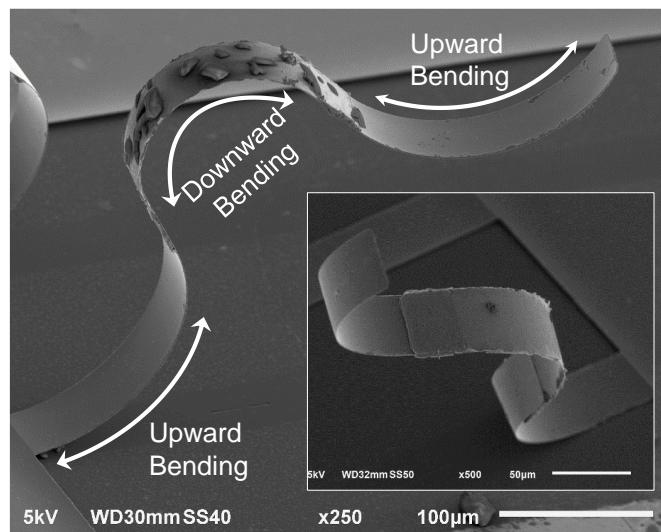

| Figure 2.7. SEM images of a segmented cantilever showing opposing stress gradients engineered in each segment to controllably realize upward and downward deflections and form a complex wavy-shaped structure.....                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15 |

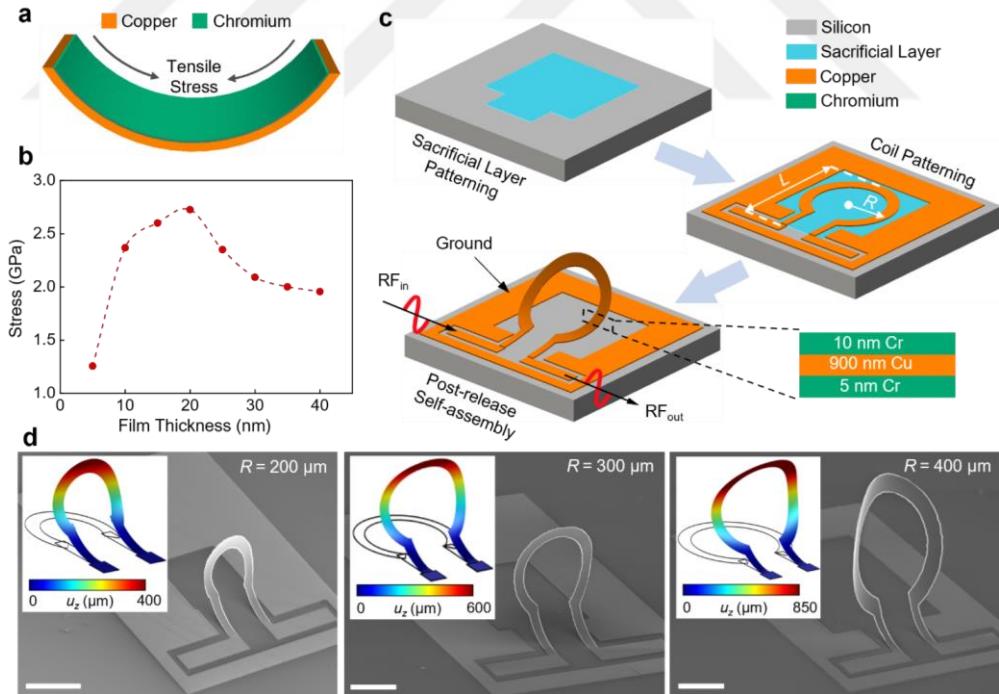

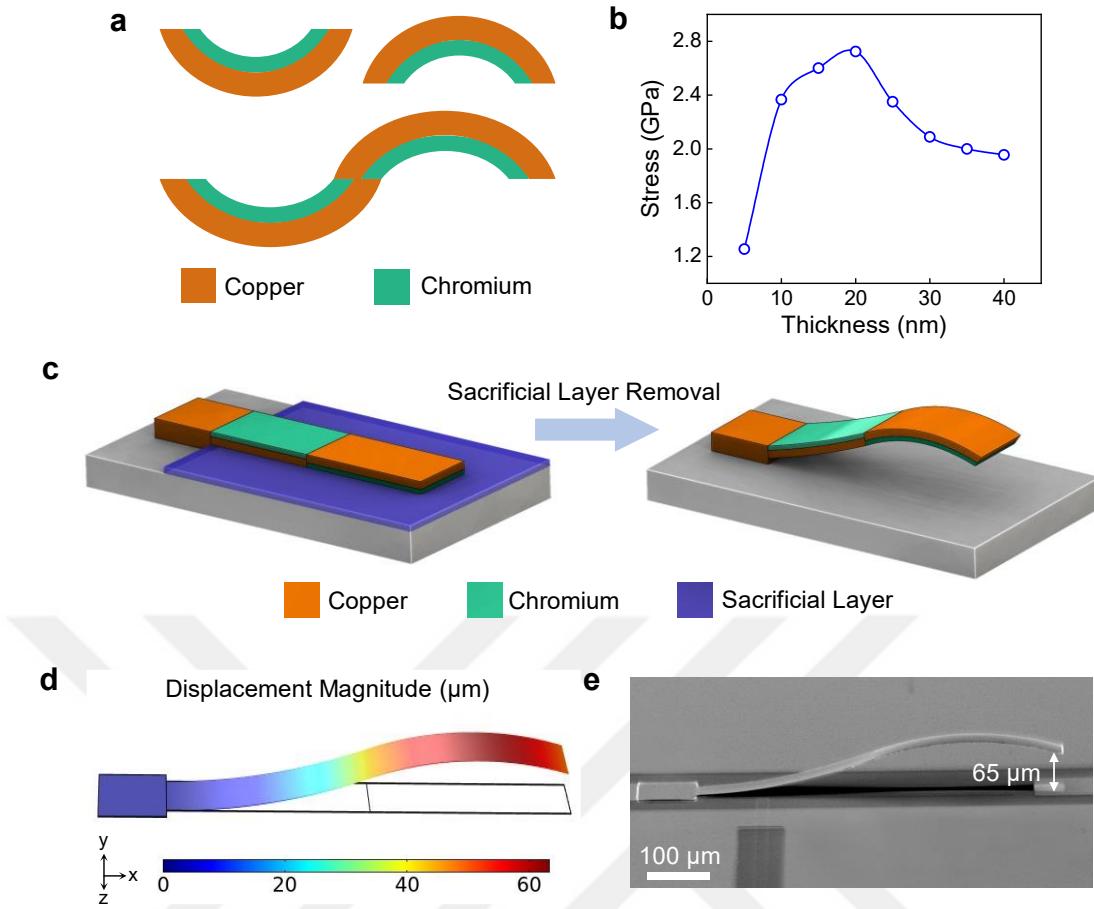

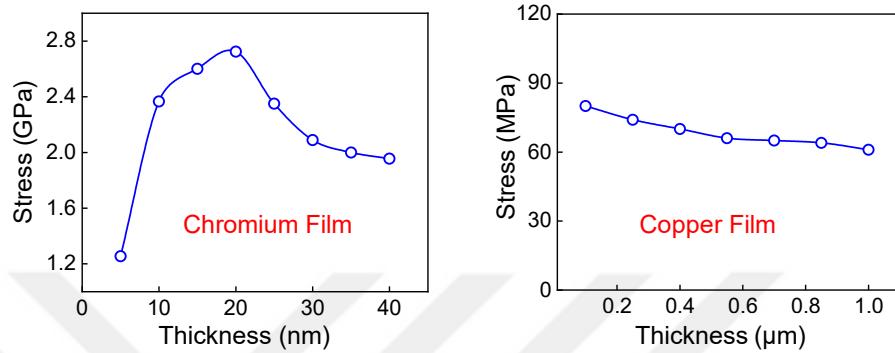

| Figure 3.1. Schematic demonstration of the development of stress-induced self-assembled ring inductors: (a) illustration of bending in copper-chromium thin film stacks; (b) characterized residual stress in evaporated chromium thin film for thickness up to 40 nm. As a convention, tensile stress is represented with positive values; (c) fabrication process for self-assembled inductors; (d) simulation results and SEM images of the designed ring inductors, with ring radius varying from 200-400 $\mu\text{m}$ . Scale bar = 300 $\mu\text{m}$ .....                                                                                                           | 19 |

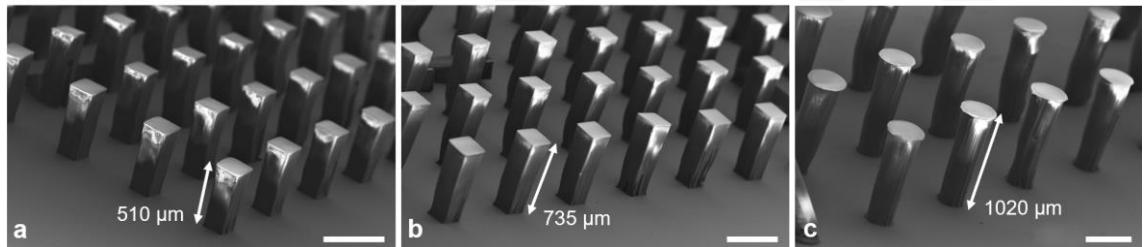

| Figure 3.2. SEM images of SU-8 micro-towers fabricated using volumetric dispensing method: (a) film thickness = 500 $\mu\text{m}$ ; (a) film thickness = 750 $\mu\text{m}$ ; (c) film thickness = 1000 $\mu\text{m}$ . Scale bar = 500 $\mu\text{m}$ .....                                                                                                                                                                                                                                                                                                                                                                                                                  | 22 |

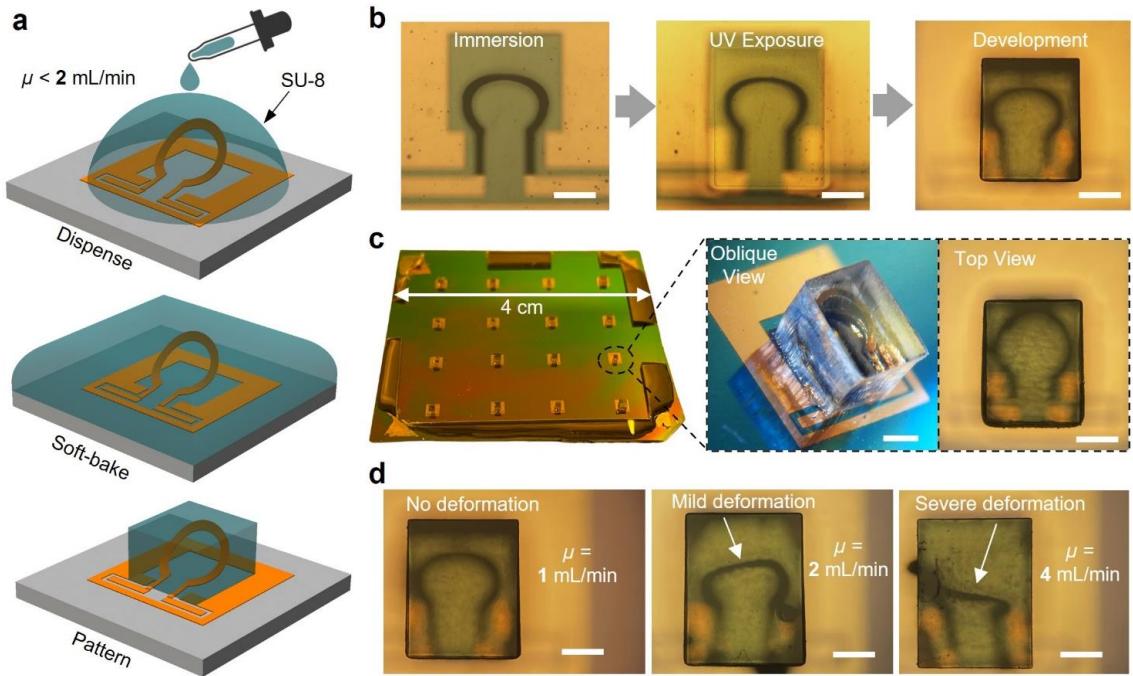

| Figure 3.3. Polymer packaging process for the suspended ring inductors: (a) schematic illustration of the encapsulation process; (b) optical microscope images of 300 $\mu\text{m}$ ring inductor during different stages of the encapsulation process; (c) a fabricated sample (4x4 $\text{cm}^2$ ) with 16 packaged bent-up inductors; (d) influence of SU-8 dispense rate on the inductor shape. At dispense rates of 2 $\text{mL min}^{-1}$ and beyond, deformation in the inductors was observed. Scale bar = 300 $\mu\text{m}$ . .....                                                                                                                                | 25 |

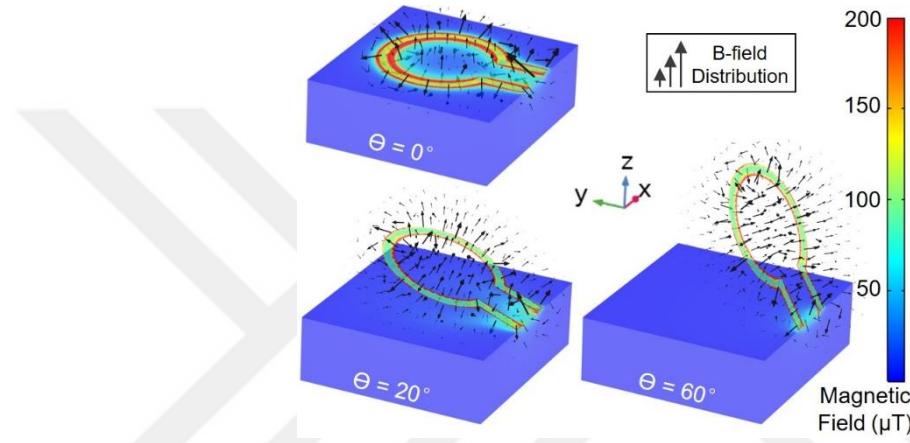

| Figure 3.4. Variation in the <i>B</i> -field region of inductor with bending angle. <i>B</i> -field region shifts away from the substrate with increasing $\Theta$ .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26 |

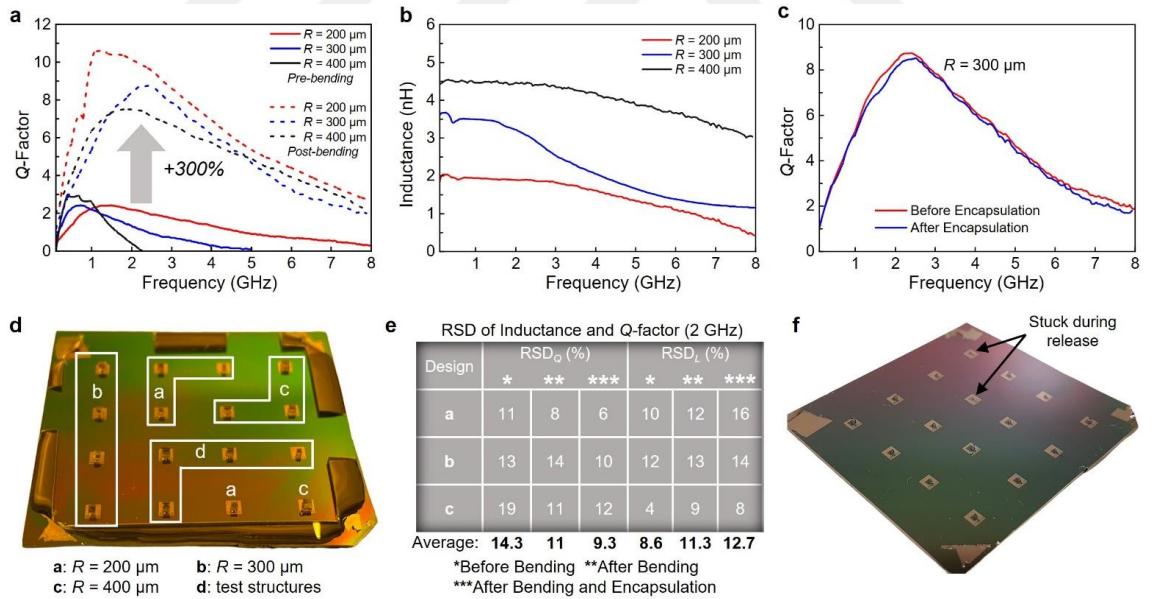

| Figure 3.5. Performance characterization of fabricated inductors: (a) measured <i>Q</i> -factor of the fabricated inductors, before and after the bending; (b) measured inductance of the fabricated inductors; (c) <i>Q</i> -factor of the 300 $\mu\text{m}$ ring inductor before and after the SU-8 encapsulation; (d) distribution of different ring inductor designs on a 4x4 $\text{cm}^2$ silicon substrate; (e) relative standard deviation of inductance and <i>Q</i> -factor for different ring inductors before bending, after bending, and after bending and encapsulation; (f) stiction problem, which occurred in some samples during the drying process. .... | 27 |

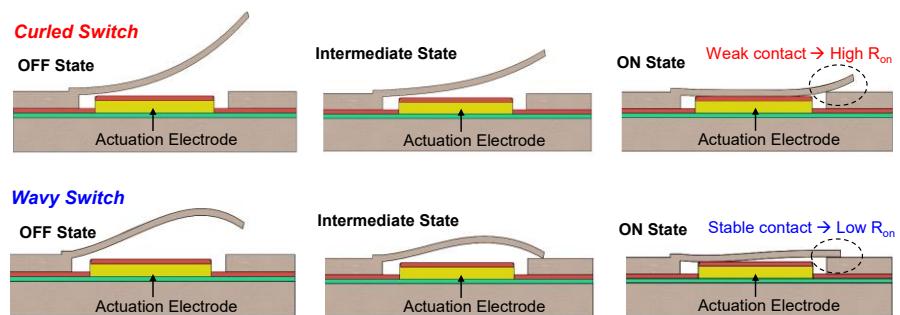

| Figure 4.1. Schematic diagram elaborating the operation of the proposed wavy switches and other curled 3D cantilever switches available in the literature. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32 |

| Figure 4.2. (a) Stress-induced bending in Cu and Cr thin film stacks; (b) characterized variation of residual stress in evaporated Cr with film thickness (as a convention, tensile nature of stress is indicated by positive stress values); (c) assembly of flat cantilever into a wavy beam through a combination of Cu and Cr thin films; (d-e) simulated bending                                                                                                                                                                                                                                                                                                       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| profile and SEM image of a 600 $\mu\text{m}$ long wavy cantilever achieved by modulating the stress in Cu-Cr thin film stack. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34 |

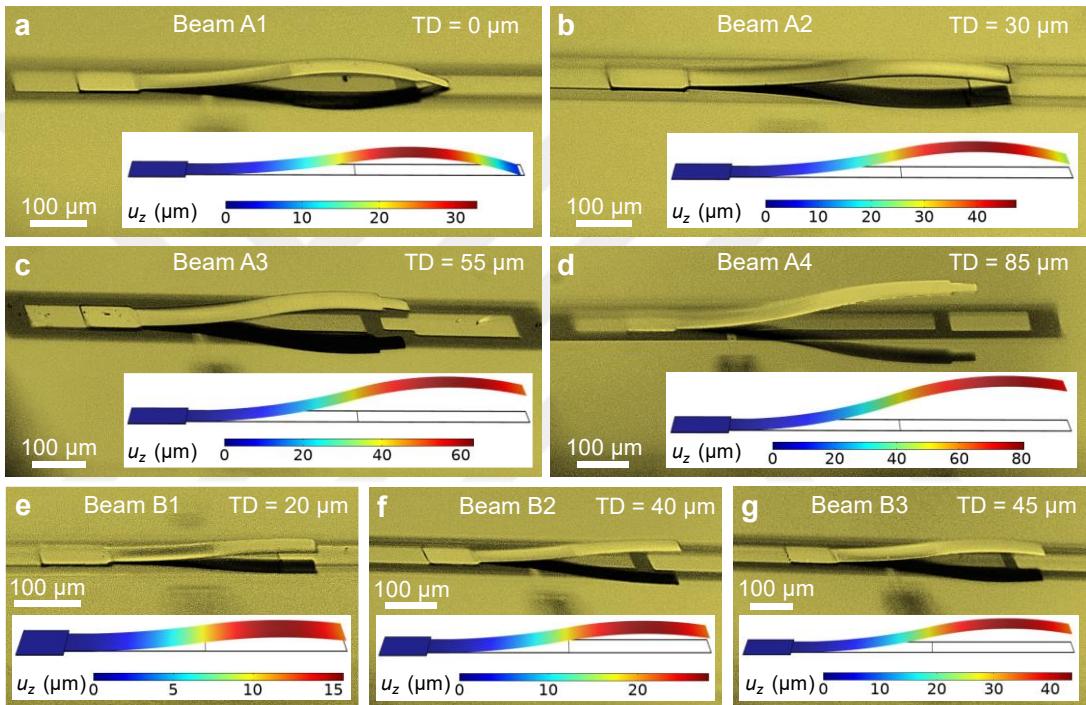

| Figure 4.3. Simulated and measured variations in wavy beam shape with (a) different stress conditions and (b) different beam lengths. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35 |

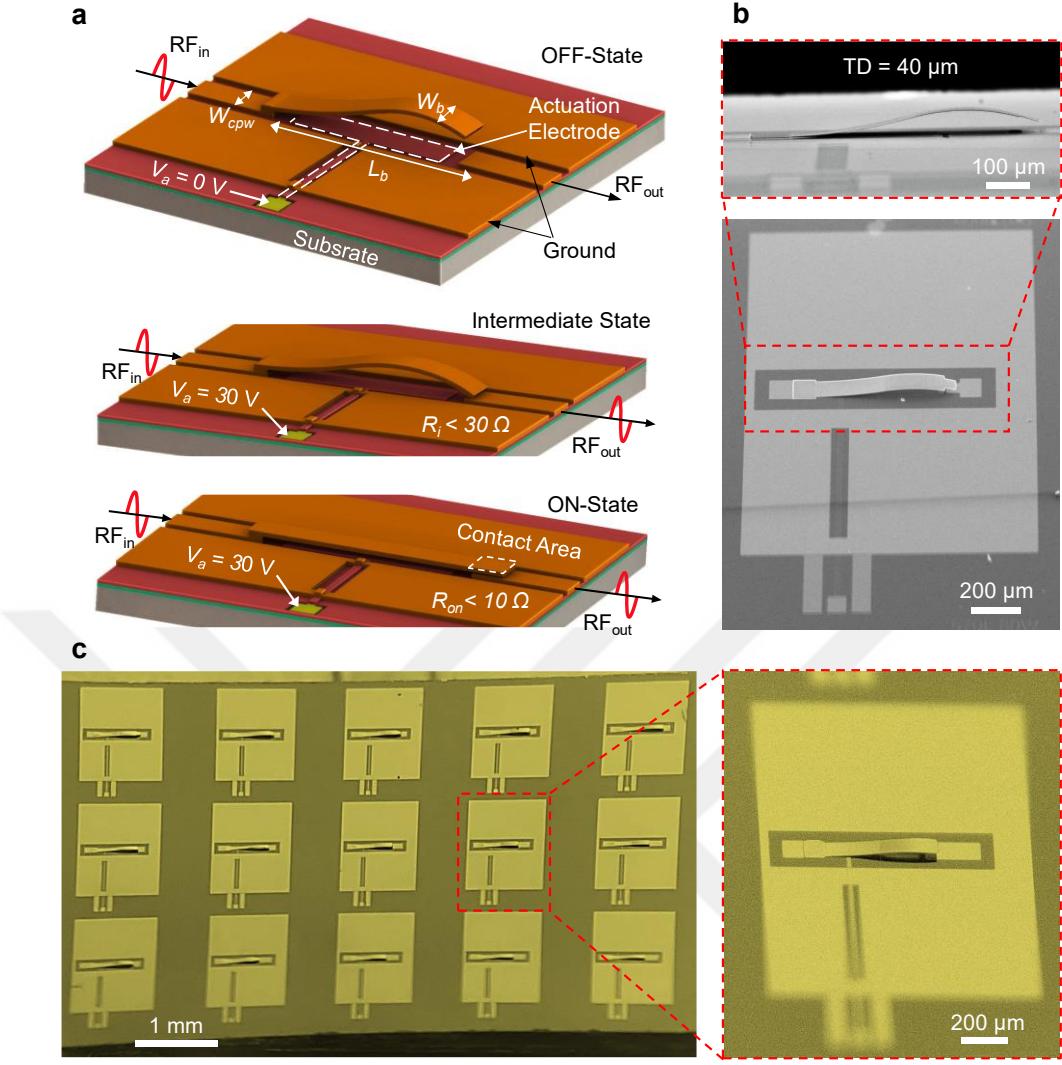

| Figure 4.4. (a) Design and operating principle of the proposed wavy switches; (b) SEM image of the proposed wavy switch with a TD of 40 $\mu\text{m}$ ; (c) a sample with a high fabrication yield containing 15 fully functional RF switches.....                                                                                                                                                                                                                                                                                                                                                                                                         | 37 |

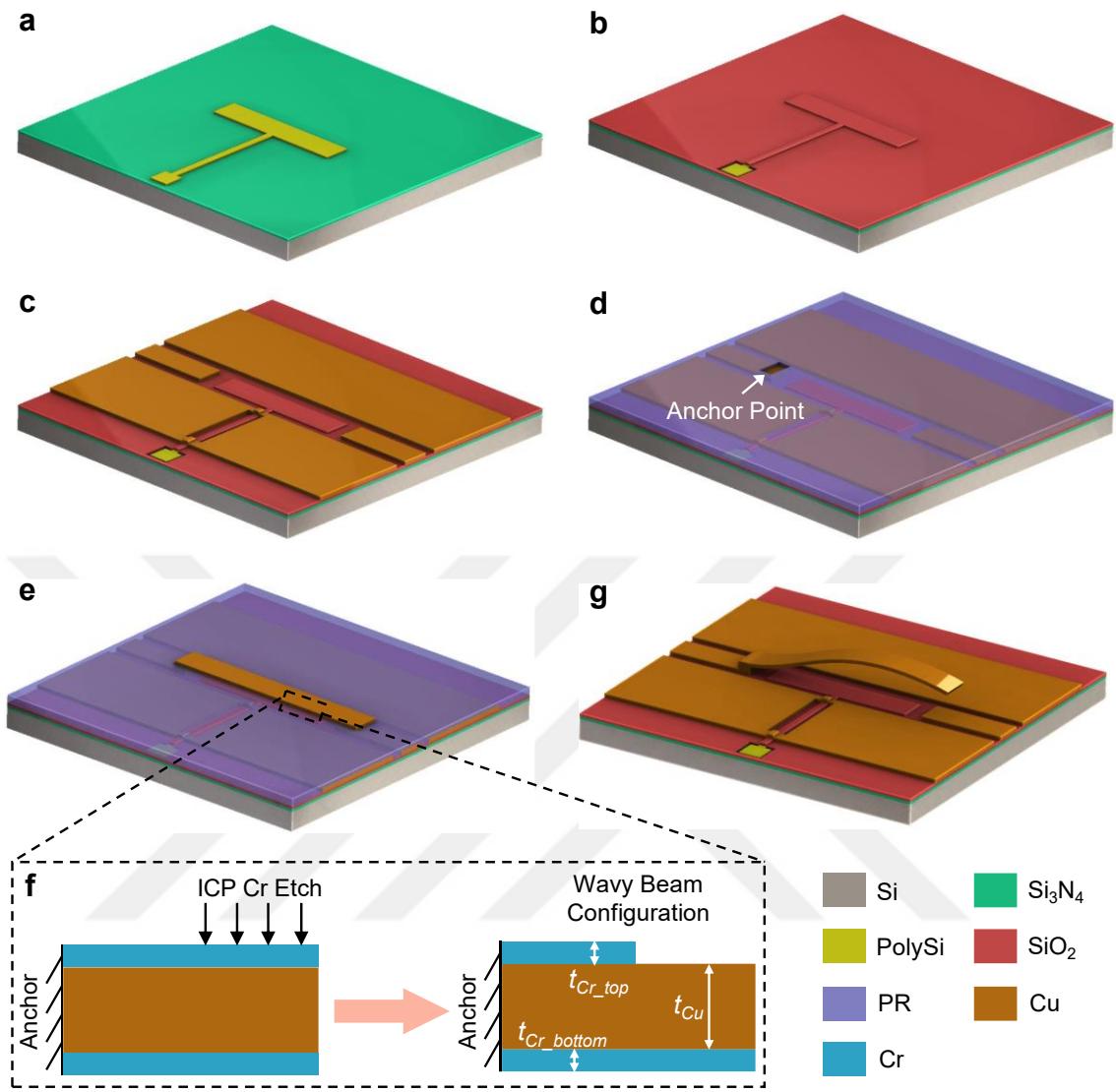

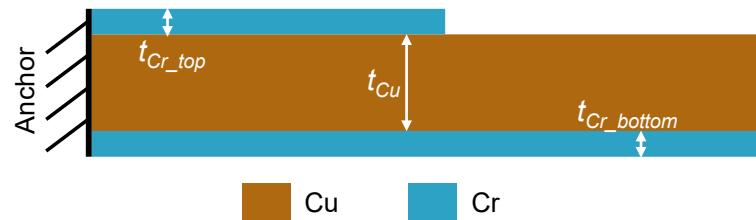

| Figure 4.5. Fabrication of wavy RF switches: (a) coating HR-Si substrate with $\text{Si}_3\text{N}_4$ passivation layer and patterning of polysilicon DC actuation electrode; (b) $\text{SiO}_2$ insulation layer for DC actuation electrode; (c) patterning CPW structure using copper layer; (d) photoresist sacrificial layer patterning; (e) patterning of thin film stack made of Cu and Cr layers to define the beam; (f) side-view of wavy beam prior to its release shows patterning of top Cr layer using ICP etching, to modulate the stress gradient along beam length; (g) sacrificial layer removal, yielding a wavy-shaped switch beam. .... | 39 |

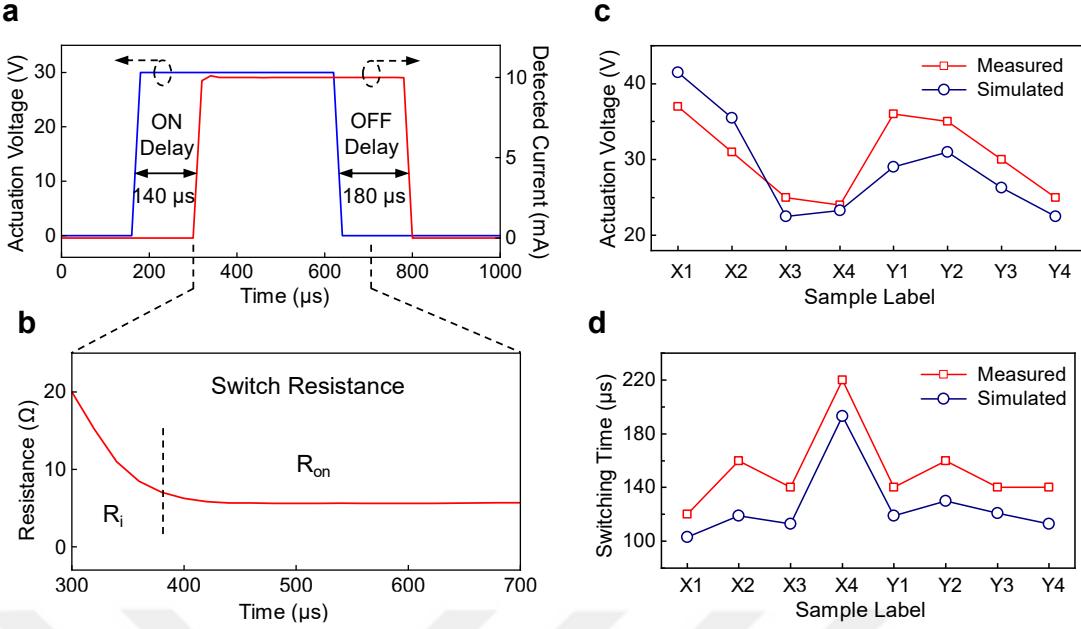

| Figure 4.6. Characterized ON-OFF operation of the fabricated X3-type wavy switch; (b) switch resistance during the switching ON period; (c) measured and simulated actuation voltages of all 8 types of fabricated switches; (d) measured and simulated switching times of all 8 types of fabricated switches.....                                                                                                                                                                                                                                                                                                                                         | 42 |

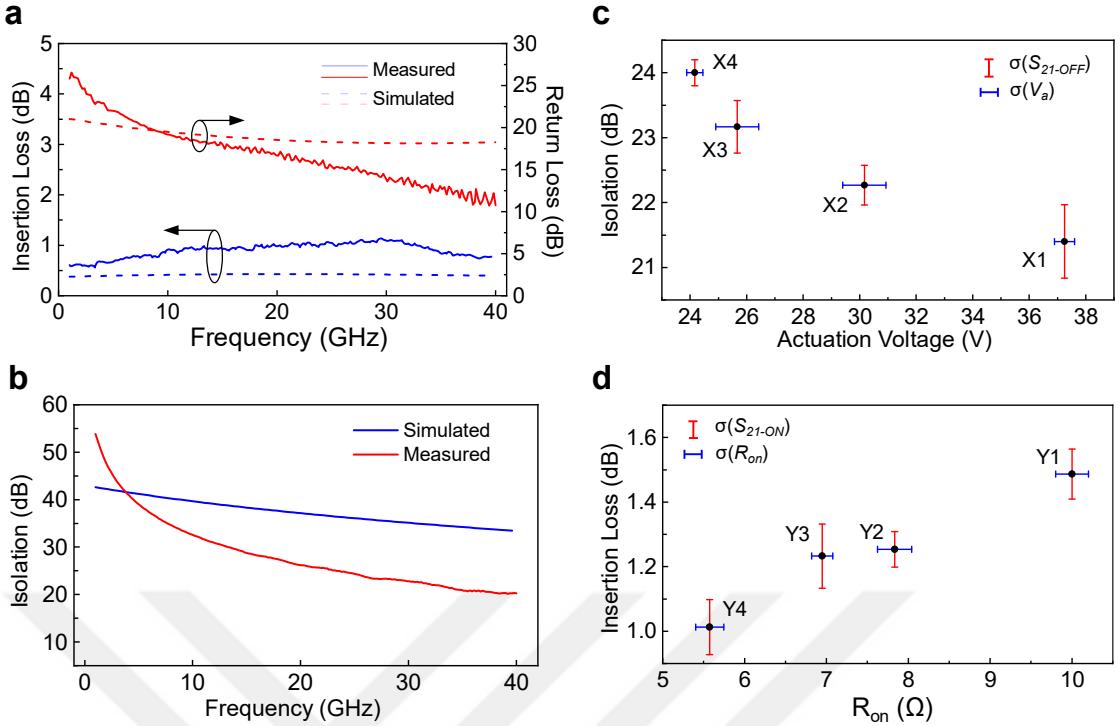

| Figure 4.7. (a) Measured and simulated insertion loss and return loss of X3-type switch; (b) measured and simulated RF isolation of X3-type switch; (c) variation of actuation voltage ( $V_a$ ) and RF isolation ( $S_{21\text{-OFF}} @ 30 \text{ GHz}$ ) among X1-X4-type switches; (d) variation of ON-state switch resistance and insertion losses (@30 GHz) among Y1-Y4-type switches. Standard deviations are calculated by measuring each switch design three times from three different samples. ....                                                                                                                                              | 44 |

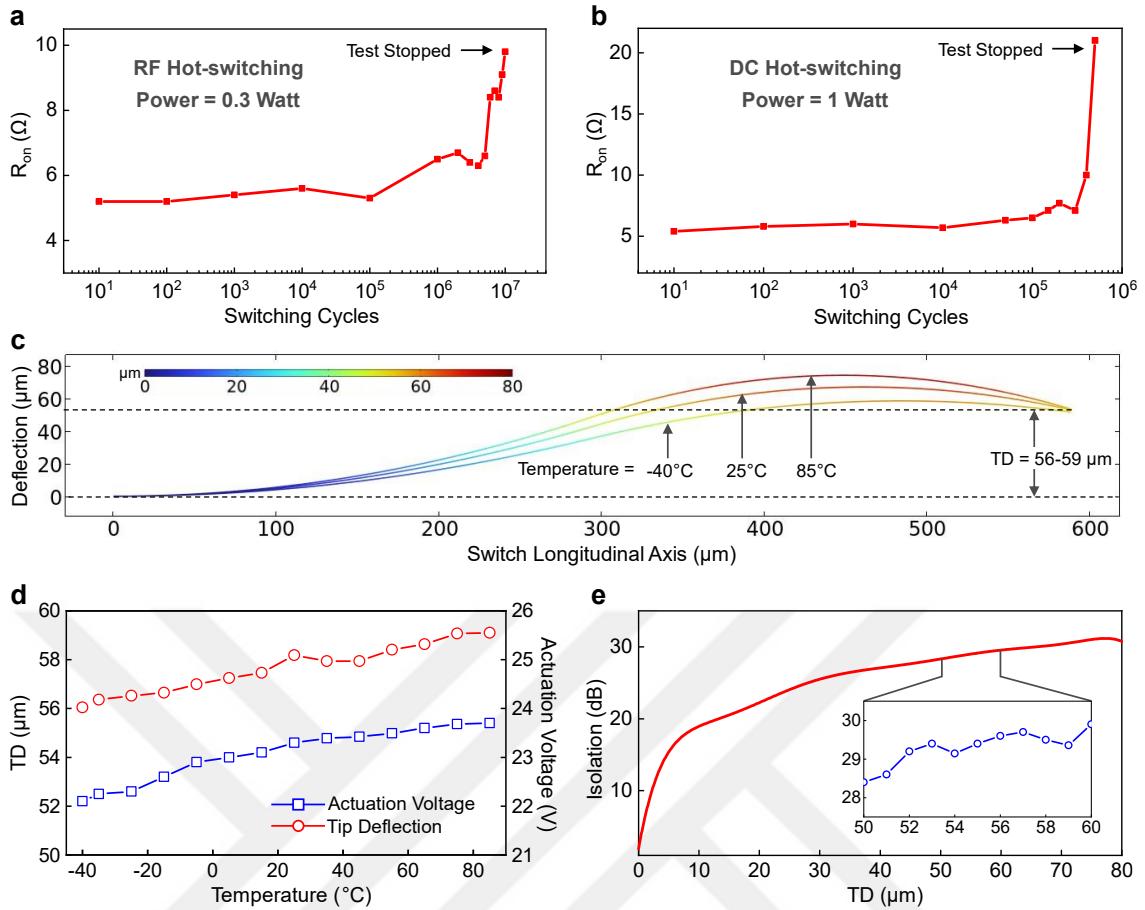

| Figure 4.8. Reliability of the proposed wavy switches: lifetime characterization (a) under an RF power of 0.3 W; (b) under a DC power of 1 W. Tests were stopped when the ON-state resistance ( $R_{on}$ ) crossed 10 $\Omega$ ; (c) sensitivity of the wavy profile of switch X4 to temperature (under the industrial temperature range, i.e., -40 $^{\circ}\text{C}$ to 85 $^{\circ}\text{C}$ ); (d) variation in tip deflection (TD) of switch X4 for temperatures ranging from -40 $^{\circ}\text{C}$ to 85 $^{\circ}\text{C}$ ; (e) simulated RF isolation of switch X4 at different degrees of tip deflection at a frequency of 30 GHz.....          | 46 |

| Figure 4.9. Characterized stresses in evaporated copper and chromium thin films. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53 |

| Figure 4.10. Cross-sectional view of wavy beam structure. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53 |

|                                                                                                                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

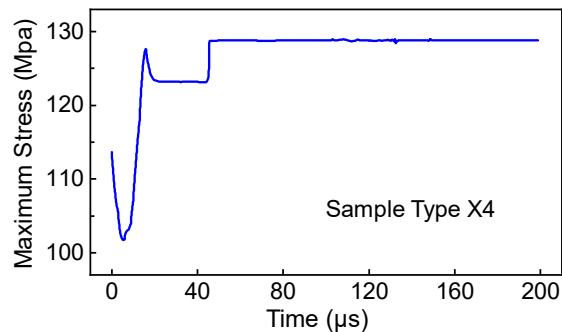

| Figure 4.11. Maximum stress in Switch X4 during actuation. ....                                                                                                                                              | 55 |

| Figure 4.12. Variation of ON-state switch resistance with increasing actuation voltage. ....                                                                                                                 | 58 |

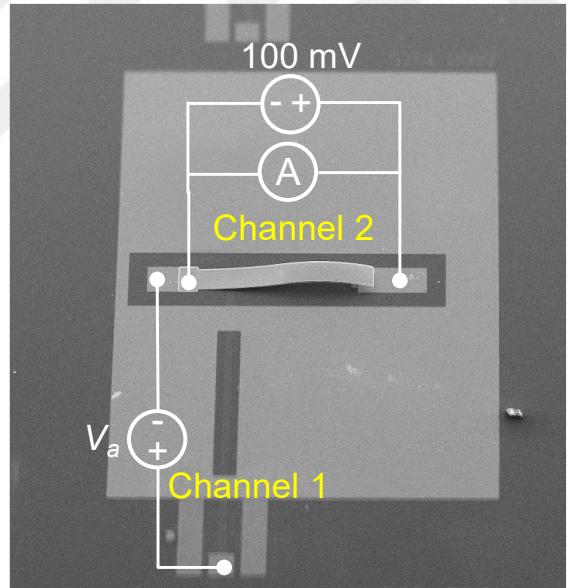

| Figure 4.13. Electromechanical characterization setup using source measurement unit with 2 channels. ....                                                                                                    | 58 |

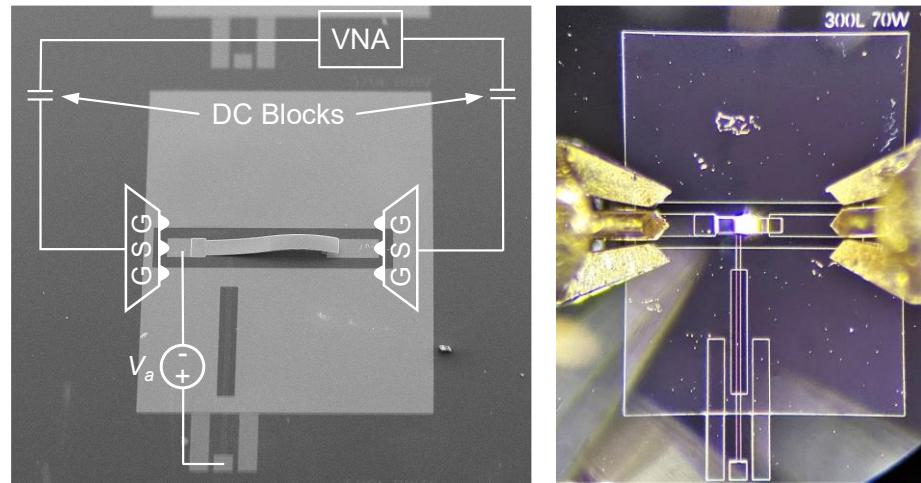

| Figure 4.14. High-frequency characterization setup for the wavy switches. ....                                                                                                                               | 59 |

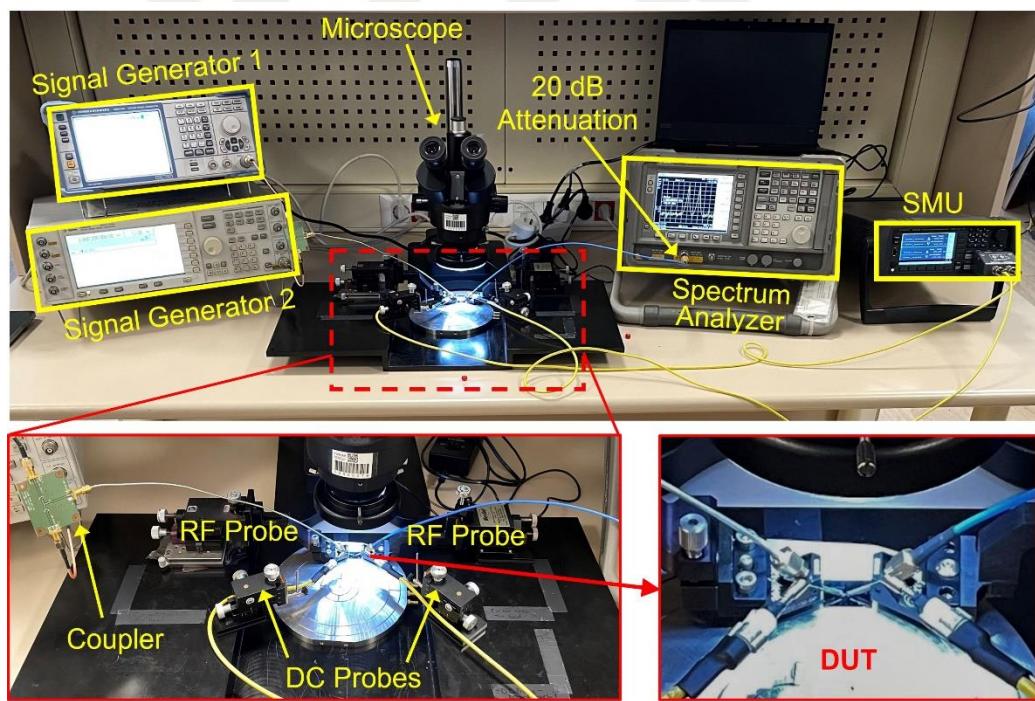

| Figure 4.15. Experimental setup for characterization of switch lifetime and linearity. .                                                                                                                     | 59 |

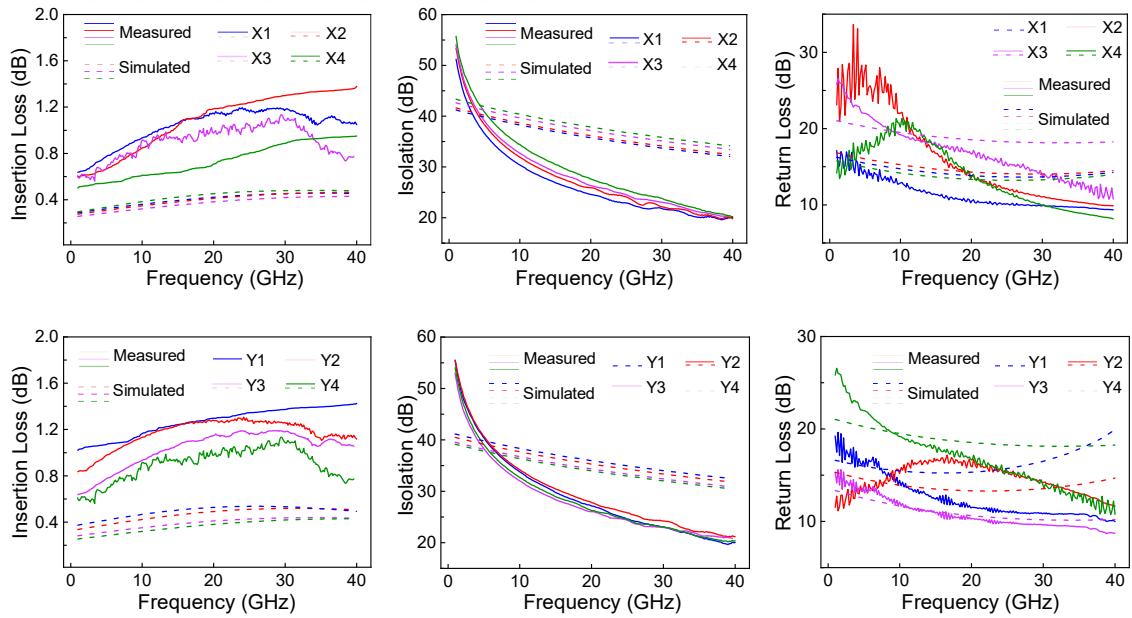

| Figure 4.16. Measured high-frequency responses of all 8 types of fabricated wavy switches. Return loss corresponds to the on-state. ....                                                                     | 60 |

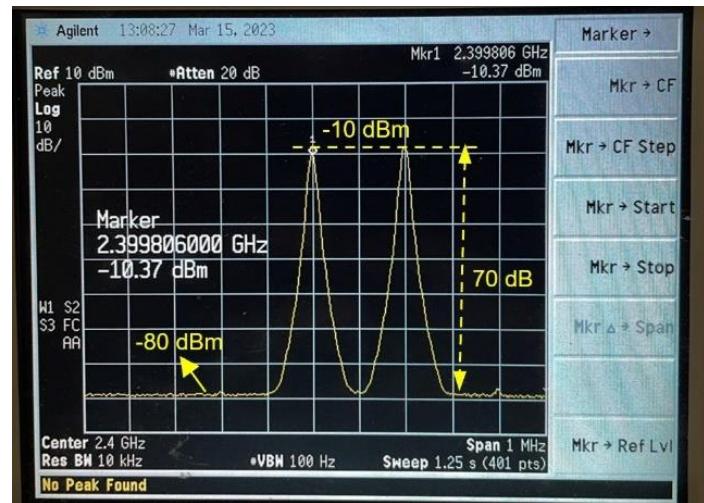

| Figure 4.17. Output at spectrum analyzer during two tone IMD3 experiments for linearity characterization under an input power of 13 dBm. ....                                                                | 61 |

| Figure 4.18. Characterized linearity of proposed wavy switches. ....                                                                                                                                         | 61 |

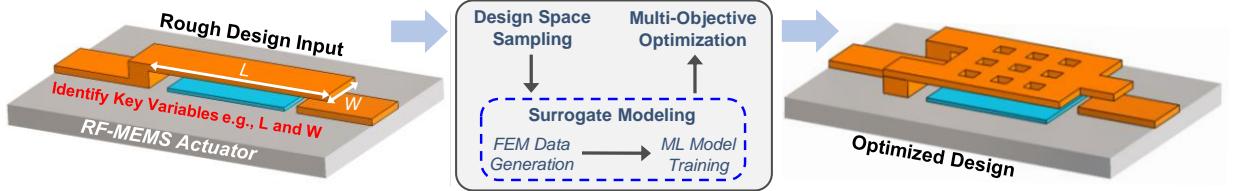

| Figure 5.1. Schematic diagram demonstrating the generic design optimization methodology for RF-MEMS devices switching. ....                                                                                  | 65 |

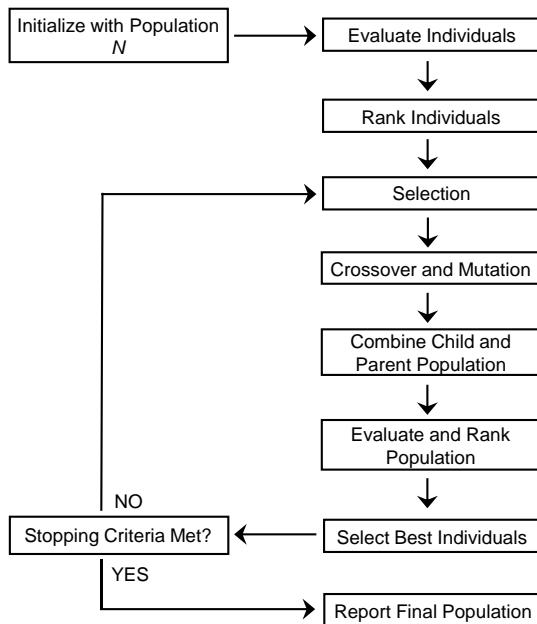

| Figure 5.2. NSGA-II algorithm flowchart [89]. ....                                                                                                                                                           | 68 |

| Figure 5.3. Self-assembled RF-MEMS ring inductor: (a) Top view of the planar ring inductor geometry prior to out-of-plane self-assembly; and (b) post self-assembly view of the deformed ring inductor. .... | 71 |

| Figure 5.4. Non-dominated solution sets for RF-MEMS inductor optimization problem: (a) inductance vs. area; (b) $Q$ -factor vs. inductance; and (c) $Q$ -factor vs. inductance vs. area. ....                | 73 |

| Figure 5.5. Pareto fronts for RF-MEMS inductor at 4 different frequencies between 1-5 GHz: (a) combined pareto plot for all frequencies; and (b) individual pareto plots at different frequencies. ....      | 75 |

| Figure 5.6. Cantilever-based series RF-MEMS switch: (a) top view; (b) side view in OFF-state; and (c) side view in ON-state. ....                                                                            | 78 |

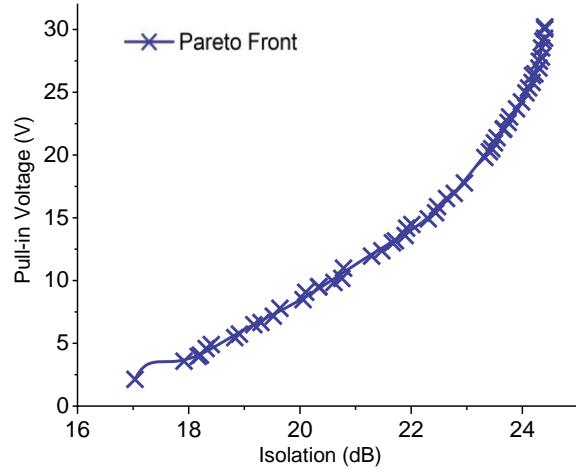

| Figure 5.7. Set of optimal trade-offs between the RF-isolation and pull-in voltage of the cantilever-based series RF-MEMS switch. ....                                                                       | 80 |

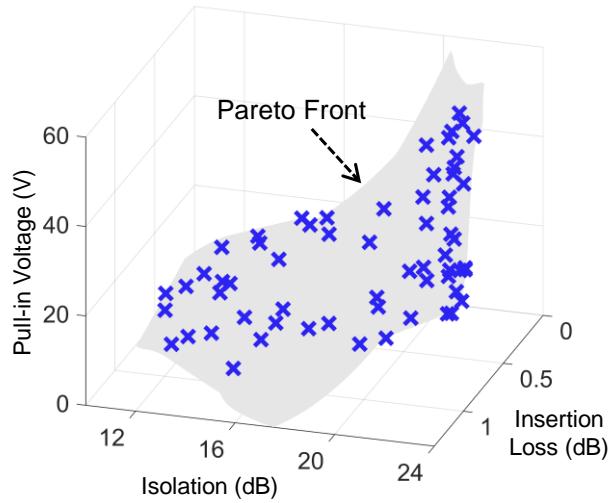

| Figure 5.8. Three-dimensional pareto front demonstrating trade-off between actuation voltage, RF isolation and insertion loses for the RF-MEMS series switch. ....                                           | 81 |

## LIST OF TABLES

|                                                                                      |    |

|--------------------------------------------------------------------------------------|----|

| Table 3.1. Comparison with literature. ....                                          | 29 |

| Table 4.1. Performance comparison of the proposed switches with existing works. .... | 49 |

| Table 4.2. Geometrical parameters of various fabricated wavy beams. ....             | 57 |

| Table 4.3. Parameters of fabricated 8 types of switch samples. ....                  | 57 |

| Table 5.1. Design variables for RF-MEMS inductor.....                                | 70 |

| Table 5.2. Accuracy metrics for meta-models of $L$ and $Q$ . ....                    | 72 |

| Table 5.3. Design variables for RF-MEMS switch. ....                                 | 76 |

| Table 5.4. Accuracy of meta-models of switch's objective functions.....              | 78 |

## 1. INTRODUCTION

Integrated circuits (ICs) are fabricated using planar processing techniques, where thin material layers are stacked and patterned one by one on top of each other to realize circuitry on semiconductor substrates. While such approach has proven to be highly effective in fabricating densely packed active circuitry (transistors) and achieving extreme miniaturization, this near-2D fabrication flow is not ideal to make passive electronic components such as inductors, transformers, which inherently possess a three-dimensional (3D) shape e.g., solenoid. However, these passive electronic components are an integral part of integrated circuit chips particularly those working at radio frequencies, having applications such as in portable wireless devices, military radars, test and measurement equipment etc. To address this integration issue, researchers over the years have modified the shapes of passive components to better fit them in the conventional 2D IC fabrication flow; for instance, RF coils nowadays have planar spiral shapes. By doing so, though these passive components can be easily integrated with transistors on the same chip, they suffer from a large reduction in their performance. In view of this, there has been a plethora of attempts over the span of past 20-25 years, aiming to develop fully IC-compatible processes that could allow us to build three-dimensional electronic components on the same chip as that of transistors, without affecting the standard IC manufacturing flow. While many interesting results have been published in past [1-4], this 3D component integration problem has not been fully solved, since monolithic integration of 3D components comes with a lot of challenges ranging from compatibility issues to device reliability [5].

Among many strategies that have been explored in the past to monolithically fabricate 3D components on ICs, one viable solution could be on-chip strain-induced shape morphing of patterned thin films by controllably leveraging their intrinsic/residual

stresses. ICs are fabricated by stacking thin films one on top of the other, and by nature, each of these thin films has some stress in it. Though this stress is undesirable in any semiconductor fabrication facility, it is indeed unavoidable. However, we realized that this unwanted stress can in fact become useful, if engineered properly. That is, stacking multiple thin film layers with different amounts of stress can in turn induce out-of-plane bending in the thin film stack in either upward or downward direction. Compared to other approaches for manufacturing out-of-plane structures at microscale such as magnetic field-driven assembly or thick photoresist processing etc., one key benefit of stress-induced bending is that it requires no external stimuli and has relatively simple fabrication [5, 6]. Nevertheless, to effectively utilize this concept in creating 3D shapes on IC chips, it is crucial to first identify IC-compatible thin film materials that also have a large mismatch of intrinsic stress.

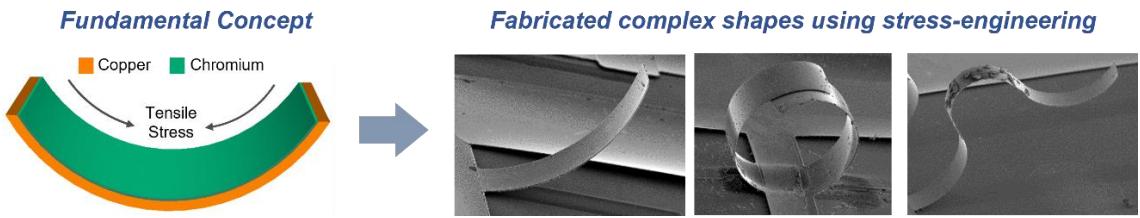

In this work, we have demonstrated the use of patterned thin film stacks made of copper and chromium layers that inherently possess a large residual stress mismatch in creating complex 3D shapes [7], where both materials are fully IC-compatible and quite commonly find use in IC fabrication. Through experiments, we observed that evaporated chromium thin films, by nature, possess a large tensile stress at thicknesses below 50 nm, whereas evaporated copper films have a minimal residual stress for thicknesses up to 1  $\mu\text{m}$ . In the early stages, we utilized this residual stress mismatch to fabricate complex out-of-plane shapes, as elaborated in Fig. 1.1, to illustrate the potential of proposed stress-induced restructuring technique (more details are available in Chapter 2). Later, we applied this technique to develop various types of on-chip passive components with 3D shapes for radio frequency applications. In particular, we have extended our stress-engineering concept to accommodate two types of electronic components used in RFICs i.e., inductors and microelectromechanical switches, while it should be noted that the methodology can be easily adjusted to fit other components as well such as transformers and capacitors etc. We show that the devices manufactured using stress-engineering can significantly outperform their standard 2D-shaped counterparts, primarily because of their 3D shape that extends the overall degree of freedom in the device design process.

Figure 1.1. Concept of residual stress-induced restructuring technique.

As another contribution of this work, we have introduced the use of machine learning (ML) in optimizing MEMS-based RF electronic components (RF-MEMS), such as the ones fabricated in this work using stress-engineering. Despite the dramatic advent of learning algorithms in almost every engineering domain, their use in aiding the design process of RF-MEMS devices has not been given much importance. To bridge this gap, we have put forward a generic methodology to optimize RF-MEMS devices by leveraging ML techniques. More details on the contributions of this work are provided in the following section.

## 1.1. Summary of Contributions

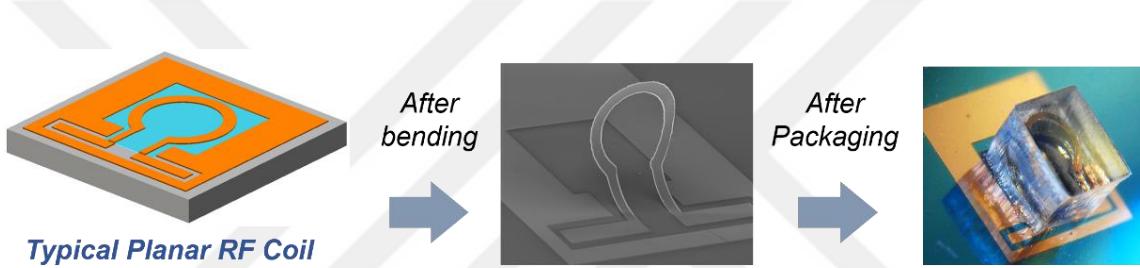

### 1.1.1. Fabrication of High-Performance RF Inductors via Stress-Engineering (Chapter 3)

Planar radio-frequency (RF) on-chip inductors suffer from large electromagnetic losses, stemming from the low resistivity silicon substrate. Though it is well-known that 3-dimensional (3D) MEMS-based RF inductors offer significant performance enhancement by reducing the substrate proximity effects, they are prone to mechanical failures and often come without any appropriate packaging, leading to reliability issues. Herein, we report an approach to fabricate highly robust packaged 3D RF inductors (Fig. 1.2), while relying on the concept of stress-induced self-assembly. By leveraging the large residual stresses in evaporated chromium thin films at low thicknesses (below 50 nm), we assemble the planar copper coils coated with chromium nano-layers into out-of-plane folded RF inductors, directly improving their Q-factor. Through measurements, we show

more than three-fold (~300%) improvement in the inductor Q-factor after the bending. Considering the inherent fragility of suspended inductors, we then add a dedicated wafer-level polymer packaging to our inductors, to improve their mechanical robustness. Specifically, we coat a thick SU-8 layer using a quasi-static volumetric dispensing process, to embed the inductors without deforming them. Upon baking, the polymer layer solidifies, making the buried inductors extremely rigid. We show that though our inductors have Q-factors similar to existing MEMS inductors, their low design complexity and high strength gained via polymer packaging make them stand out among the others. This packaging technique essentially paves the way for the widespread commercialization of suspended inductors, which has been hindered in the past by their poor mechanical reliability.

Figure 1.2. Transforming traditional planar RF coils into out-of-plane wafer-level packaged inductors.

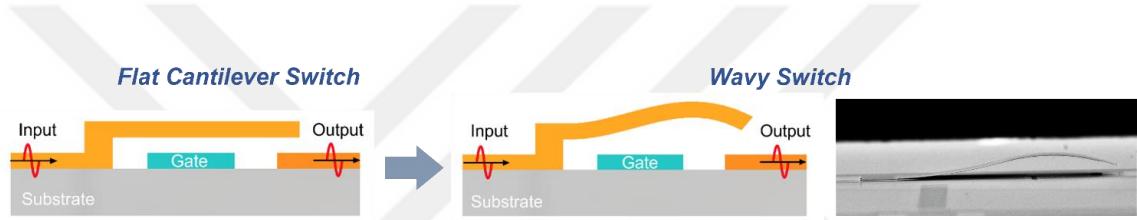

### 1.1.2. Development of High-Performance RF-MEMS Switches via Stress-Engineering (Chapter 4)

Electrostatic microelectromechanical (MEMS) switches are the basic building blocks for various radio-frequency (RF) transceivers. However, conventional cantilever-based designs of MEMS switches require a large actuation voltage, exhibit limited RF performance, and suffer from many performance tradeoffs due to their flat geometries restricted in 2 dimensions (2D). Here, by leveraging the residual stress in thin films, we report a novel development of 3-dimensional (3D) wavy microstructures, which offer the potential to serve as high-performance RF switches. Relying on standard IC-compatible metallic materials, we devise a simple fabrication process to repeatedly manufacture out-of-plane wavy beams with controllable bending profiles and yields reaching 100%. We

then demonstrate the utility of such metallic wavy beams as RF switches achieving both extremely low actuation voltage and improved RF performance owing to their unique geometry, which is tunable in three dimensions and exceeds the capabilities of current state-of-the-art flat cantilever switches with 2D-restricted topology (Fig. 1.3). As such, the wavy cantilever switch presented in this work actuates at voltages as low as 24 V while simultaneously exhibiting RF isolation and insertion loss of 20 dB and 0.75 dB, respectively, for frequencies up to 40 GHz. Wavy switch designs with 3D geometries break through the design limits set by traditional flat cantilevers and provide an additional degree of freedom or control knob in the switch design process, which could enable further optimization of switching networks used in current 5G and upcoming 6G communication scenarios.

Figure 1.3. Schematic illustration of proposed wavy switch and its geometrical differences compared to traditional flat-cantilever switch.

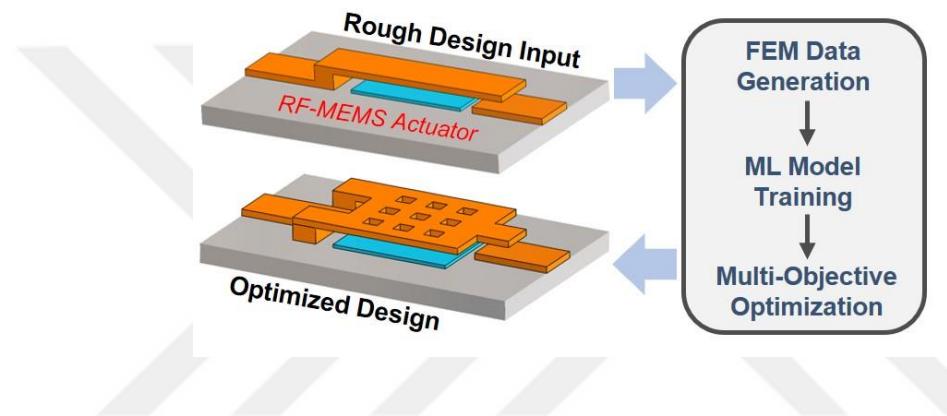

### 1.1.3. Machine Learning-Based Design and Optimization of RF-MEMS Components (Chapter 5)

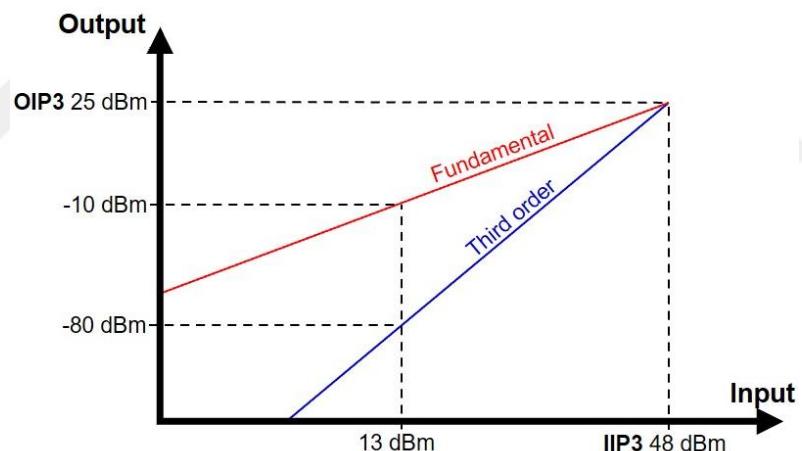

RF-MEMS technology has evolved significantly over the years where various attempts have been made to tailor such devices for extreme performance by leveraging novel designs and fabrication processes as well as integrating unique materials; however, their design optimization aspect has remained less explored. In this work, we report a computationally efficient generic design optimization methodology for RF-MEMS passive devices based on multi-objective heuristic optimization techniques, which to our best knowledge stands out as the first approach offering applicability to different RF-MEMS passives as opposed to being customized for a single, specific component [8] (Fig. 1.4). To comprehensively optimize the design, both electrical and mechanical aspects of RF-MEMS device design are modeled carefully using coupled finite element analysis (FEA). The proposed approach first generates a dataset, efficiently spanning the entire

design space, based on FEA models. By coupling this dataset with machine learning based regression tools, we then generate surrogate models describing the output behavior of RF-MEMS device for a given set of input variables. Finally, the developed surrogate models are subjected to genetic algorithm-based optimizer, to extract the optimized device parameters. The proposed approach is validated for two case studies including RF-MEMS inductors and electrostatic switches, where the multiple design objectives are optimized simultaneously. Moreover, the degree of conflict between various design objectives of the selected devices is studied, and corresponding sets of optimal trade-offs (pareto fronts) are extracted successfully.

Figure 1.4. ML-based design and optimization methodology for RF-MEMS components.

## 2. CONTROLLABLE RESTRUCTURING OF THIN FILMS BASED ON INTRINSIC STRESS<sup>1</sup>

### 2.1. Concept of Intrinsic Stress-Induced Self-Assembly

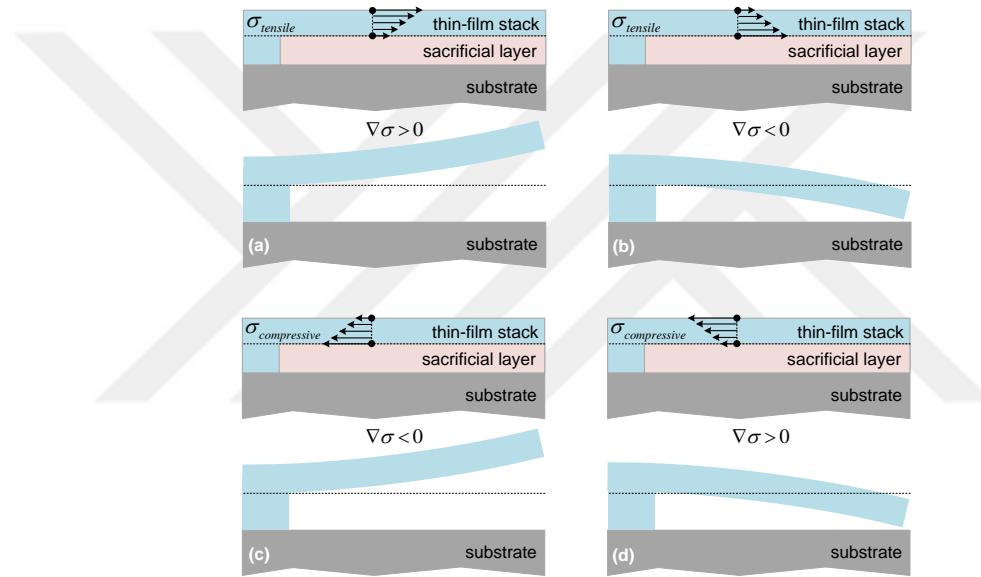

When a layer of thin metal film is deposited on a substrate, tensile or compressive residual stresses are likely to develop in the deposited film which can cause the film to either contract or expand when released from the supporting substrate [9-11]. The type of intrinsic stress in the film, depends largely on the material properties, as well as the deposition technique (i.e. sputtering, evaporation etc.) and the actual deposition conditions (i.e. temperature, pressure, ambient gas etc.). By engineering stress gradients in multi-layer structures such that differing magnitudes and/or modes of residual stress (i.e. tensile or compressive) exist in each layer, effective transverse bending of the entire structure in either upward or downward direction can be achieved (Fig. 2.1). Accordingly, increasing tensile stress gradients from the sacrificial layer to the top surface of the thin-film stack will cause upward bending of the film upon release (Fig. 2.1(a)); and, tensile stress gradients increasing towards the sacrificial layer will result in downward bending (Fig. 2.1(b)). Opposite behaviour is observed for compressive stress gradients, where increasing stress towards the sacrificial layer cause upward bending (Fig. 2.1(c)); and increasing stress away from the sacrificial layer cause downward bending (Fig. 2.1(d)).

Amount of bending in patterned bi-layer films depends on several factors including thickness of the film, substrate type and deposition temperature, to name a few. The

---

<sup>1</sup> Reprinted with permission from “Intrinsic stress-induced bending as a platform technology for controlled self-assembly of high-Q on-chip RF inductors” by R. Bajwa and M. K. Yapici, Journal of Micromechanics and Microengineering, 29, 064002, 2019. Copyright [2019] by IOP Publishing.

Stoney's equation, which governs the amount of stresses on metal films deposited on a substrate with respect to given conditions is given as follows:

$$\sigma = \frac{Et_1^2 K}{6t_2(1-\nu_s)} \quad (2.1)$$

where  $\sigma$  is the amount of stress,  $K$  is the radius of curvature,  $t_1$  and  $t_2$  are the thicknesses of substrate and film,  $E$  is the elastic modulus of the substrate, and  $\nu_s$  is the Poisson's ratio. Following Stoney's approach, there have been other efforts to model stress in thin-films [12-15].

Figure 2.1 Intrinsic stress-induced post-release bending in multi-layer thin film stacks due to tensile and compressive stress gradients.

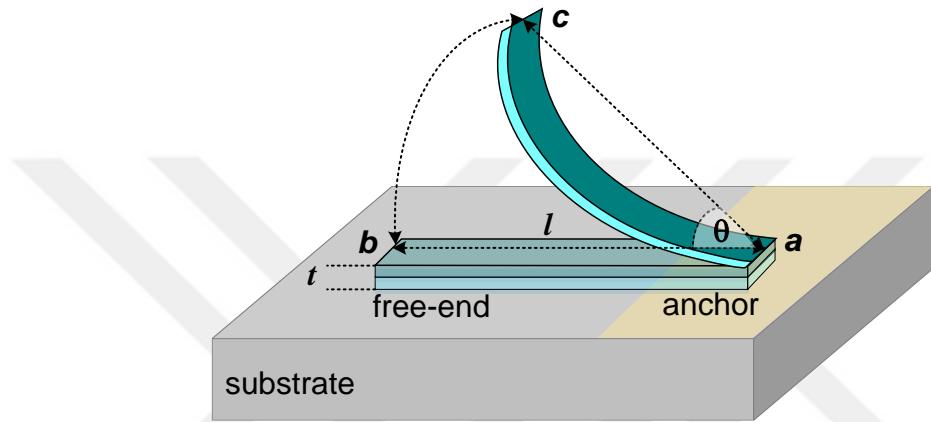

In addition to the magnitude of stress in thin-films, it is also critical to quantify the amount of bending when patterned thin-film structures are released from an underlying layer. For this purpose, optical and/or electron microscopy imaging can be used to readily quantify and compare the degree of bending in microfabricated thin-film structures with varying geometries and/or fabricated using different deposition techniques or conditions. To evaluate bending, in this work, angular displacement was used as a measure of comparison and bending angle  $\theta$  was estimated both from simulation and fabrication results. Considering a fixed-free, thin-film cantilever (Fig. 2.2) anchored at point  $a$  with

its distal end located at position  $b$ , and assuming that intrinsic stresses exist in the thin-film cantilever structure, upon release from the substrate the cantilever tip will traverse to position  $c$ . The displacement covered by the tip of the cantilever can be used as a parameter to evaluate the amount of bending achieved; however, to normalize the variation with respect to cantilever length, “angular displacement” was used and bending angle  $\theta$  was estimated as shown in Fig. 2.2. This approach provided a sound and practical basis to compare transverse bending of different cantilever geometries.

Figure 2.2. Concept of bending angle ( $\theta$ ) based on angular displacement.

## 2.2. Design and Mechanical Modelling

To characterize the bending angle  $\theta$  with respect to geometrical specifications of patterned thin films, various sets of bi-layer cantilever structures with different dimensions were designed containing copper (Cu) and chromium (Cr) as stacked metal layers. Evaporated chromium thin films have been reported to possess large tensile stress values of around 1.3 GPa at a thickness of 100nm; whereas, copper films possess smaller tensile stress, usually less than 0.1 GPa, over a large span of thicknesses [15]. Since the actual magnitude of intrinsic stress in metallic thin-films is highly dependent on the film thickness and deposition conditions, by fixing the deposition parameters and varying the thicknesses of Cr and Cu, it is possible to control the stress gradients along the thickness of a metallic multi-layer stack to control their bending. As such, cantilevers made up of

stacked layers of Cu/Cr are expected to show upward bending, while reverse stress gradients in Cr/Cu cantilevers are expected to cause downward bending.

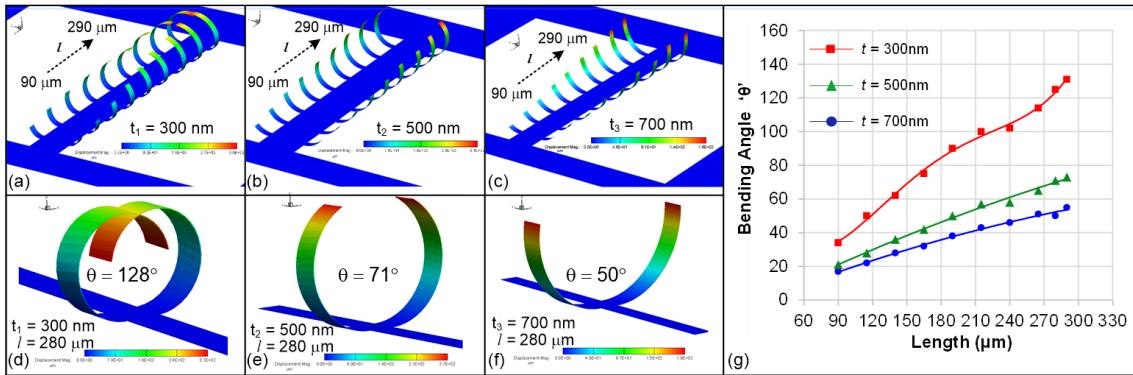

Cantilevers assuming different lengths ranging from 90  $\mu\text{m}$  to 290  $\mu\text{m}$  at three different values for the total bi-layer thickness (300 nm, 500 nm and 700 nm) were designed and modelled in CoventorWare®. To create model geometries of desired cantilever structures, a fabrication process flow was first designed in the process editor of CoventorWare®. The Process Editor of CoventorWare® software makes use of foundry MEMS processes (e.g. CVD, metal evaporation and deep etching etc.) to create process flows and hence perform more accurate MEMS simulations. Subsequently, suitable mask layouts defining length and width of the cantilevers were developed and eventually, integrating mask layouts with appropriate fabrication process flow resulted in 3D model geometries of cantilevers. The thickness of the Cr layer was fixed at 100 nm, and Cu layer was varied at 200 nm, 400 nm and 600 nm; respectively. Following the construction of the model geometry, reference values for intrinsic stresses [15] were defined in material library for both copper and chromium metals as a parameter of their material properties. However, other material properties such as elastic constants and density. were kept at pre-defined default values. Progressively, boundary conditions i.e., anchor points for cantilevers etc. were defined and automatic meshing was performed. Finally, the mechanical solver of CoventorWare® software *MemMech* was used to simulate the designs and observe mechanical deformation in the cantilever structures. Finite element analysis (FEA) results revealed out-of-plane bending of cantilever structures away from the substrate with the bending angle ( $\theta$ ) as a function of cantilever thickness ( $t$ ) and cantilever length ( $l$ ). Since cantilever width ( $w$ ) does not significantly affect bending in the low width/length ( $w/l$ ) regime of less than 1 [9],  $w$  was fixed at 50  $\mu\text{m}$  to yield  $w/l$  ratios of  $\sim 0.5$  or less, and achieve bending primarily as a function of  $l$  and  $t$ .

Analysis results display an increase in the bending angles with increasing cantilever length, while bending angles decreased with increasing cantilever thicknesses (from 300 nm to 700 nm), as reported in Fig. 2.3(a-c). To highlight the effect of film thickness, a 280- $\mu\text{m}$ -long cantilever was simulated for various thicknesses and results indicated decreasing bending angles of 128°, 71° and 50° with increasing film thicknesses of 300 nm, 500 nm and 700 nm, respectively (Fig. 2.3(d-f)). The complete trend of bending

angles for all simulated cantilever lengths and thicknesses are plotted and compared in Fig. 2.3(g).

Figure 2.3. FEA results indicating intrinsic stress induced bending for a set of cantilevers with lengths “ $l$ ” varying from  $90 \mu\text{m}$  to  $290 \mu\text{m}$  and thickness of: (a)  $t_1 = 300 \text{ nm}$ ; (b)  $t_2 = 500 \text{ nm}$ ; and (c)  $t_3 = 700 \text{ nm}$ ; (d-g) zoom-in views of  $280 \mu\text{m}$ -long, two-sided cantilevers for the same thicknesses  $t_1$ ,  $t_2$ ,  $t_3$ , respectively; and (g) trend of simulated bending angles ( $\theta$ ) with respect to the length of cantilevers for varying thicknesses.

### 2.3. Fabrication and Characterization

To verify the bending results obtained from mechanical modelling, identical structures were developed using standard MEMS fabrication processes. First, a sacrificial layer of silicon dioxide ( $\text{SiO}_2$ ) was deposited on a silicon substrate using plasma enhanced chemical vapor deposition (PECVD). The sacrificial oxide was lithographically patterned by spin-coating and exposing a layer of AZ 5214E photoresist, and wet etching the oxide with buffered oxide etchant (BOE). As a result, contact holes in the  $\text{SiO}_2$  layer were created, through which cantilever structural layers were anchored to silicon and mechanical connection was ensured. To realize multi-layer metallic films, chromium and copper of varying thicknesses were deposited on  $\text{SiO}_2$  using e-beam evaporation technique with substrate rotation. First, a thin layer (10 nm) of chromium was deposited to serve as an adhesion layer, followed by deposition of a copper layer, and finally by a top chromium layer. The stacked thin-film metallic layers were patterned by

photolithography to form cantilever structures, and selectively wet-etched with commercial Cr and Cu etchants. Etching of the sacrificial oxide layer resulted in free standing cantilevers with some finite amount of intrinsic stress.

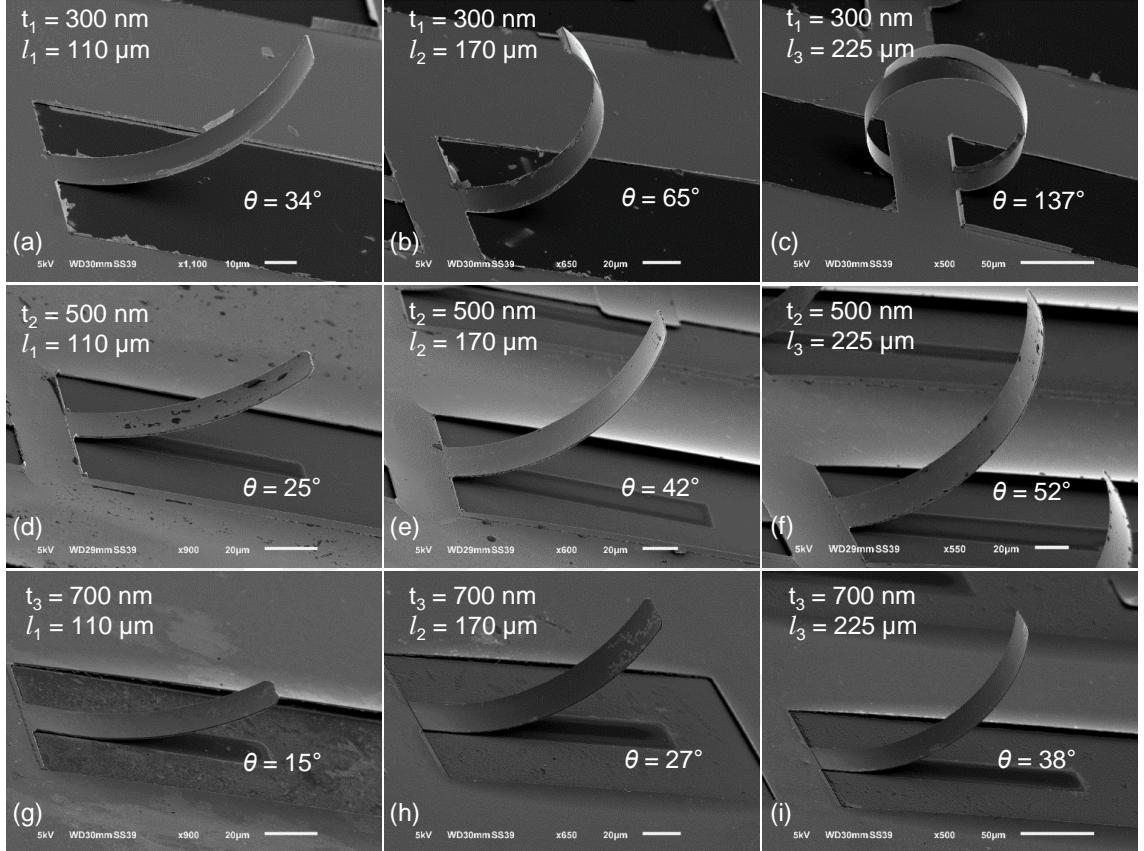

Figure 2.4. Side-view SEM images of released cantilevers with corresponding bending angles ( $\theta$ ) for three different lengths ( $l_1 = 110 \mu\text{m}$ ,  $l_2 = 170 \mu\text{m}$ ,  $l_3 = 225 \mu\text{m}$ ) and thicknesses  $t_1 = 300 \text{ nm}$  (a-c);  $t_2 = 500 \text{ nm}$  (d-f);  $t_3 = 700 \text{ nm}$  (g-i).

Thin-films of chromium have large intrinsic stress and act as the primary stressor layer in the bi-metallic cantilever structure. Additionally, the magnitude of stress in Cr is highly dependent on film thickness. Therefore, to ensure the same magnitude of stress in Cr layers for all fabricated designs, the thickness of Cr was kept constant at 100 nm. Instead, thickness of the Cu layer whose stress is relatively invariant of film thickness was adjusted at 3 different values (200 nm, 400 nm and 600 nm) to achieve of Cr/Cu thickness ratios ( $t_{\text{Cr}}/t_{\text{Cu}}$ ) of 1/2, 1/4, and 1/6, respectively. This approach allowed a more controllable modulation of the total stress gradient in the multi-layer stack and provided tuning of the

degree of bending in fabricated microstructures upon sacrificial layer release. Following fabrication, stress-induced bending in cantilevers was observed under a scanning electron microscope (SEM) and bending angles were experimentally quantified. SEM images of cantilevers for three fixed lengths ( $l$ ) and for three film thicknesses ( $t$ ) are shown in figure 6, which indicate upward bending where  $\theta$  decreases with  $t$ , and increases with  $l$  in much similarity to modelling results. Specifically,  $\theta$  rises from  $34^\circ$  to a maximum of  $137^\circ$  as  $l$  increases from  $110\ \mu\text{m}$  to  $225\ \mu\text{m}$  for  $t_1$  of  $300\ \text{nm}$  (Fig. 2.4(a-c)), similarly for  $t_2$  of  $500\ \text{nm}$   $\theta$  varies from  $25^\circ$  to  $52^\circ$  (Fig. 2.4(d-f)), and from  $15^\circ$  to a minimum of  $38^\circ$  at  $t_3$  of  $700\ \text{nm}$  and  $l$  of  $225\ \mu\text{m}$  (Fig. 2.4(g-i)).

Figure 2.5. (a) SEM images of two-sided Cu/Cr cantilever arrays consisting of varying cantilever lengths and fabricated at three different film thicknesses; (b) SEM images of  $280\ \mu\text{m}$  long cantilevers fabricated at thicknesses of  $700\ \text{nm}$ ,  $500\ \text{nm}$  and  $300\ \text{nm}$ ; and (c) comparison of bending data obtained from simulations and fabrication results for cantilevers.

In coherence with the modelling results,  $300\text{-nm-thick}$  structures exhibit the highest, whereas  $700\text{-nm-thick}$  structures show the lowest bending for all cantilever designs (Fig. 2.5(a-c)). The comparison between simulated and experimental results shows high consistency especially at lower values of length ( $l$ ); however, at larger lengths the bending angles of fabricated structures tend to increase more rapidly than simulated bending angles. For instance, bending angles for a cantilever of length  $280\ \mu\text{m}$  at film thicknesses of  $300\ \text{nm}$ ,  $500\ \text{nm}$  and  $700\ \text{nm}$  were observed to be  $155^\circ$ ,  $115^\circ$ , and  $64^\circ$ , respectively (Fig. 2.5(d-f)); whereas modelled cantilevers with similar  $l$  of  $300\ \mu\text{m}$  displayed  $\theta$  of  $131^\circ$ ,

77°, and 59°, respectively. Complete bending data from both simulation and fabrication results are plotted and compared in Fig. 2.5(g).

As suggested by the theory, direction of cantilever bending can be adjusted by controlling the sign of the stress gradient or the loading mode. Since stress in evaporated thin-film metals is usually tensile; we have chosen to control the sign of the stress gradient (i.e., considering increase of tensile stress away from the sacrificial layer-thin film interface to yield positive stress gradients and increasing tensile stress gradients towards the sacrificial layer to be negative) rather than the loading mode (tensile vs. compressive). Thus, it can be hypothesized that by modulating the stress gradient along the length of a cantilever, it can be possible to realize complex wavy structures upon post-release self-assembly which are otherwise difficult, if not impossible, to fabricate with conventional microfabrication.

Figure 2.6. Fabrication process flow of a three-segment cantilever showing opposing stress gradients engineered in each segment for realization of wavy structure.

To elaborate on the concept, cantilevers with sections of alternating stress conditions were designed and fabricated. A fabrication process flow diagram for such a cantilever with three segments is shown in Fig. 2.6. Initially, a sacrificial layer of  $\text{SiO}_2$

layer was deposited on a silicon substrate using PECVD technique and patterned using standard photolithography step followed by a subsequent wet etching step to create sub-micron deep via holes (Fig. 2.6(a)). Next, a bi-layer thin film metal stack consisting of a chromium metal layer on top of a copper metal layer was deposited and patterned using a combination of e-beam metal evaporation, photolithography and selective wet etching. The patterned metal-1 layer (Cu/Cr) formed the first and last sections of the three-segment cantilever (Fig. 2.6(b)). Afterwards, a second  $\text{SiO}_2$  sacrificial layer was deposited and patterned on top of metal-1 layer to create mechanical junctions (vias) between metal-1 and a subsequent metal-2 layer (Fig. 2.6(c)). Lastly, metal-2 layer stack (Cr/Cu) was deposited and patterned with the intention to serve as the middle section of the three-segment cantilever (Fig. 2.6(d)). First and last sections of the cantilever (metal-1 layer) are comprised of Cu/Cr metal stack resulting in upward bending, whereas the middle section is made up of Cr/Cu stack (metal-2 layer) and have opposite stress gradients causing this section to bend downwards. Sacrificial release of such a cantilever results in controllable fabrication of wavy shaped structure (Fig. 2.6(f)) which also demonstrates the potential of intrinsic-stress induced self-assembly technology in 3D microfabrication. Fig. 2.7 shows a scanning electron microscope image of a three-segment, wavy structure fabricated using the described process flow.

Figure 2.7. SEM images of a segmented cantilever showing opposing stress gradients engineered in each segment to controllably realize upward and downward deflections and form a complex wavy-shaped structure.

### 3. ORIGAMI-INSPIRED FABRICATION OF HIGH-PERFORMANCE WAFER-LEVEL PACKAGED THREE-DIMENSIONAL RADIO- FREQUENCY INDUCTORS<sup>2</sup>

#### 3.1. Introduction

On-chip inductors are among the key elements of various radio-frequency (RF) transceiver blocks such as low-noise amplifiers, matching networks, voltage-controlled oscillators and filters, and their efficiency directly affects the overall performance of an RF system [16]. Conventional on-chip inductors have planar spiral-shaped geometries, which are easy to design and fabricate; however, such geometries are linked with large RF losses, most of which originate due to strong magnetic coupling between flat spiral inductor coils and underlying silicon substrate with finite resistivity. To quantify inductor losses, a unitless metric known as “*Q*-factor” is often utilized, which is an indicator of the inductor efficiency, where larger *Q*-factor implies a more efficient inductor.

Fundamentally, improvement in *Q*-factor or reduction in losses can be achieved by decreasing the proximity of inductors from lossy silicon substrate, which is practically impossible with flat spiral designs as they are mechanically adhered to substrate. Considering these performance limitations, various efforts have been made to realize more advanced 3-dimensional (3D) inductor geometries, also referred to as MEMS inductors, with better immunity against the substrate effects [16, 17]. This was achieved by either lifting the coils away from the substrate, removing the bulk silicon from

---

<sup>2</sup> Reprinted with permission from “Origami-Inspired Fabrication of High-Performance Wafer-Level Packaged Three-Dimensional Radio-Frequency Inductors” by R. Bajwa and M. K. Yapici, IEEE Journal of Microelectromechanical Systems, 2023. Copyright [2023] by IEEE.

underneath the inductors, or designing complex 3-dimensional structures with low magnetic leakage into the substrate [2, 4, 7, 18-21].

With 3D designs, on-chip inductors have demonstrated  $Q$ -factors much larger than the conventional planar spiral designs [2, 4, 7, 18-21]. However, compared to planar designs, out-of-plane topologies are inherently linked with high fabrication complexity, more susceptible to mechanical stresses, and require robust packaging solutions to ensure sufficient device reliability [22]. Though there have been attempts where researchers focused on lowering the manufacturing complexity [23], adding wafer-level cap to inductors [24] or strengthening them mechanically with improved designs [25], all these aspects that are essential for overall device development were scarcely addressed simultaneously. In particular, wafer-level packaging of 3D inductors has been widely overlooked over the years, which is in fact critical for realizing resilient integrated out-of-plane inductors capable of withstanding subsequent die packaging and other assembly procedures. Bare 3D on-chip inductors are by nature incompatible with the die packaging process, due to their suspended shape resulting in high fragility [26, 27]. Therefore, from a practical standpoint, a 3D inductor with performance no matter how much larger than its flat-spiral counterpart, is meaningless without the sufficient mechanical stability and appropriate packaging.

Addressing the above concerns, we here report the development of self-assembled out-of-plane RF inductors with wafer-level polymer encapsulation. Our inductors not only exhibit large  $Q$ -factors but also have low design and fabrication complexity as well as extremely high mechanical robustness gained via polymer packaging, compared to other free-standing inductors. To fabricate 3D inductors, we have leveraged the concept of intrinsic/residual stress in thin films, where we carefully adjust the stress mismatch between the layers of patterned thin film stack to induce controllable out-of-plane bending [7]. As opposed to other fabrication methodologies for MEMS inductors such as substrate transfer, post-fabrication magnetic assembly, and thick photoresist-based processes that are lengthy and complex, stress-induced self-folding is relatively simple involving only one typical 3-step surface micromachining process. We show that by bending the inductors away from the substrate, their  $Q$ -factor exhibits a three-fold improvement compared to similar geometries in flat 2D configuration.

Furthermore, thin film suspended inductors have thickness of less than a micron, while their designed footprints can be as large as  $1 \text{ mm}^2$  or even more depending on the amount of required inductance. Such large-aspect ratio suspended devices are thus naturally very fragile [28], and their packaging is certainly not straightforward. In view of these challenges, we have developed a quasi-static polymer encapsulation process for 3D bent-up inductors, to realize their on-wafer packaging without mechanically damaging them. Instead of standard spin-coating, we use volumetric dispensing at a low flow rate to quasi-statically immerse the inductors in a commercially available polymer (SU-8) while preserving their shape. Thick films can also be achieved easily using this method by simply controlling the dispensed volume, which is required for encapsulating tall bent-up inductors, while producing thick films is challenging with spin-coating. Upon baking, the dispensed polymer film solidifies with suspended inductors buried inside it, thereby providing a solid mechanical support. Afterwards, we also pattern the SU-8 layer to remove the unwanted polymer material and realize a localized on-wafer packaging for inductors.

It should be noted that SU-8 encapsulation slightly degrades the performance of bent-up inductors due to its large loss tangent value compared to air, however the amount of degradation is quite low. To summarize, we herein highlight a great potential of suspended inductors that has not been fully utilized in past due to their limited reliability. In response, we then propose a multi-faceted development strategy for high-performance out-of-plane RF inductors, in which we address various unanswered practical issues.

### **3.2. Design Concept**

Inherently, thin films deposited on a substrate have residual stresses inside them, which depend on many factors including deposition type, film material, film thickness and deposition conditions etc. A mismatch between the residual stress values of different layers in a multi-layer thin film stack generates a stress gradient along the film thickness. By adjusting the direction and amount of this stress gradient, a controllable out-of-plane bending can be induced in thin films, as they are released from the substrate [7, 15].

Relying on this idea, we have identified two standard IC thin film materials with large residual stress mismatch i.e., copper and chromium (Fig. 3.1(a)), to fabricate bent-up inductors with large bending angles, which helps reduce the substrate proximity losses.

Evaporated copper thin films are known to have low stress while chromium thin films possess a significantly high intrinsic stress, particularly at low thicknesses [15, 29]. We have verified this behavior by characterizing the film stress with respect to thickness, through surface profilometry experiments and utilizing Stoney's equation. We observed that residual stress of copper (Cu) stays between 60-80 MPa (tensile) for thicknesses up to 1  $\mu$ m. In contrast, stress in chromium thin films is more than 1 GPa at thicknesses below 40 nm, reaching a maximum of 2.7 GPa (tensile) at 20 nm (Fig. 3.1(b)). It is worthwhile to note that both copper and chromium are highly IC-compatible and are widely used as IC interconnects and adhesion layers for metallic films, respectively. Using these materials thus simplifies the fabrication by alleviating any additional costs linked with some special materials, which are often required for fabricating 3D inductors.

Figure 3.1. Schematic demonstration of the development of stress-induced self-assembled ring inductors: (a) illustration of bending in copper-chromium thin film stacks; (b) characterized residual stress in evaporated chromium thin film for thickness up to 40 nm. As a convention, tensile stress is represented with positive values; (c) fabrication

process for self-assembled inductors; (d) simulation results and SEM images of the designed ring inductors, with ring radius varying from 200-400  $\mu\text{m}$ . Scale bar = 300  $\mu\text{m}$ .

### 3.3. Modeling and Fabrication of Self-folded Inductors