**REPUBLIC OF TURKEY

GAZİANTEP UNIVERSITY

GRADUATE SCHOOL OF NATURAL & APPLIED SCIENCES**

**DEVELOPMENT OF EMBEDDED SYSTEM FOR ENERGY

ANALYZER**

**M.Sc. THESIS

IN

ELECTRICAL AND ELECTRONICS ENGINEERING**

**BY

UĞUR POLAT

FEBRUARY 2022**

**FEBRUARY 2022**

**M.Sc. in Electrical and Electronics Engineering**

**UĞUR POLAT**

# **DEVELOPMENT OF EMBEDDED SYSTEM FOR ENERGY ANALYZER**

**M.Sc. Thesis

in

Electrical and Electronics Engineering

Gaziantep University**

**Supervisor**

**Assist. Prof. Dr. Nurdal WATSUJİ**

**by

Uğur POLAT

February 2022**

©2022[Uğur POLAT]

## DEVELOPMENT OF EMBEDDED SYSTEM FOR ENERGY ANALYZER

submitted by **Uğur POLAT** in partial fulfillment of the requirements for the degree of Master of Science in **Electrical and Electronics Engineering**, **Gaziantep University** is approved by,

Prof. Dr. Mehmet İshak YÜCE

Director of the Graduate School of Natural and Applied Sciences.....

Prof. Dr. Ergün ERÇELEBİ

Head of the Department of Electrical and Electronics Engineering.....

Assist. Prof. Dr. Nurdal WATSUJİ

Supervisor, Electrical and Electronics Engineering

Gaziantep University .....

Graduation Date: 03 February 2022

### Examining Committee Members:

Assist. Prof. Dr. Nurdal WATSUJİ

Thesis Supervisor, Electrical and Electronics Engineering

Gaziantep University .....

Prof. Dr. Arif NACAROĞLU

Electrical and Electronics Engineering

Gaziantep University .....

Assist. Prof. Dr. Noor Bahar ALDİN

Electrical and Electronics Engineering

Hasan Kalyoncu University .....

**I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.**

**Uğur POLAT**

## ABSTRACT

### DEVELOPMENT OF EMBEDDED SYSTEM FOR ENERGY ANALYZER

**POLAT, Uğur**

**MSc. in Electrical and Electronics Engineering**

**Supervisor: Assist. Prof. Dr. Nurdal WATSUJİ**

**February, 2022**

**146 pages**

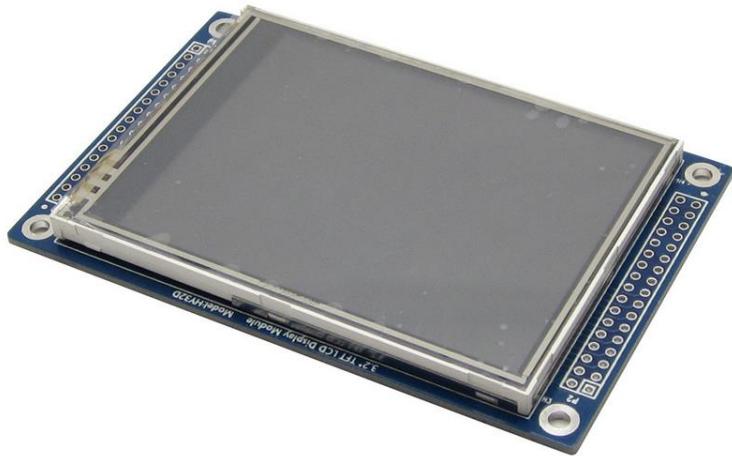

The increase in energy consumption and the gradual decrease in limited energy resources raise fundamental questions such as how much energy is produced, what is its efficiency, how it distributes to the end users. Not only on an individual basis, but also on a global basis research and development are carried out on this subject. Also, required equipment usage in energy generation, distribution and utilization is increasing every day, too. In the common systems for monitoring, need to install individual measuring devices e.g., Voltmeter, Oscilloscope, etc. separately because of the harmonic currents and voltages in the grids. Our design yields an industrial analyzer that sense the current and voltage at the input then designed circuit transmits signals proportional levels to the MCU which will be analyzed based on some standards such as IEEE Std 1459TM-2010 [1]. An A/D converter, converts the voltage and current signals to the digital representation at regular intervals. MCU periodically samples ( $f_{sampling}=1600$  Hz,  $N=32$ , A/D resolution 12-bit) then analyze the voltage and current signals at regular intervals of time with the \*0,4 % error rate. Then, it stores the data of electrical variables which are analyzed. e.g., frequency, true RMS volts, true RMS amps,  $\cos(\phi)$  and even harmonic values, including energy variables. For the project ARM based STM-32F405 and LCD-TFT screen which part number is HY-32D are one of the most important components. The features of this device completely provide our requirements with isolation circuits, fuses and another safety equipment. As a summary, it is the goal of the thesis to develop a compact analyzer device that analyzes the variable parameters in a grid by eliminating the require of multiple measuring devices. Thanks to the LCD, with the compact design we are able to see all data only on a screen and it's completely mobilized.

\*The error rate depends on the  $f_{sampling}$ ,  $N$ , and A/D resolution.

**Key Words:** Embedded Systems, Arm Cortex, Energy Analyzer, Single Phase Analyzer, STM-32f429, Digital Signal Processing, Real-time Operating System.

## ÖZET

# GÖMÜLÜ SİSTEM KULLANARAK BİR ENERJİ ANALİZÖRÜ GELİŞTİRİLMESİ

**POLAT, Uğur**

**Yüksek Lisans Tezi, Elektrik Elektronik Mühendisliği**

**Danışman: Dr. Öğrt. Üyesi Nurdal WATSUJİ**

**Şubat, 2022**

**146 sayfa**

Enerji tüketiminin artması ve sınırlı enerji kaynaklarının giderek azalması; ne kadar enerji üretildiğinin, verimliliğin, son kullanıcılara nasıl dağıtıldığının sorularını gündeme getiriyor. Bu konuda sadece bireysel bazda değil, global bazda da araştırma ve geliştirmeler mevcuttur. Ayrıca enerji üretimi, dağıtıımı ve kullanımında gerekli ekipman kullanımı da her geçen gün artmaktadır. Güç sistemlerinde şebekedeki dengesiz harmonik akımlar ve gerilimleri gözlemek için; Voltmetre, Ampermetre, Osiloskop Wattmetre vb. ayrı ayrı ölçüm cihazlarının kurulumu gereklidir. Yapmış olduğumuz çalışmamızda, şebekeden gelen akımı ve voltajı algılayan özel bir devre MCU'ya orantılı seviyelerde sinyaller iletir. IEEE Std 1459TM-2010 [1] gibi bazı standartlara göre analizler yapılır. Bir A/D dönüştürücü, voltaj ve akım sinyallerini düzenli aralıklarla ayrı zamanlı sinyale dönüştürür. MCU periyodik olarak örnekler ( $f_{sampling}=1600$  Hz,  $N=32$ , A/D çözünürlüğü 12-bit) daha sonra voltaj ve akım sinyallerini düzenli aralıklarla yaklaşık \*0,4 % hata orANIyla analiz eder. Analiz edilen frekans, RMS voltları, RMS amperleri,  $\cos(\phi)$ , harmonikler ve enerji değerleri ölçülür. Projede STM-32F405 MCU ve HY-32D LCD-TFT ekran en önemli bileşenlerden biridir. PCB'mız için izolasyon devreleri, sigortalar ve diğer güvenlik ekipmanları ile gereksinimlerimizi tamamen karşılamaktadır. Özet olarak, birden fazla ölçüm cihazı gereksinimini ortadan kaldırın bir şebekedeki değişken parametreleri analiz eden tek bir analizör geliştirmek tezin amacıdır. LCD sayesinde tüm verileri sadece bir ekran da gösterecek mobilize ve kompakt yapıda olacaktır.

\*Hata oranı  $f_{örnekleme}$ ,  $N$  ve A/D çözünürlüğüne bağlıdır.

**Anahtar Kelimeler:** Gömülü Sistem, Arm Cortex, Enerji Analizörü, Tek Fazlı Analizör, STM-32f429, Sayısal Sinyal İşleme, Gerçek Zamanlı İşletim Sistemi

*“Dedicated to my darling wife Kübra, daughter Eslem

Âmine and science of electronics...”*

## **ACKNOWLEDGEMENTS**

I would like to thanks my supervisor, Assist. Prof. Dr. Nurdal WATSUJİ and my motivator Mr. F. Gökçegöz and Mr. U. Şentürk for their guidance and support throughout the study. I am thankful for their encouragement and motivation.

I would like to express my gratitude and gratitude to my teachers who have supported me throughout my studies, to my darling wife, my family and friends who have always been there for me.

## TABLE OF CONTENTS

|                                                                  | Page  |

|------------------------------------------------------------------|-------|

| <b>ABSTRACT</b>                                                  | V     |

| <b>ÖZET</b>                                                      | VI    |

| <b>ACKNOWLEDGEMENTS</b>                                          | VIII  |

| <b>TABLE OF CONTENTS</b>                                         | IX    |

| <b>LIST OF TABLES</b>                                            | XII   |

| <b>LIST OF FIGURES</b>                                           | XIII  |

| <b>LIST OF SYMBOLS</b>                                           | XVIII |

| <b>LIST OF ABBREVIATIONS</b>                                     | XIX   |

| <b>CHAPTER I: INTRODUCTION</b>                                   | 1     |

| 1.1.    Literature Summary .....                                 | 1     |

| 1.1.1    Effective Value in AC Systems.....                      | 2     |

| 1.1.2    Phase Difference Between AC Voltage and AC Current..... | 4     |

| 1.1.3    Power Calculation in AC Systems .....                   | 5     |

| 1.1.4    Power Factor ( $\cos \phi$ ) in Power Systems.....      | 7     |

| 1.1.5    Harmonic Distortion.....                                | 9     |

| 1.2    Purpose of the Thesis.....                                | 13    |

| 1.3    Conclusion and Key Findings.....                          | 14    |

| <b>CHAPTER II: PHASE LOCKED LOOP (PLL) DESIGN</b>                | 16    |

| 2.1    Phase Locked Loop.....                                    | 16    |

| 2.2    Phase Locked Loop (PLL) Methods.....                      | 19    |

| 2.2.1    Notch Filtered Single Phase PLL .....                   | 19    |

| 2.2.2    Orthogonal Signal Generator .....                       | 26    |

| 2.3    Discretizing the Phase Locked Loop Model.....             | 35    |

|                                                                  |                                                                         |           |

|------------------------------------------------------------------|-------------------------------------------------------------------------|-----------|

| 2.3.1                                                            | Separation of the Second Order Low Pass Filter .....                    | 36        |

| 2.3.2                                                            | Discretization of the PI Controller .....                               | 39        |

| 2.3.3                                                            | Discrete Time Model of Classical PLL Structure .....                    | 43        |

| 2.3.4                                                            | Software Implementation of the Digital PLL Model with PSIM.....         | 45        |

| 2.4                                                              | Hardware Implementation of Software PLL .....                           | 47        |

| <b>CHAPTER III: HARDWARE DESIGN FOR INDUSTRIAL ANALYZER.....</b> |                                                                         | <b>50</b> |

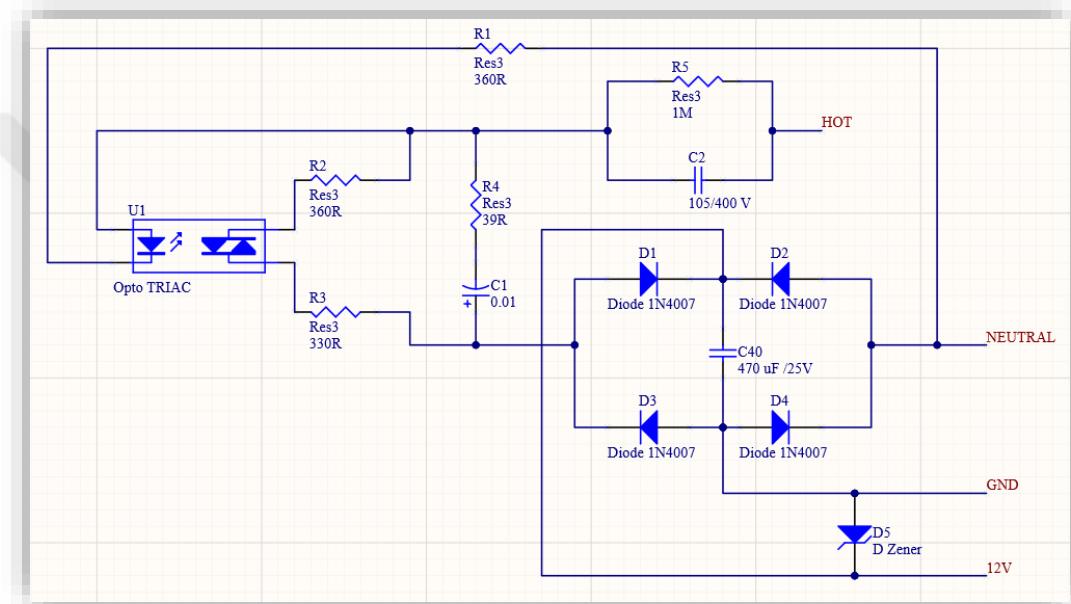

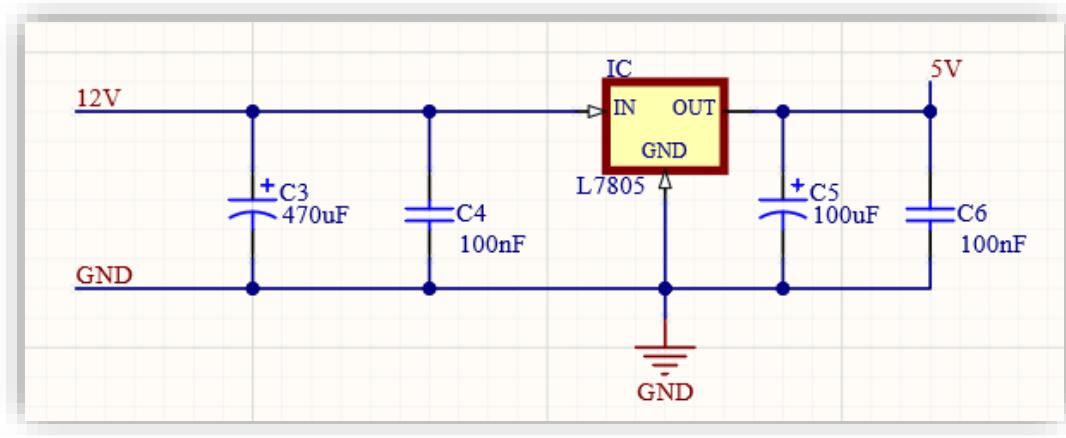

| 3.1                                                              | Main Supply Circuit .....                                               | 50        |

| 3.2                                                              | Voltage Detection Circuit .....                                         | 51        |

| 3.3                                                              | Current Detection Circuit .....                                         | 53        |

| 3.4                                                              | Voltage and Current Zero-cross Detection Circuit.....                   | 55        |

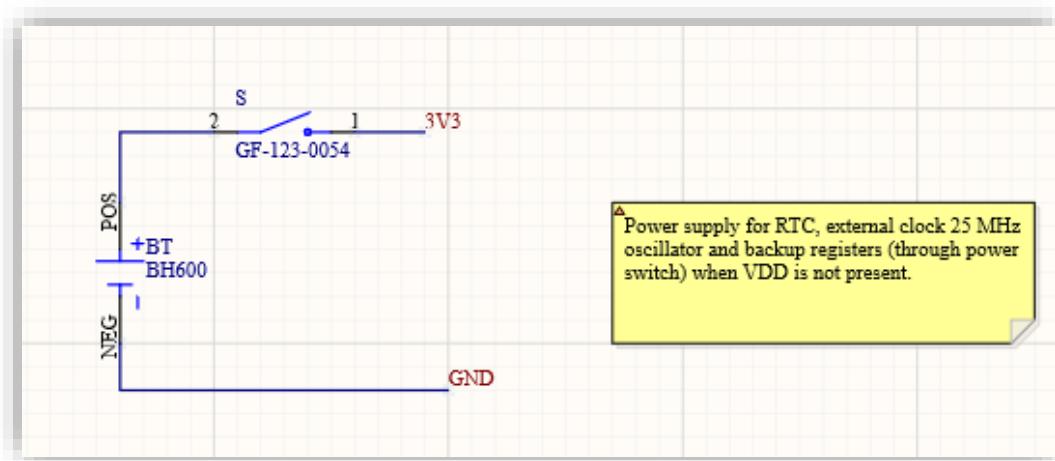

| 3.5                                                              | Battery Back-up Circuit.....                                            | 56        |

| 3.6                                                              | Microcontroller Unit (MCU) .....                                        | 57        |

| 3.7                                                              | Human Hardware Interface Design .....                                   | 62        |

| 3.8                                                              | Communication Hardware .....                                            | 66        |

| 3.9                                                              | Designed PCB.....                                                       | 68        |

| <b>CHAPTER IV: SOFTWARE DESIGN FOR INDUSTRIAL ANALYZER .....</b> |                                                                         | <b>70</b> |

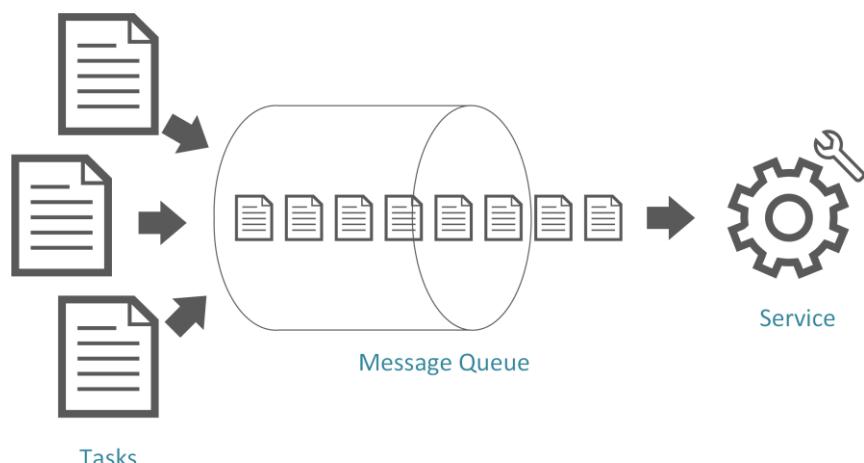

| 4.1                                                              | Message Queue Based Operating System .....                              | 70        |

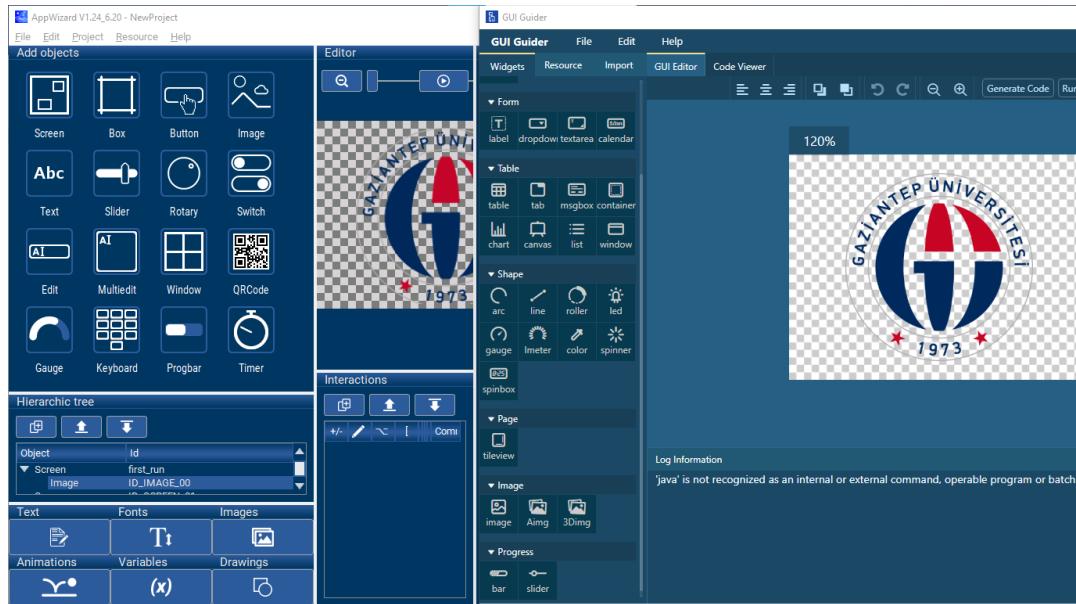

| 4.2                                                              | TFT-LCD Graphical Library .....                                         | 73        |

| 4.3                                                              | Effective Value Calculation of Voltage and Current in Discrete Time ... | 75        |

| 4.4                                                              | Harmonics and Fast Fourier Transform (FFT) Analysis .....               | 79        |

| 4.5                                                              | The Calculation of Phase Angle [ $\cos(\varphi)$ ].....                 | 82        |

| 4.6                                                              | The Calculation of Power Factor (PF).....                               | 85        |

| 4.7                                                              | Power and Energy Calculation .....                                      | 88        |

| <b>CHAPTER V: HARDWARE REALIZATION AND MEASUREMENT</b>           |                                                                         |           |

| <b>RESULTS .....</b>                                             |                                                                         | <b>91</b> |

| 5.1                                                              | Working Screens.....                                                    | 91        |

| 5.2                                                              | The Effect of Sampling Frequency on the Measurements.....               | 98        |

|                                                                              |                                                                      |            |

|------------------------------------------------------------------------------|----------------------------------------------------------------------|------------|

| 5.3                                                                          | The Effect of Analog Digital Converter Resolution on Measurements... | 98         |

| 5.4                                                                          | The Effect of Total Number of Samples on Measurements .....          | 100        |

| 5.5                                                                          | Other Factors That Effective on The Results.....                     | 101        |

| <b>CHAPTER VI: MODBUS COMMUNICATION.....</b>                                 |                                                                      | <b>103</b> |

| 6.1                                                                          | Modbus Communication .....                                           | 103        |

| <b>CHAPTER VII: CONCLUSION AND FUTURE WORKS .....</b>                        |                                                                      | <b>106</b> |

| <b>REFERENCES .....</b>                                                      |                                                                      | <b>108</b> |

| <b>APPENDIX .....</b>                                                        |                                                                      | <b>111</b> |

| Appendix A: Simulating the PLL for Varying Conditions for Notch Filter ..... |                                                                      | 111        |

| Appendix B: Simulating the PLL for Varying Conditions for OSG Filter .....   |                                                                      | 114        |

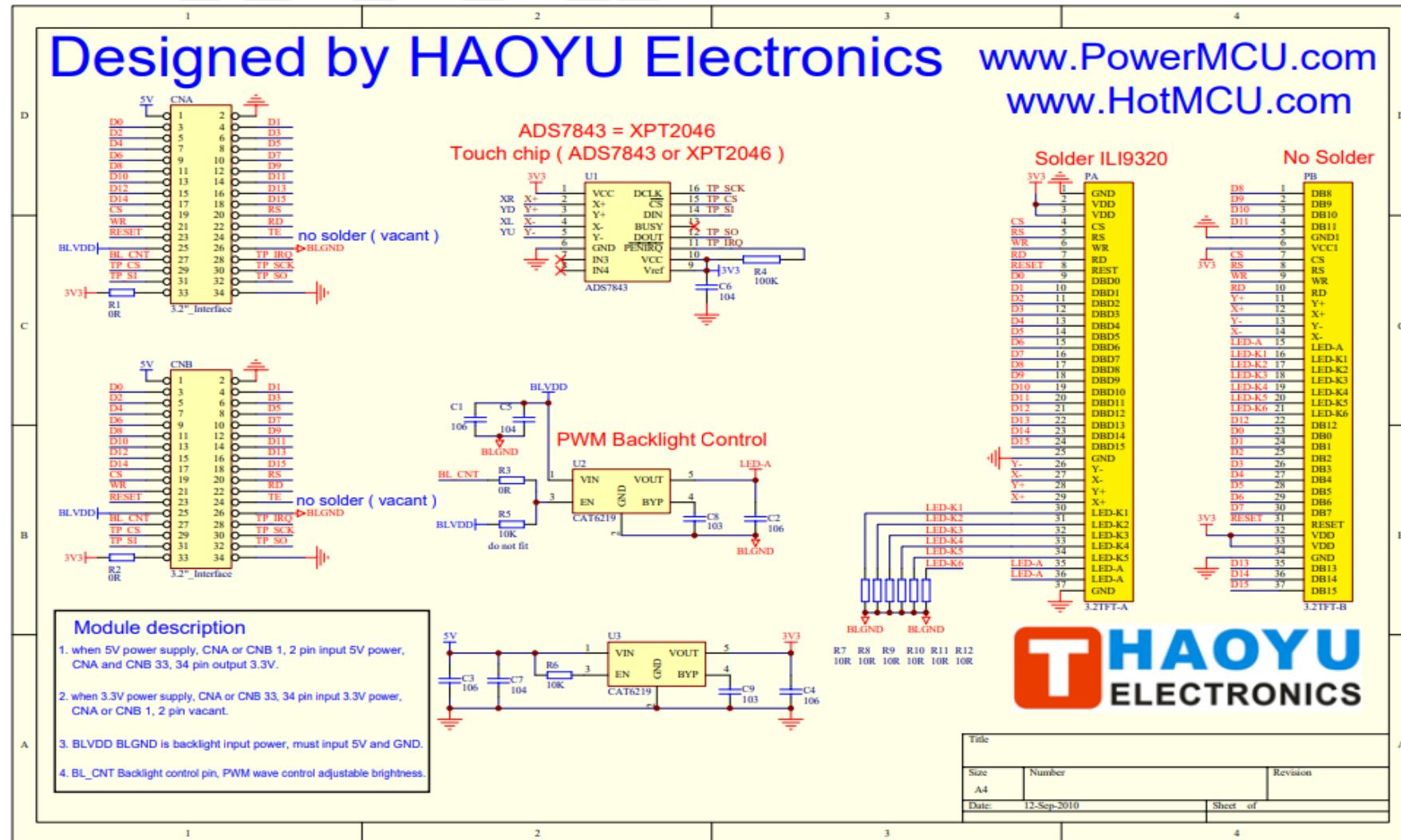

| Appendix C: Schematic of Human Hardware Interface HY32D .....                |                                                                      | 117        |

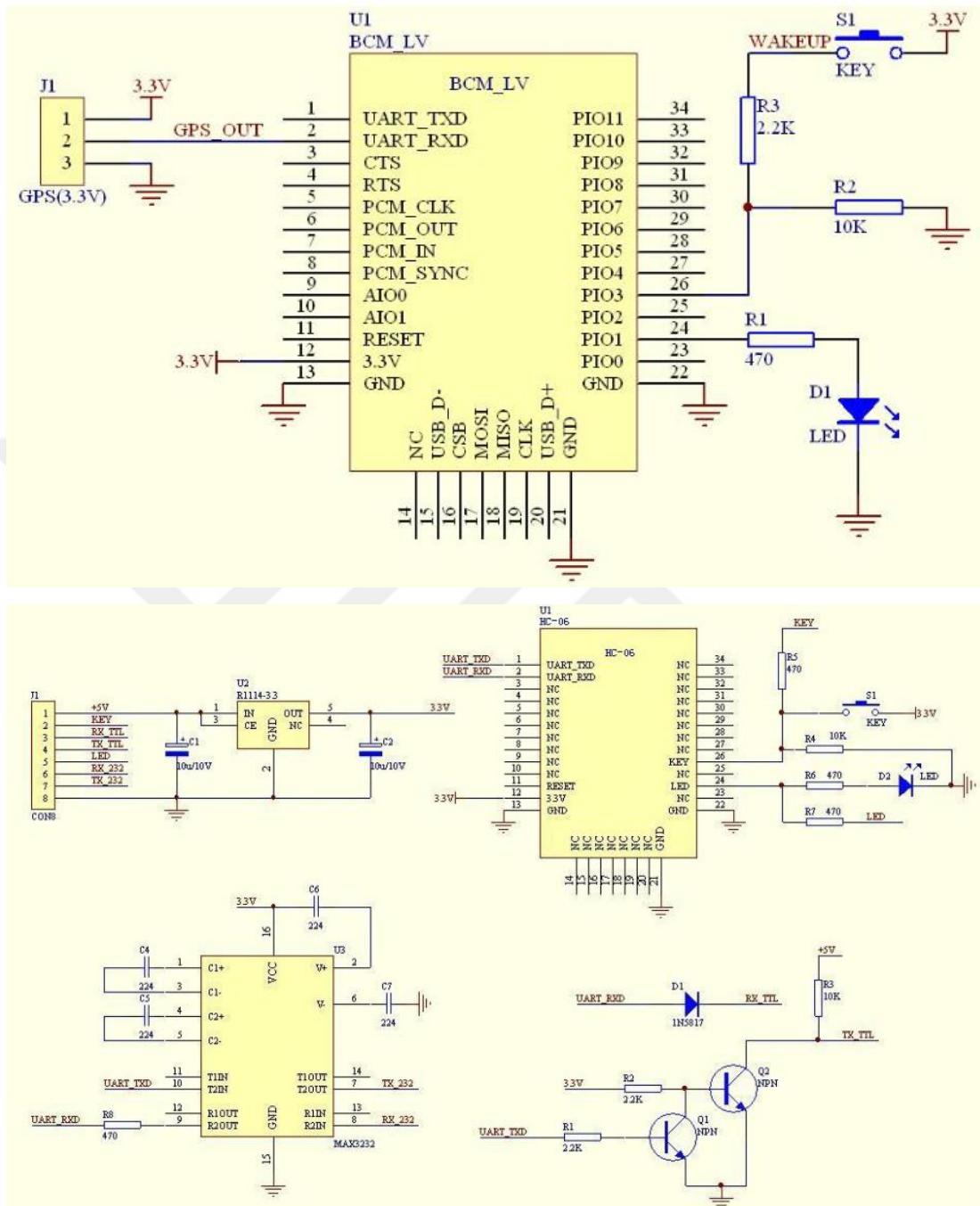

| Appendix D: Schematic of HC-06 Bluetooth Device .....                        |                                                                      | 118        |

| Appendix E: Real-time Operating System Message Queue Service Codes.....      |                                                                      | 119        |

| E.1 Service Function of the System.....                                      |                                                                      | 119        |

| E.2 Message Sending Function to the System.....                              |                                                                      | 119        |

| E.3 Message Requesting Function from the System .....                        |                                                                      | 119        |

| Appendix F: <b>Cosφ</b> Calculating Function by the MCU.....                 |                                                                      | 121        |

| Appendix G: Power Factor Calculating Function by the MCU .....               |                                                                      | 122        |

| Appendix H: MODBUS Communication Address Mapping:.....                       |                                                                      | 123        |

| <b>Cirriculum Vitae .....</b>                                                |                                                                      | <b>124</b> |

## LIST OF TABLES

|                                                                                          | Page |

|------------------------------------------------------------------------------------------|------|

| <b>Table 1.1</b> Electrical device classification according to EN 61000 - 3 - 2 standard | 10   |

| <b>Table 1.2</b> Harmonic limits according to EN 61000 - 3 - 2 standards .....           | 12   |

| <b>Table 1.3</b> Voltage distortion limits according to IEEE 519 - 1992 standard .....   | 12   |

| <b>Table 2.1</b> PLL and adaptive notch filter coefficients .....                        | 32   |

| <b>Table 5.1</b> Experiment results with the different sampling frequency .....          | 98   |

| <b>Table 5.2</b> Experiment results with the different resolutions of ADC .....          | 99   |

| <b>Table 5.3</b> Experiment results with the different samples of ADC .....              | 101  |

| <b>Table 6.1</b> Query .....                                                             | 105  |

| <b>Table 6.2</b> Response.....                                                           | 105  |

## LIST OF FIGURES

|                    | <b>Page</b>                                                         |

|--------------------|---------------------------------------------------------------------|

| <b>Figure 1.1</b>  | Equivalent system block diagram for an energy analyzer .....        |

| <b>Figure 1.2</b>  | 3                                                                   |

| <b>Figure 1.3</b>  | Value of the grid voltage in sine form .....                        |

| <b>Figure 1.4</b>  | 4                                                                   |

| <b>Figure 1.5</b>  | Sinusoidal signals that has the phase difference .....              |

| <b>Figure 1.6</b>  | 5                                                                   |

| <b>Figure 1.7</b>  | Sinusoidal signals that has phase difference.....                   |

| <b>Figure 1.8</b>  | 6                                                                   |

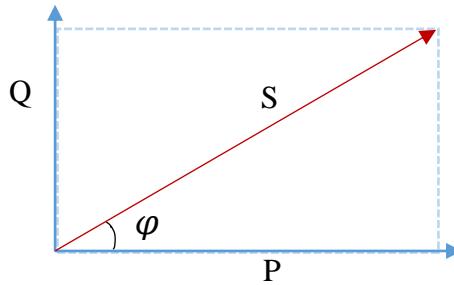

| <b>Figure 2.1</b>  | Power Triangle, Relationship between Power factors .....            |

| <b>Figure 2.2</b>  | 6                                                                   |

| <b>Figure 2.3</b>  | Instantaneous voltage, current and power values .....               |

| <b>Figure 2.4</b>  | 9                                                                   |

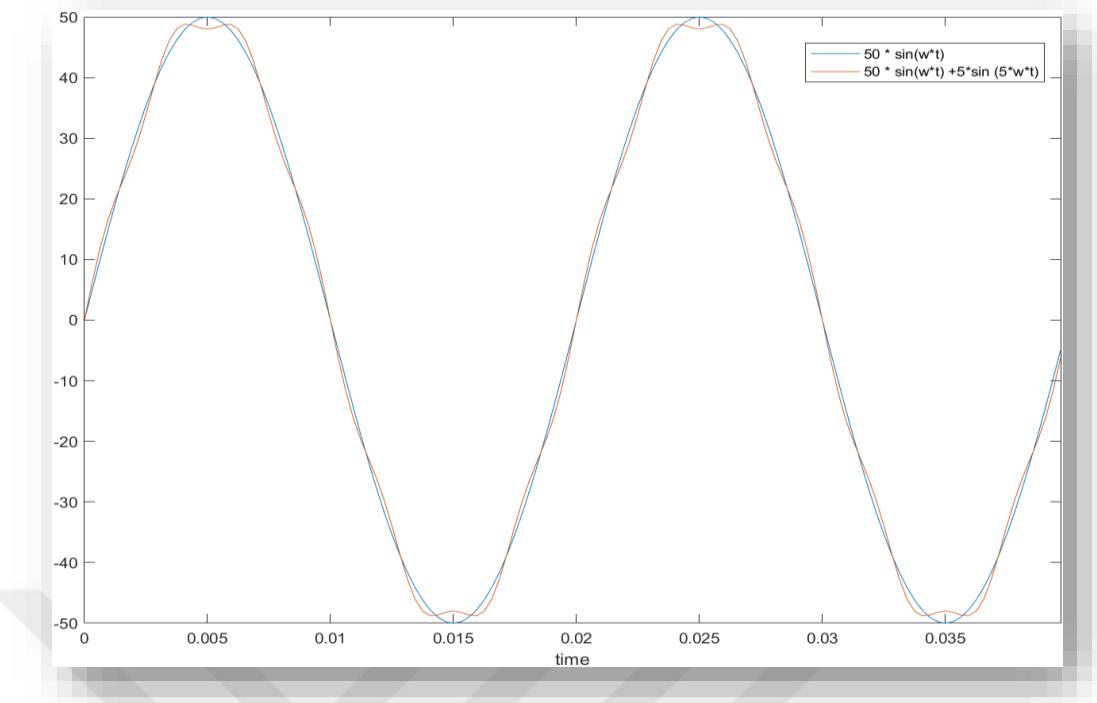

| <b>Figure 2.5</b>  | A current signal with the 5th harmonic in it .....                  |

| <b>Figure 2.6</b>  | 11                                                                  |

| <b>Figure 2.7</b>  | Flow chart to apply standard EN 61000 - 3 -2.....                   |

| <b>Figure 2.8</b>  | 17                                                                  |

| <b>Figure 2.9</b>  | Single Phase PLL With Notch Filter .....                            |

| <b>Figure 2.10</b> | 19                                                                  |

| <b>Figure 2.11</b> | The response of the notch filter .....                              |

| <b>Figure 2.12</b> | 21                                                                  |

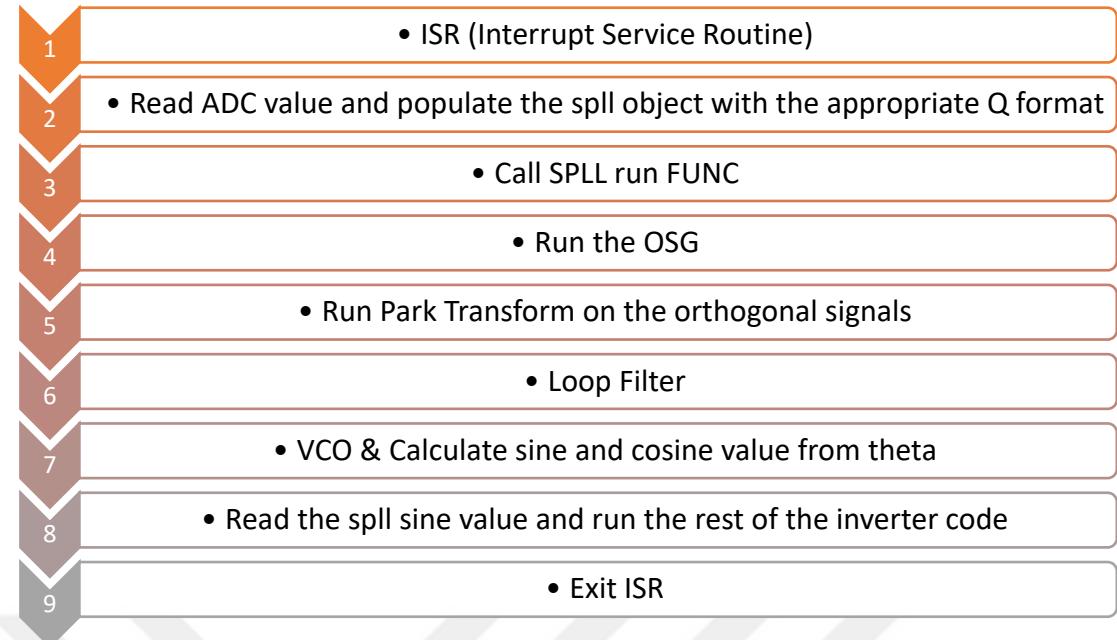

| <b>Figure 2.13</b> | Filter Interrupt flow chart .....                                   |

| <b>Figure 2.14</b> | 23                                                                  |

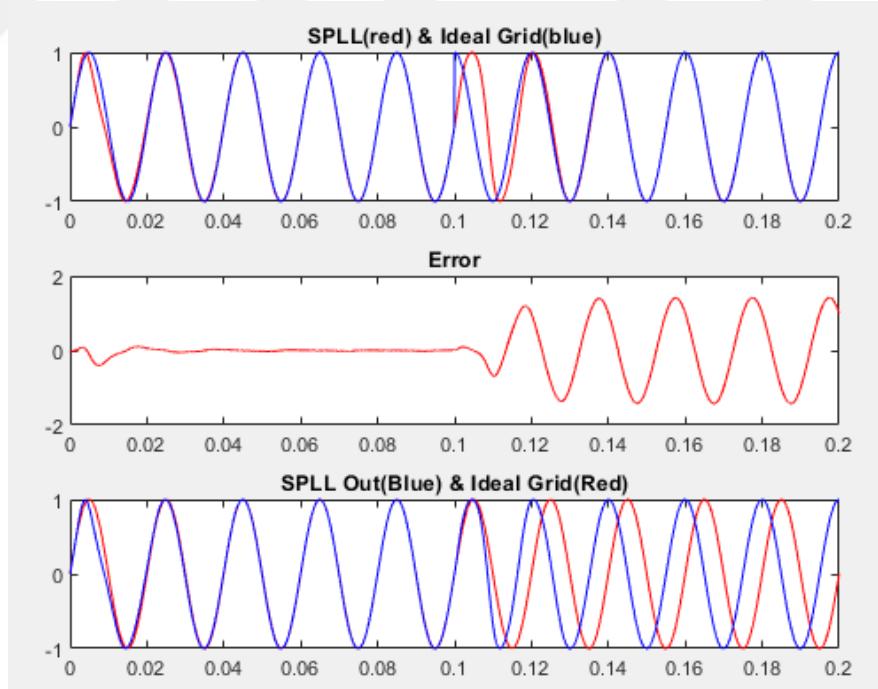

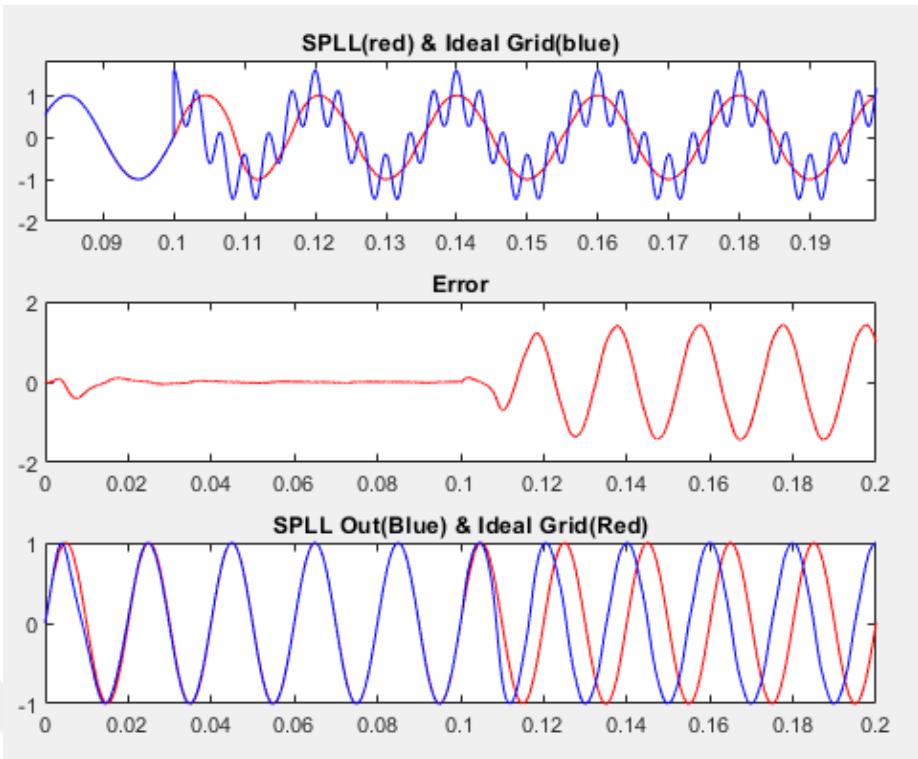

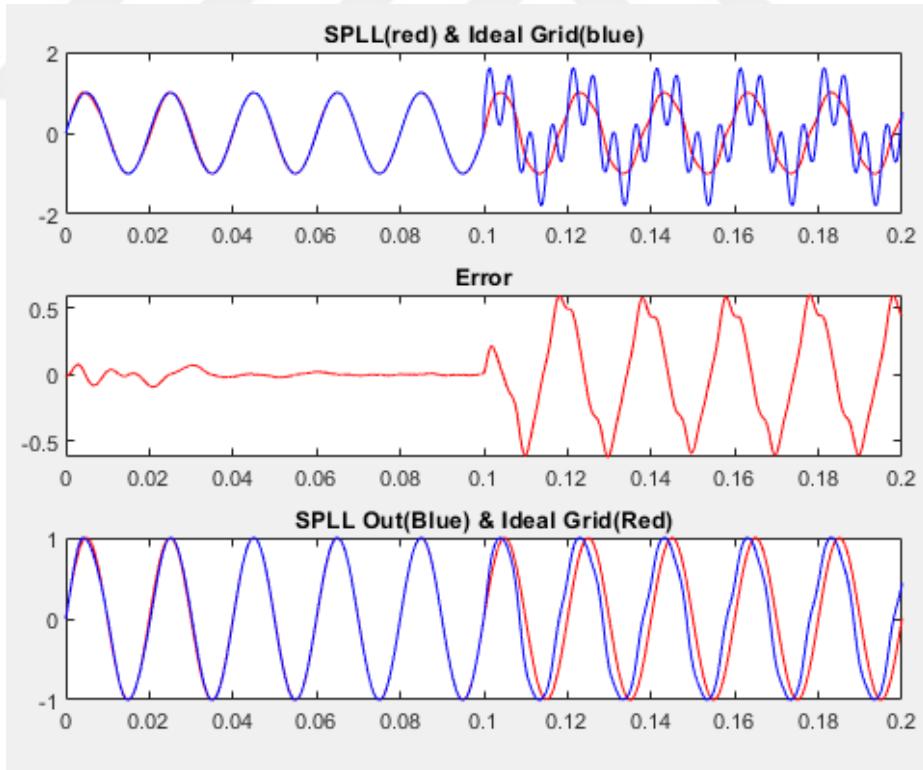

| <b>Figure 2.15</b> | PLL Response to Varying Grid Conditions .....                       |

| <b>Figure 2.16</b> | 23                                                                  |

| <b>Figure 2.17</b> | PLL Response to Varying Grid Conditions .....                       |

| <b>Figure 2.18</b> | 24                                                                  |

| <b>Figure 2.19</b> | PLL Response to Varying Grid Conditions .....                       |

| <b>Figure 2.20</b> | 24                                                                  |

| <b>Figure 2.21</b> | PLL Response to Varying Grid Conditions .....                       |

| <b>Figure 2.22</b> | 25                                                                  |

| <b>Figure 2.23</b> | PLL Response to Varying Grid Conditions .....                       |

| <b>Figure 2.24</b> | 25                                                                  |

| <b>Figure 2.25</b> | PLL Response to Varying Grid Conditions .....                       |

| <b>Figure 2.26</b> | 25                                                                  |

| <b>Figure 2.27</b> | OSG Based Single Phase PLL .....                                    |

| <b>Figure 2.28</b> | 26                                                                  |

| <b>Figure 2.29</b> | Second Order Generalized Integrator for Orthogonal Signal           |

| <b>Figure 2.30</b> | Generation .....                                                    |

| <b>Figure 2.31</b> | 26                                                                  |

| <b>Figure 2.32</b> | Extraction of the Fifth Harmonic Using the SOGI .....               |

| <b>Figure 2.33</b> | 28                                                                  |

| <b>Figure 2.34</b> | Interrupt Filter flow chart .....                                   |

| <b>Figure 2.35</b> | 29                                                                  |

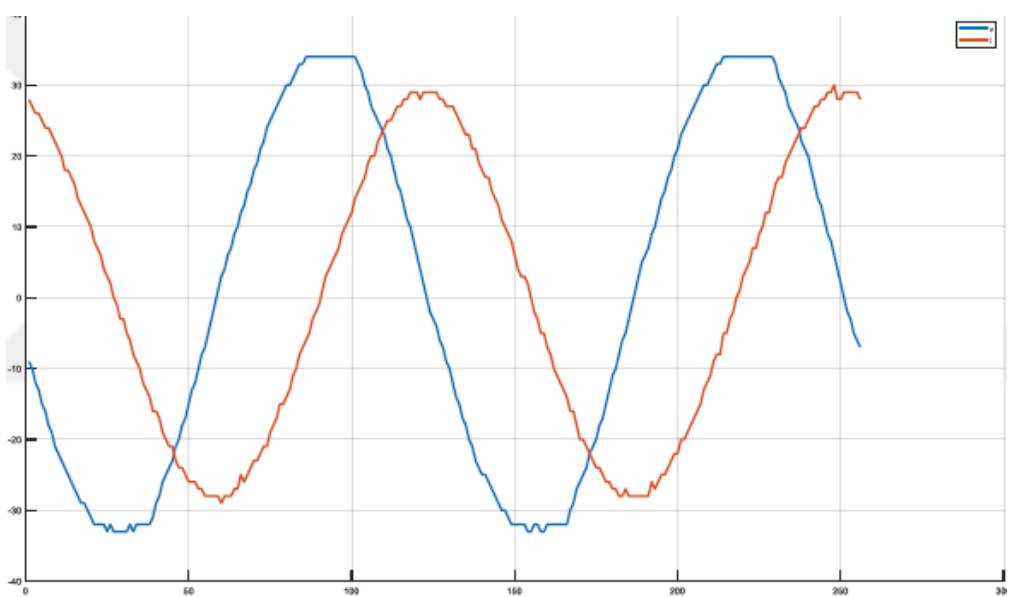

| <b>Figure 2.36</b> | Phase Jump of $90^\circ$ .....                                      |

| <b>Figure 2.37</b> | 29                                                                  |

| <b>Figure 2.38</b> | Phase Jump of $90^\circ$ .....                                      |

| <b>Figure 2.39</b> | 30                                                                  |

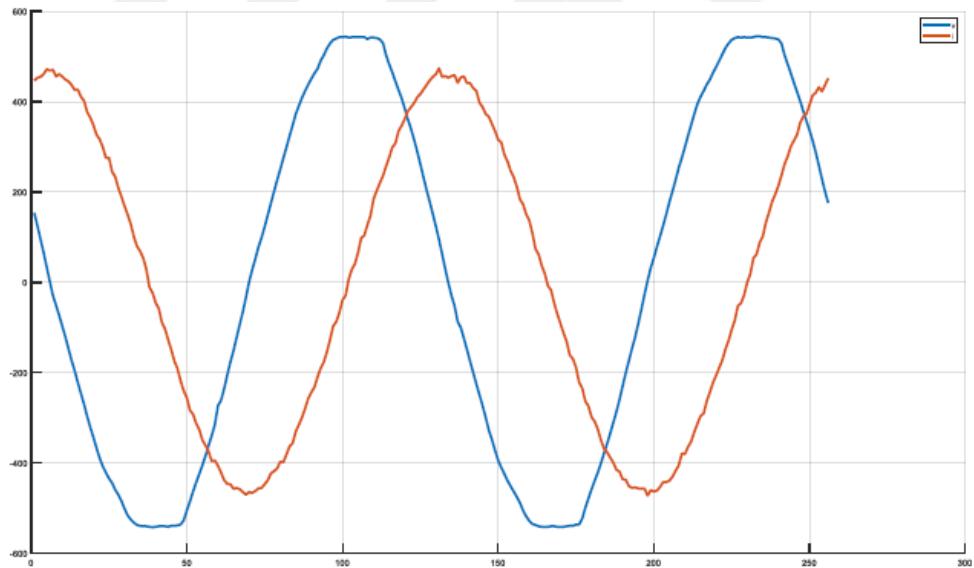

| <b>Figure 2.40</b> | Frequency drift at mid-point highlights the need for adaptive notch |

| <b>Figure 2.41</b> | filter .....                                                        |

| <b>Figure 2.42</b> | 30                                                                  |

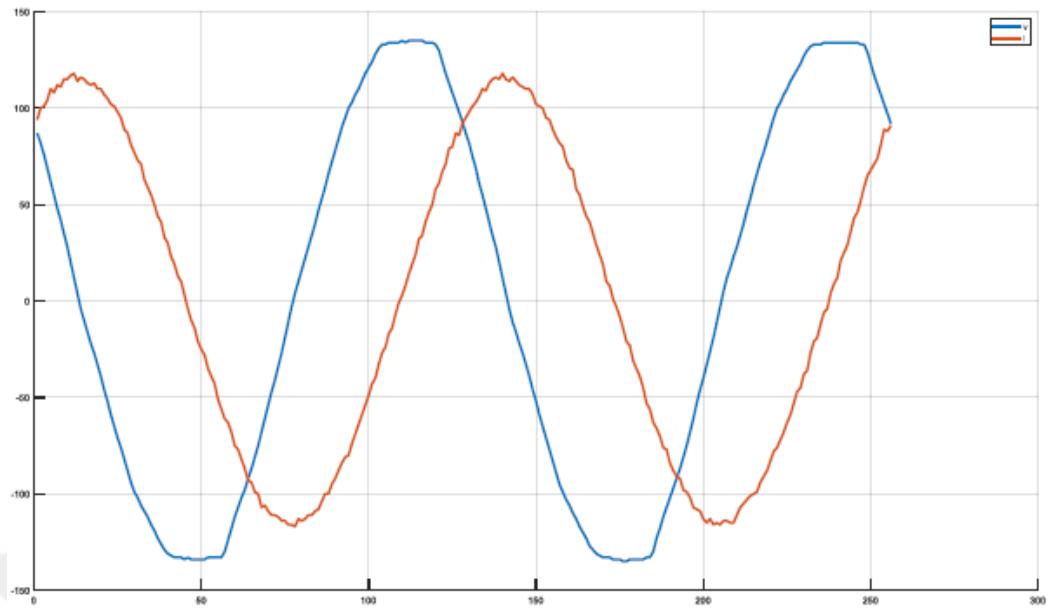

| <b>Figure 2.43</b> | Amplitude change (Voltage Sags and Dips).....                       |

| <b>Figure 2.44</b> | 31                                                                  |

| <b>Figure 2.45</b> | Amplitude change with harmonics (Voltage Sags and Dips).....        |

| <b>Figure 2.46</b> | 31                                                                  |

|                    |                                                                                                                                     |    |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|----|

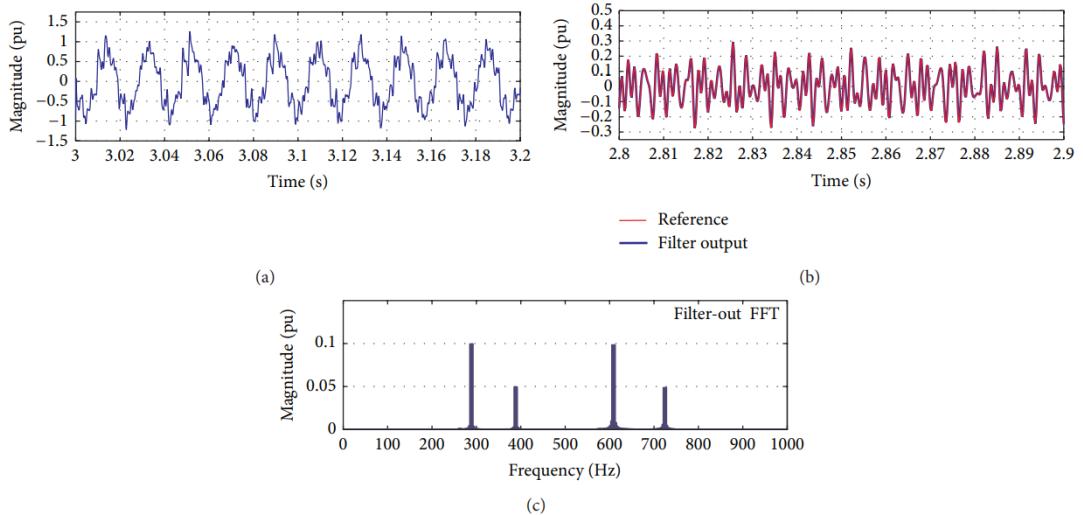

| <b>Figure 2.19</b> | The signal $x(t)$ for $f = 50$ Hz and $T = 0.2$ s .....                                                                             | 32 |

| <b>Figure 2.20</b> | Under the multiple disturbances; (a) the signal, $x(t)$ , (b) reference-filter output signal, and (c) FFT of the filter output..... | 33 |

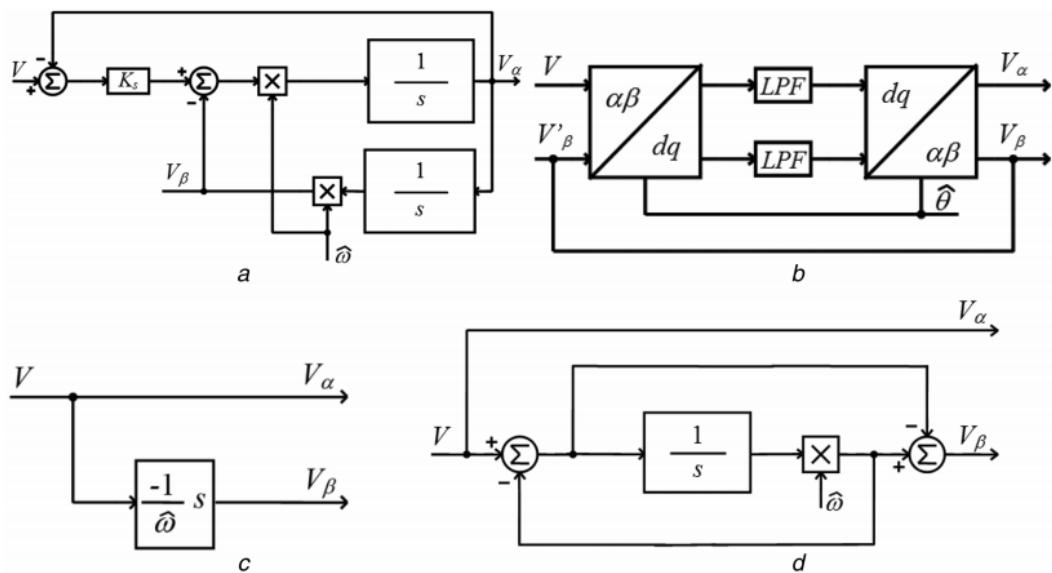

| <b>Figure 2.21</b> | Single-phase PLL application with OSG.....                                                                                          | 33 |

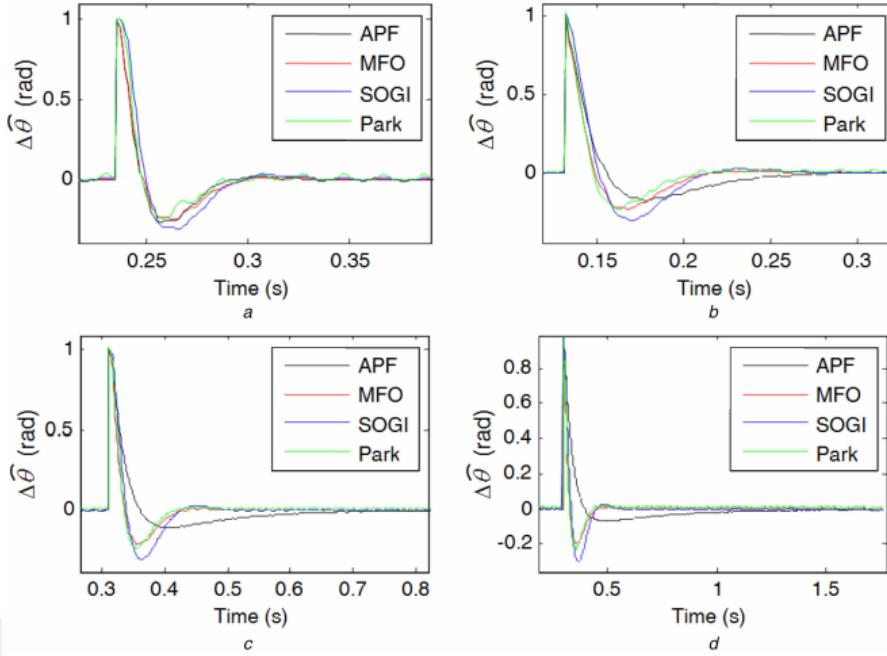

| <b>Figure 2.22</b> | Conventional OSG; a) SOGI, b) Park, c) Derivative, d) APF PLL ..                                                                    | 33 |

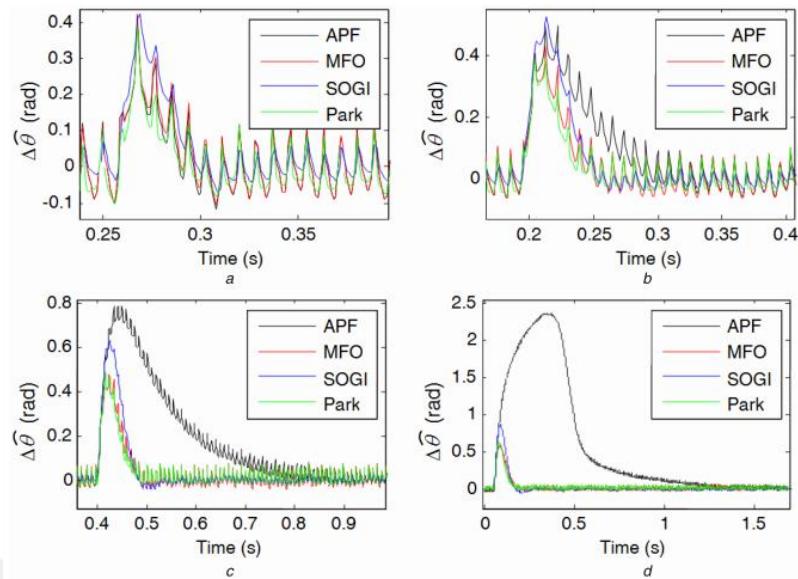

| <b>Figure 2.23</b> | Responses of the estimated angle error for 1 rad step change in PLL input phase .....                                               | 34 |

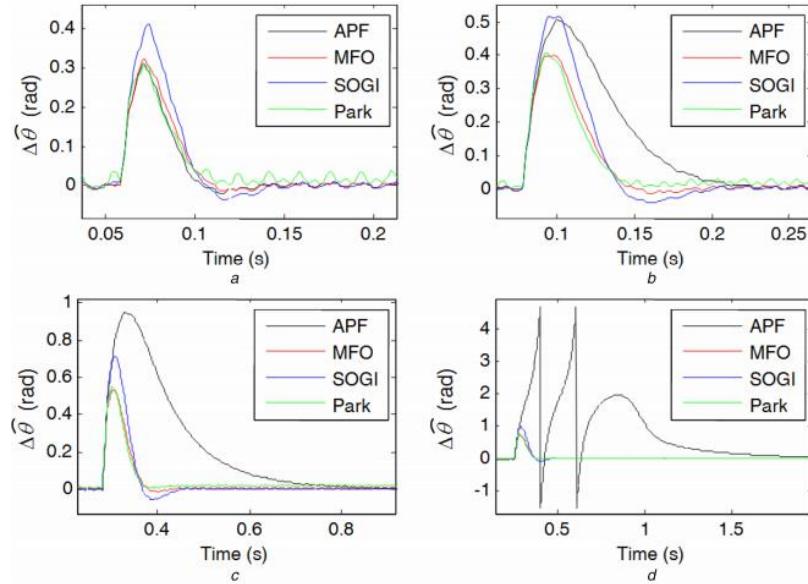

| <b>Figure 2.24</b> | Responses of the estimated angle error for 50 rad/s step change in PLL input frequency .....                                        | 34 |

| <b>Figure 2.25</b> | Responses of the estimated angle error for 50 rad/s step change in PLL input frequency .....                                        | 35 |

| <b>Figure 2.26</b> | Classic PLL PSIM model .....                                                                                                        | 35 |

| <b>Figure 2.27</b> | Response of MATLAB for Discrete-time transfer function .....                                                                        | 37 |

| <b>Figure 2.28</b> | Response of MATLAB for Continuous-time transfer function.....                                                                       | 37 |

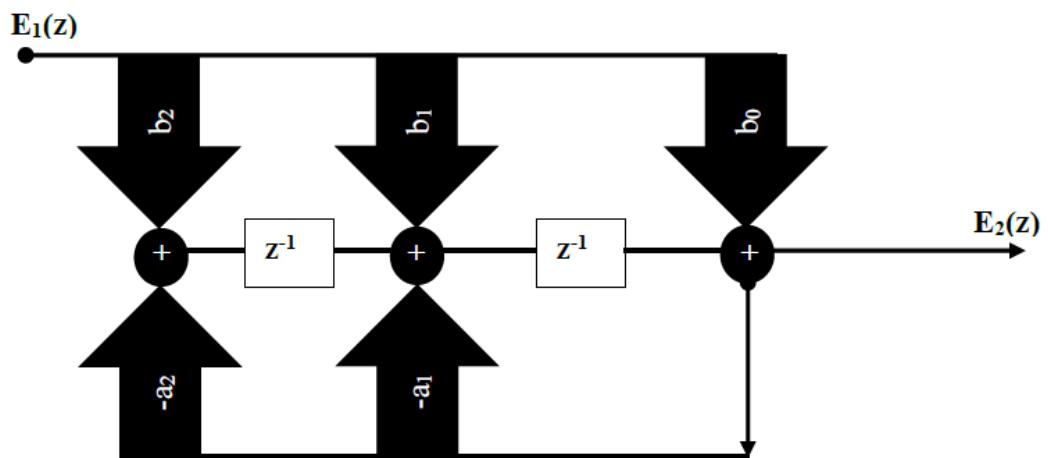

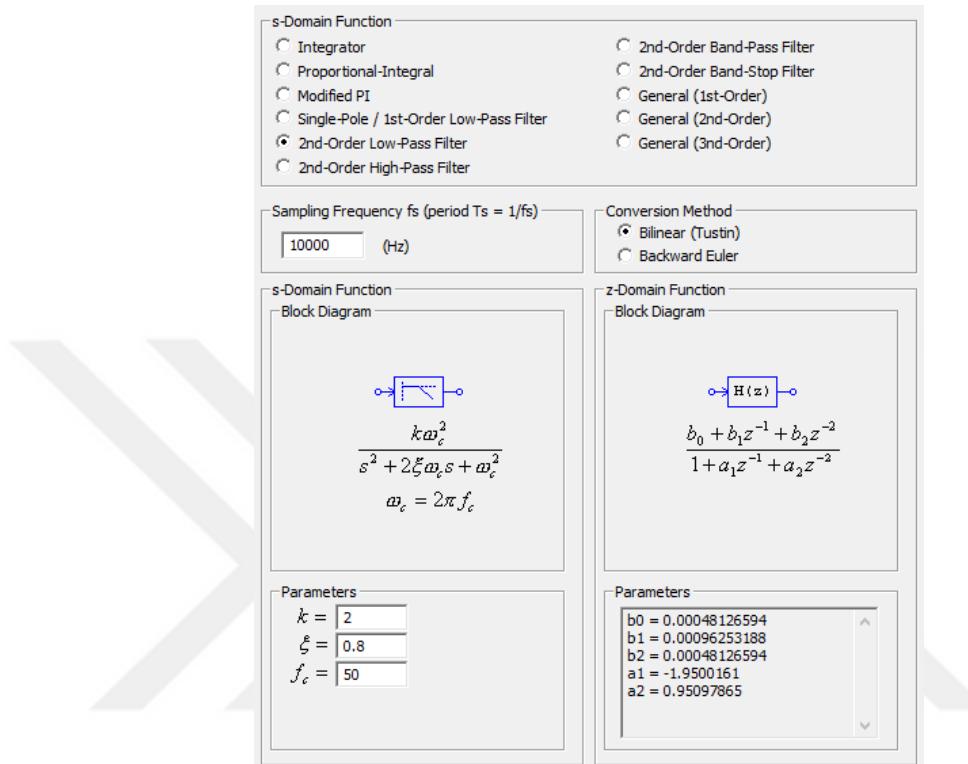

| <b>Figure 2.29</b> | Programming block diagram for a second order low pass filter.....                                                                   | 38 |

| <b>Figure 2.30</b> | Calculation of filter coefficients with PSIM.....                                                                                   | 39 |

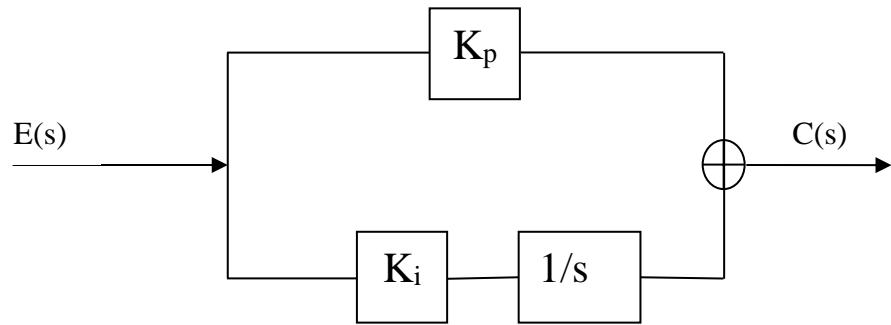

| <b>Figure 2.31</b> | General structure of the PI controller .....                                                                                        | 40 |

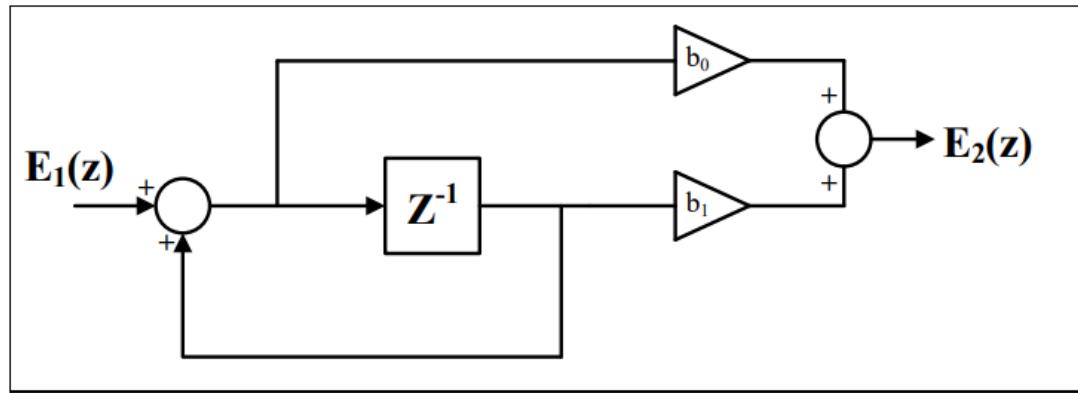

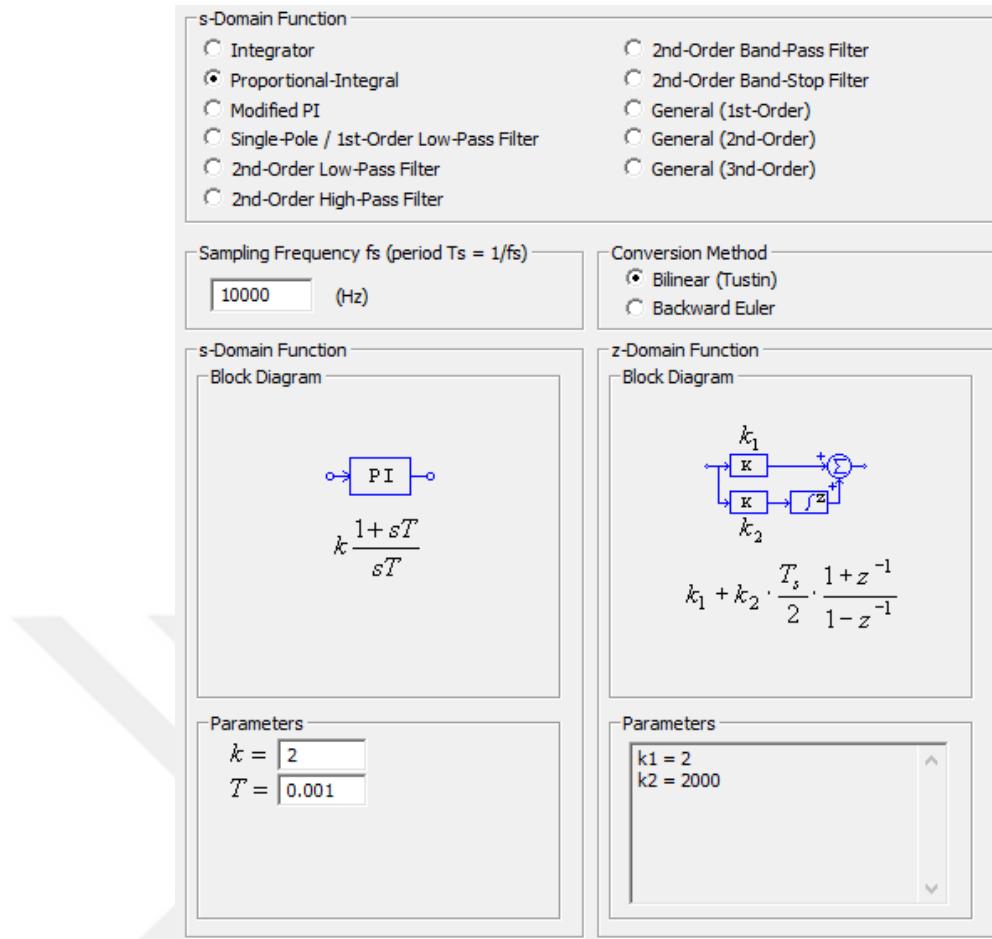

| <b>Figure 2.32</b> | Programming block diagram for PI controller.....                                                                                    | 42 |

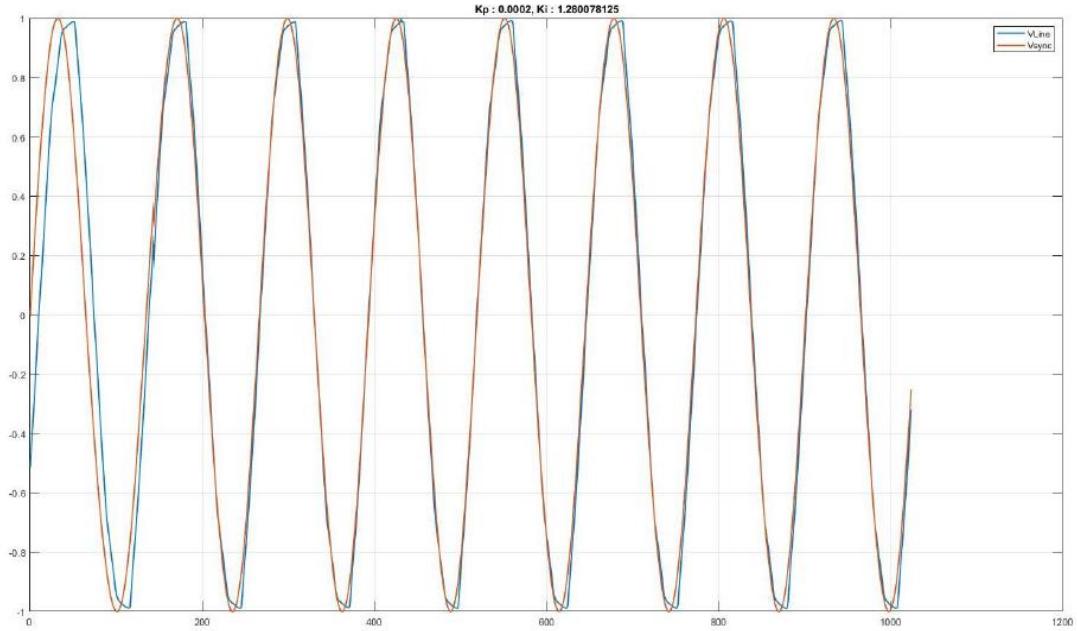

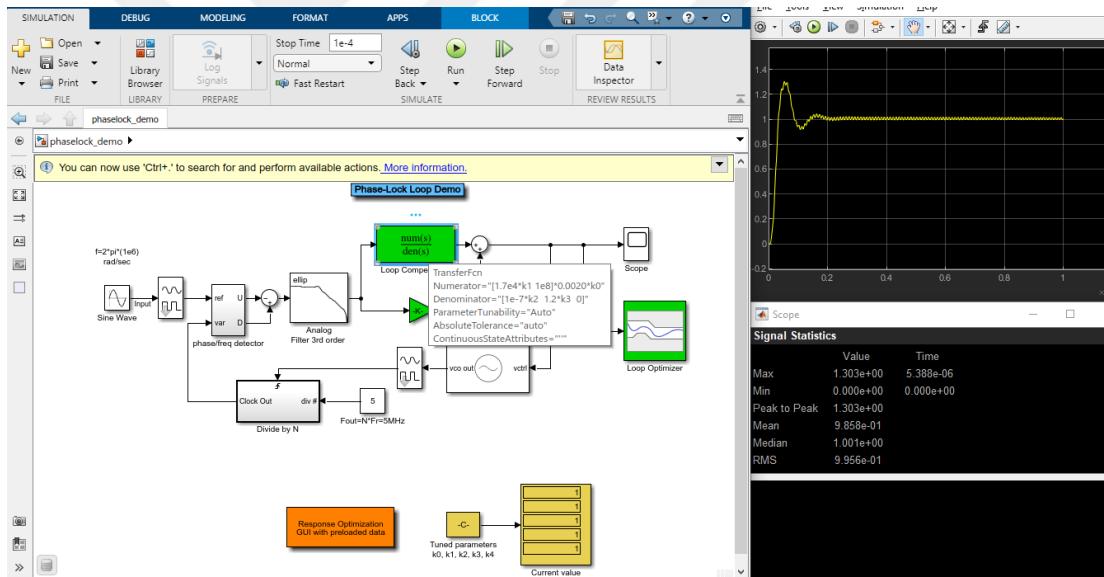

| <b>Figure 2.33</b> | Calculation of $KP$ and $Ki$ coefficients with Simulink environment                                                                 | 43 |

| <b>Figure 2.34</b> | Discrete time block diagram of the classical PLL model .....                                                                        | 43 |

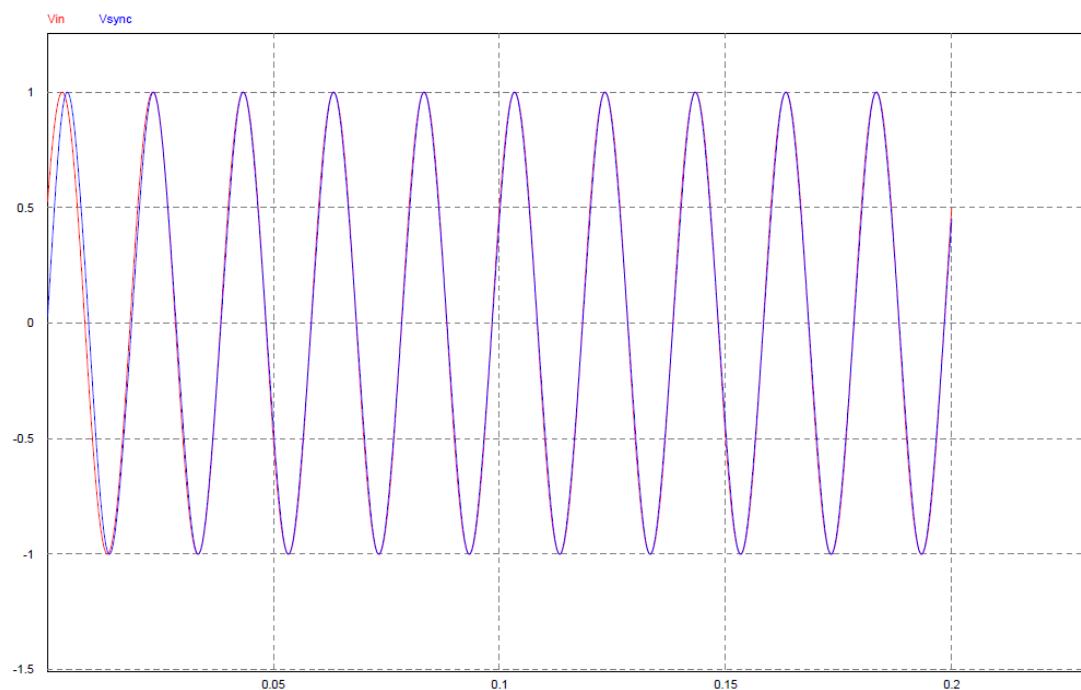

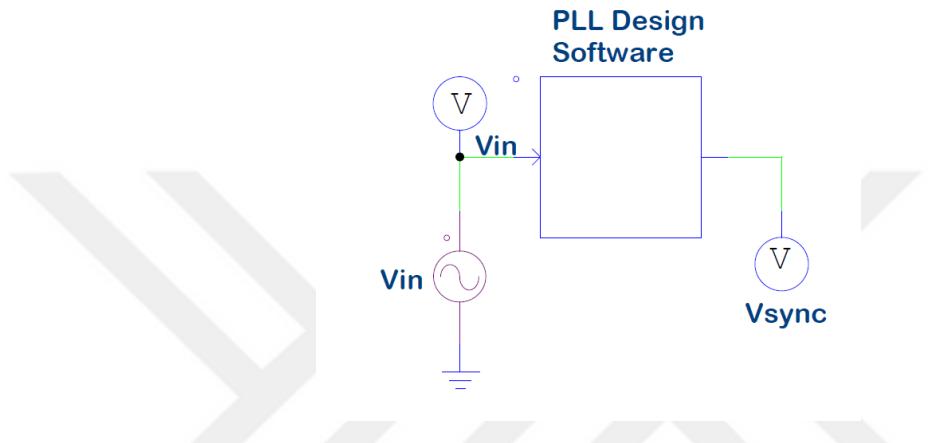

| <b>Figure 2.35</b> | Response of digital PLL to sinusoidal input signal .....                                                                            | 44 |

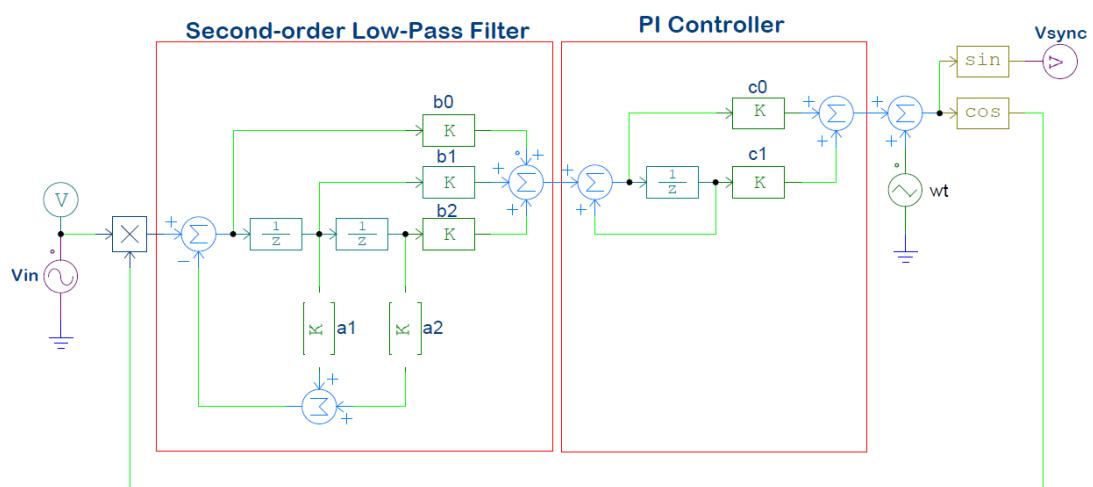

| <b>Figure 2.36</b> | Software implementation of digital PLL .....                                                                                        | 45 |

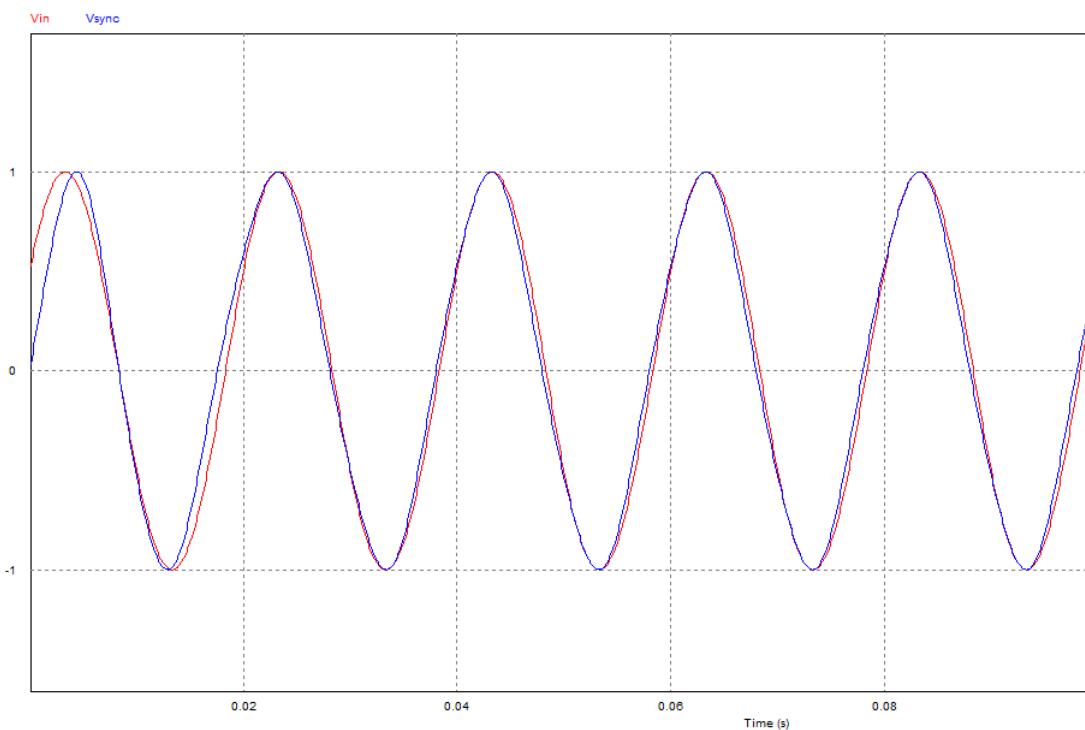

| <b>Figure 2.37</b> | Software PLL's response to sinusoidal input signal .....                                                                            | 45 |

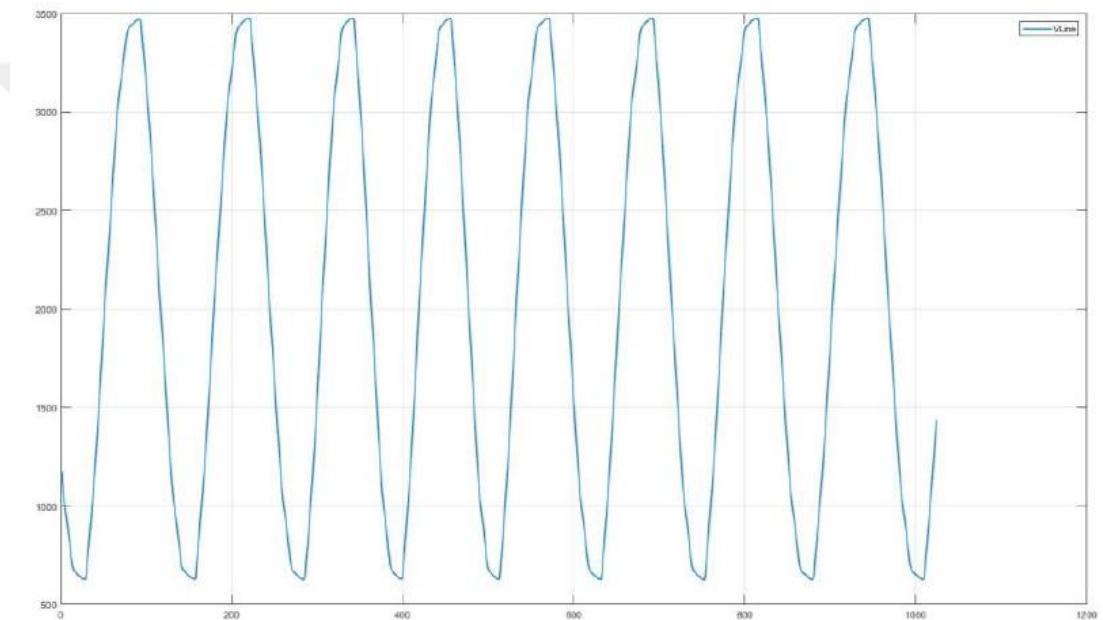

| <b>Figure 2.38</b> | Sampled Signal from the grid voltage ( $V_{line}$ ).....                                                                            | 47 |

| <b>Figure 2.39</b> | PLL output signal that locked to the grid signal .....                                                                              | 48 |

| <b>Figure 2.40</b> | MATLAB Simulink Demo PLL Program Outputs.....                                                                                       | 49 |

| <b>Figure 3.1</b>  | Sophisticated Triac Driver Optoisolator 230 VAC to 12 VDC Power Supply Circuit                                                      | 50 |

| <b>Figure 3.2</b>  | 5 VDC circuit for TFT-LCD.....                                                                                                      | 50 |

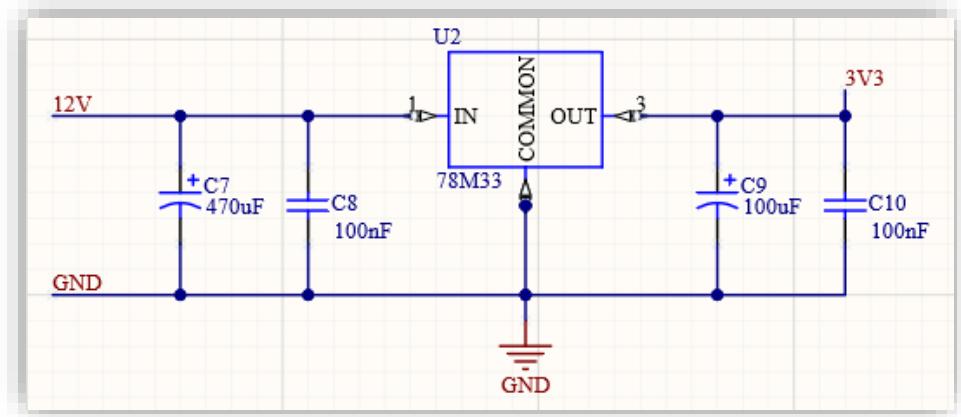

| <b>Figure 3.3</b>  | 3V3 DC circuit for electronic components .....                                                                                      | 51 |

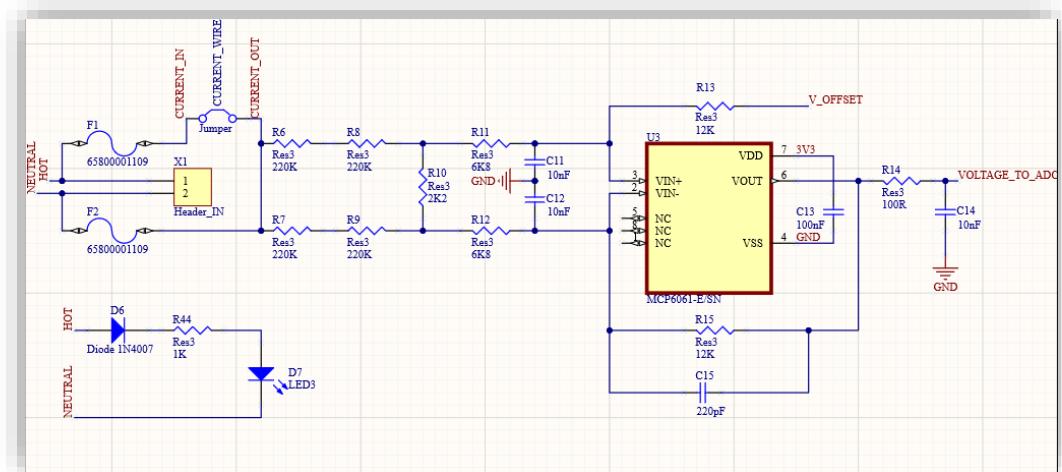

| <b>Figure 3.4</b>  | Voltage detection circuit .....                                                                                                     | 51 |

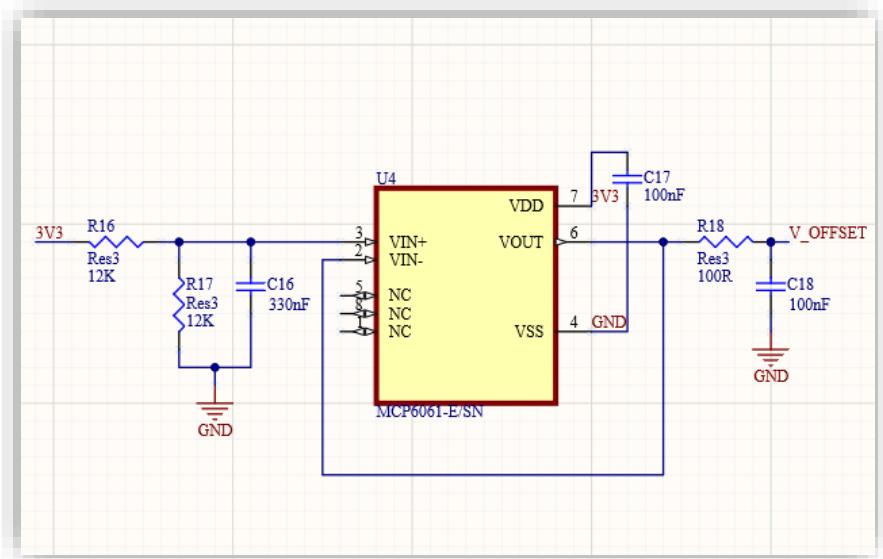

| <b>Figure 3.5</b>  | Voltage offset circuit .....                                                                                                        | 53 |

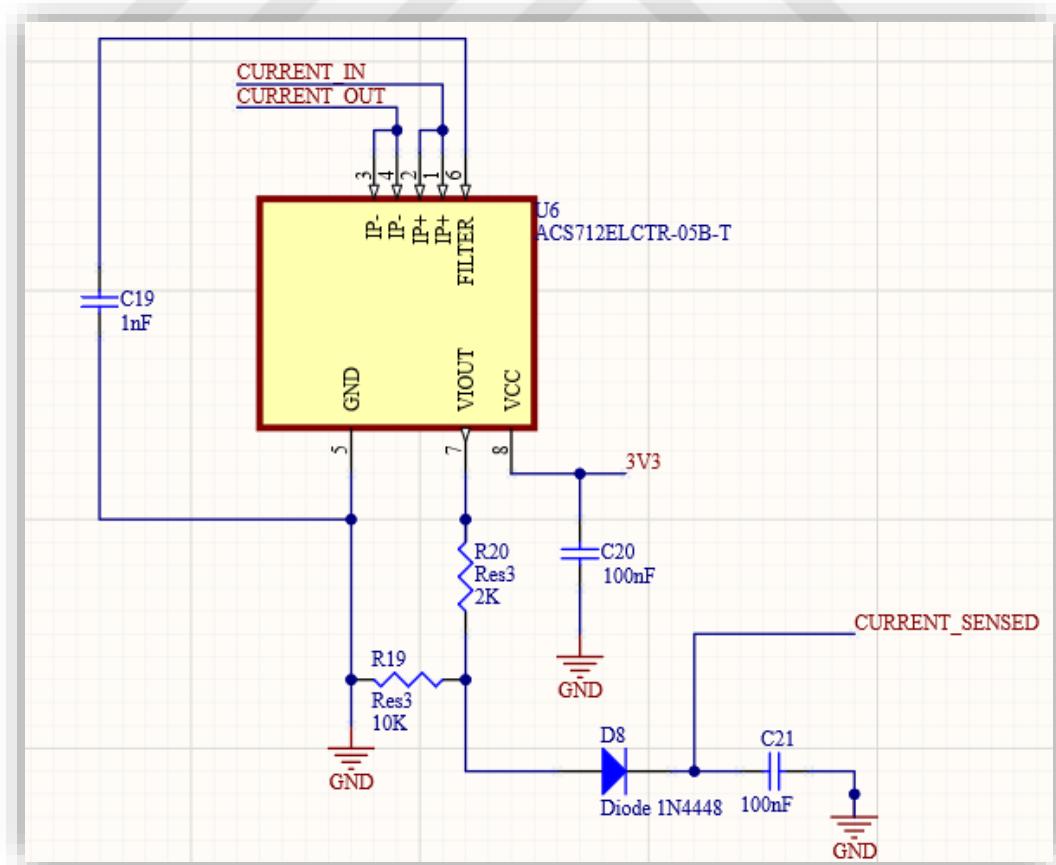

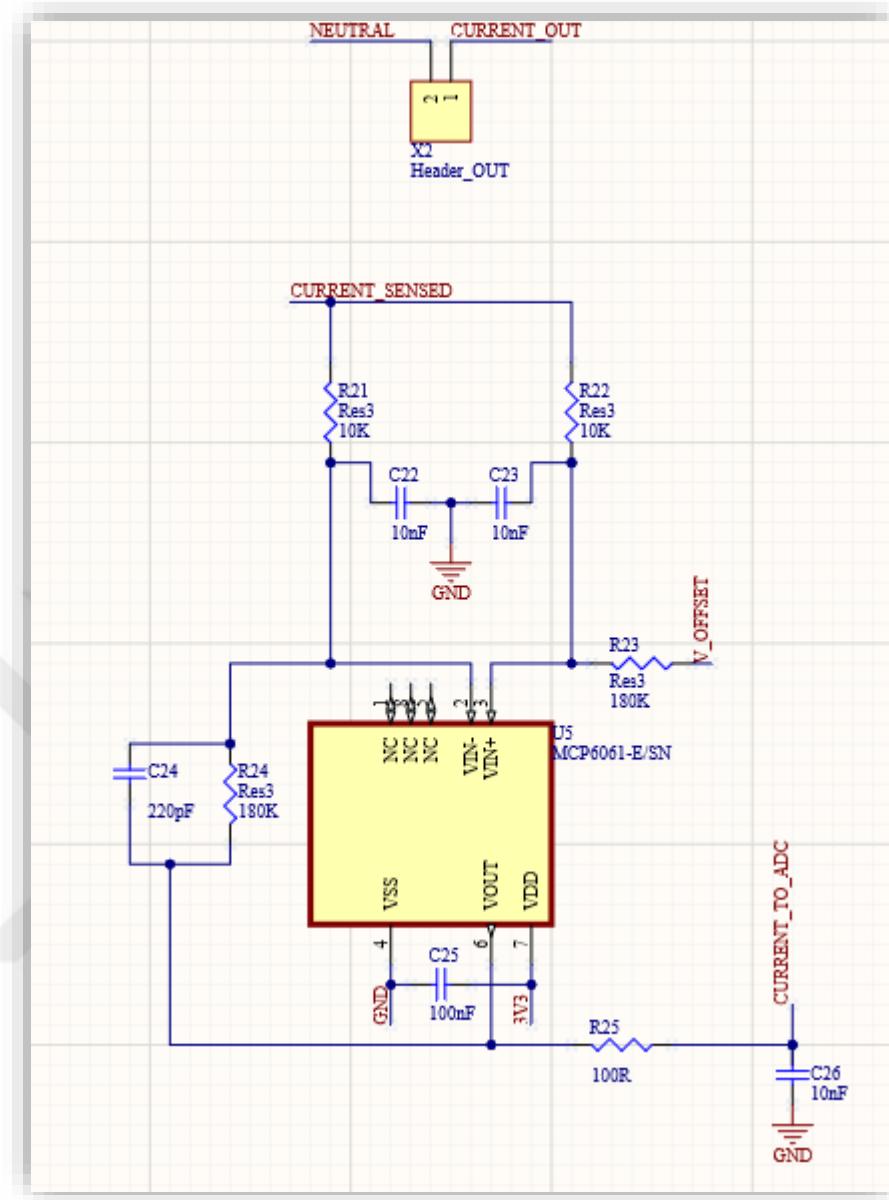

| <b>Figure 3.6</b>  | Current detection circuit with hall effect sensor .....                                                                             | 53 |

| <b>Figure 3.7</b>  | Current output circuit.....                                                                                                         | 54 |

|                     |                                                                   |    |

|---------------------|-------------------------------------------------------------------|----|

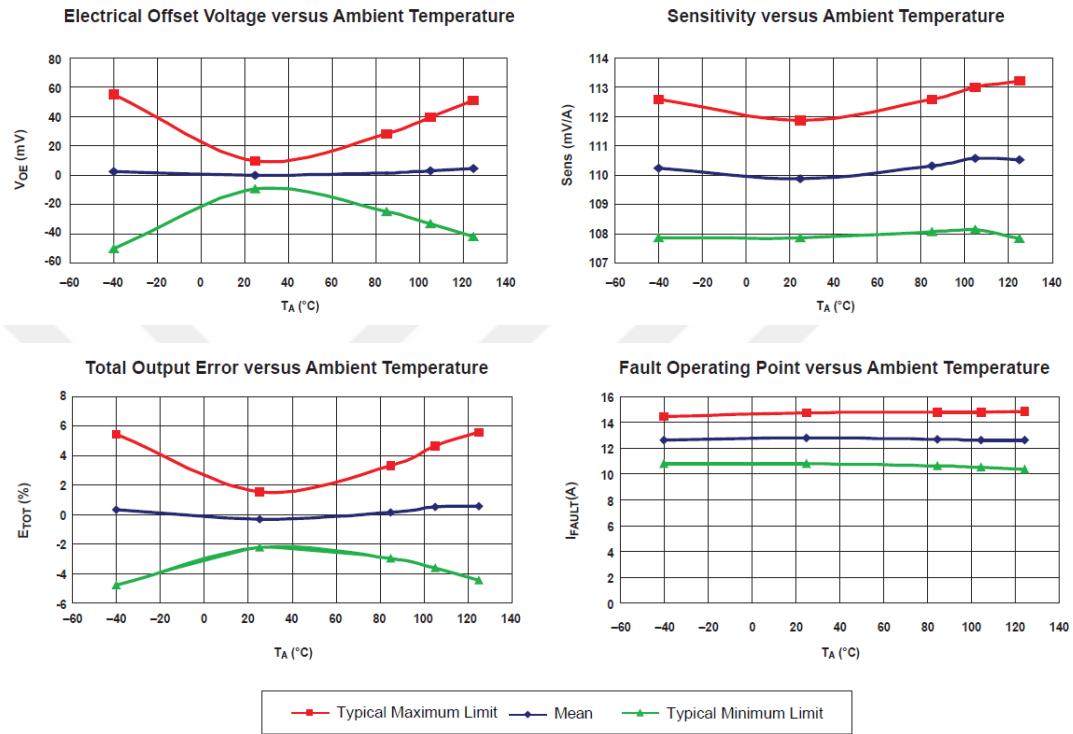

| <b>Figure 3.8</b>   | Characteristic Performance data of ACS711KLCA-25A, Vcc=3,3 V      | 55 |

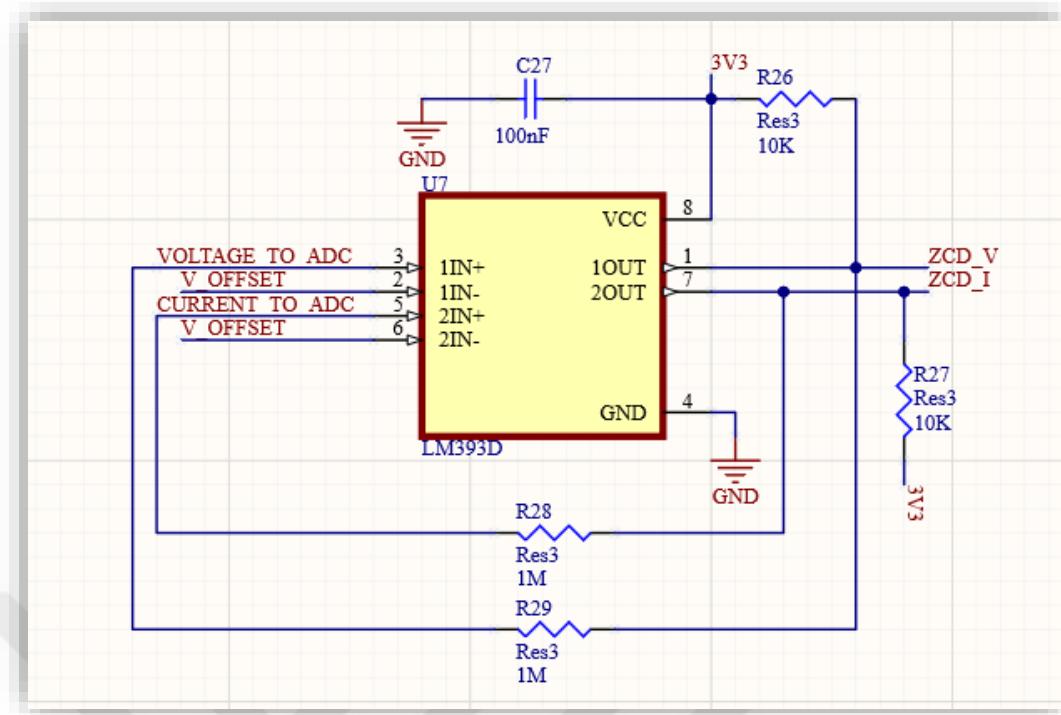

| <b>Figure 3.9</b>   | Zero-cross detection circuit .....                                | 56 |

| <b>Figure 3.10</b>  | Battery backup circuit.....                                       | 56 |

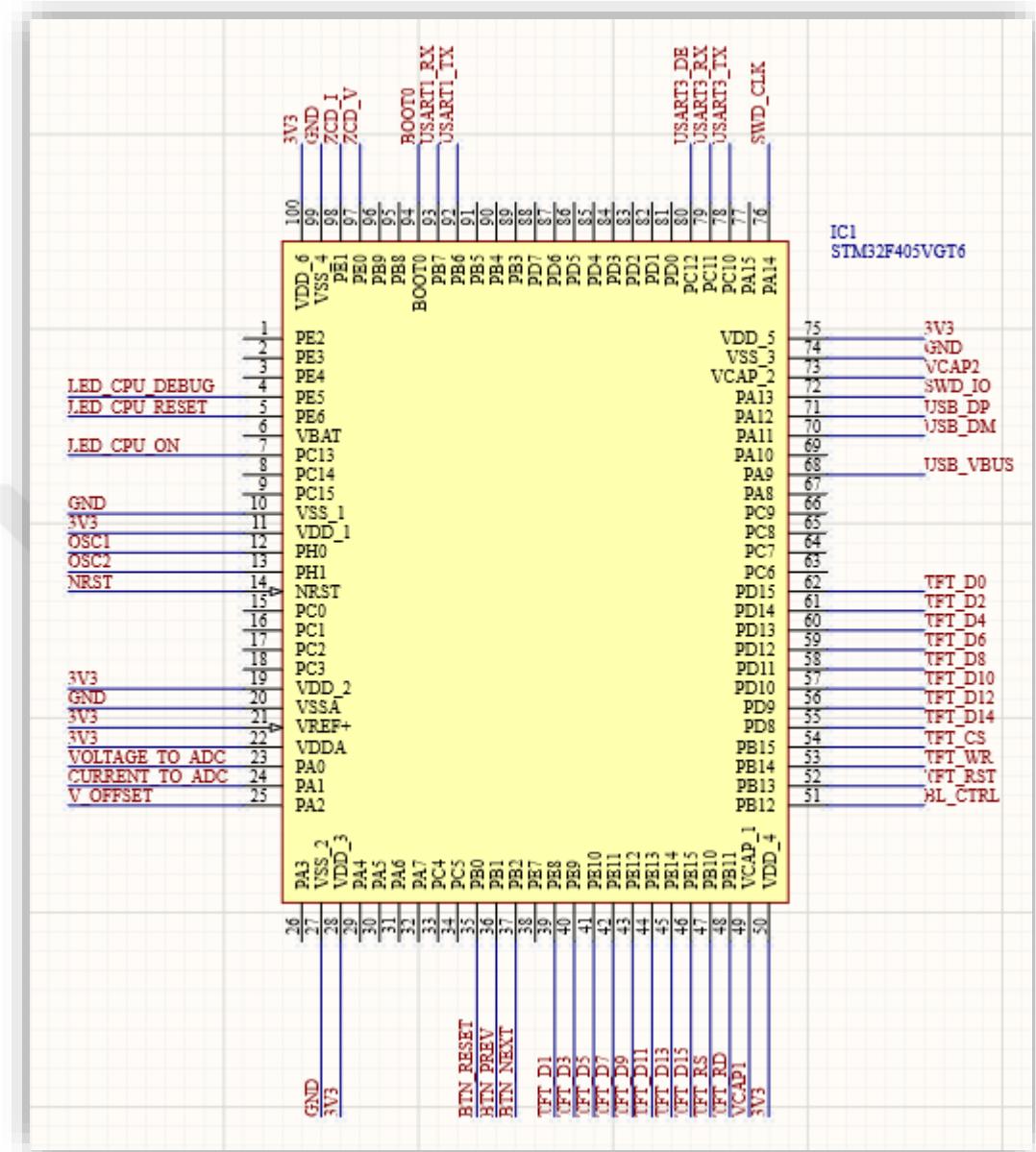

| <b>Figure 3.11</b>  | Central processing unit (CPU) input and outputs .....             | 57 |

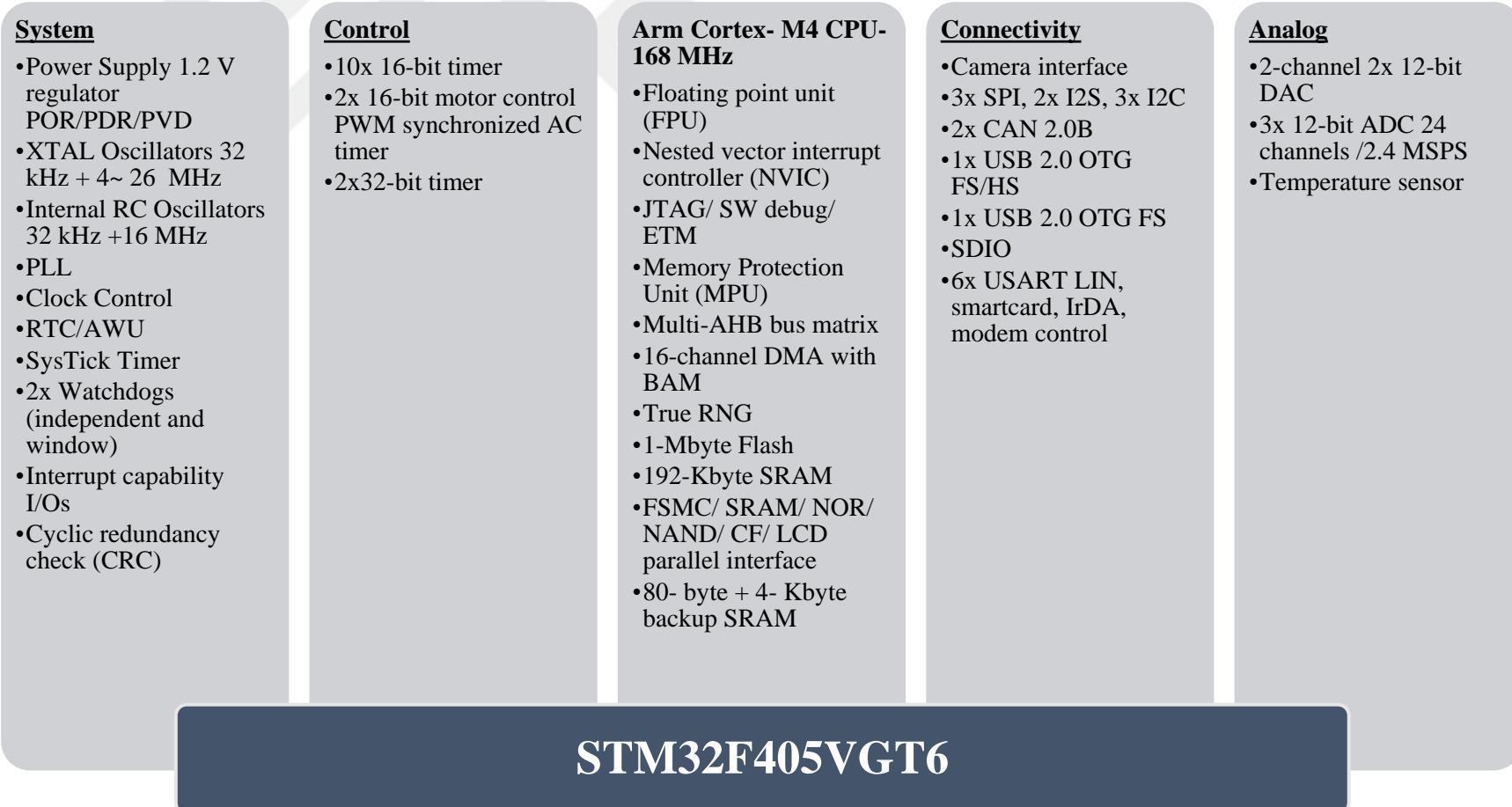

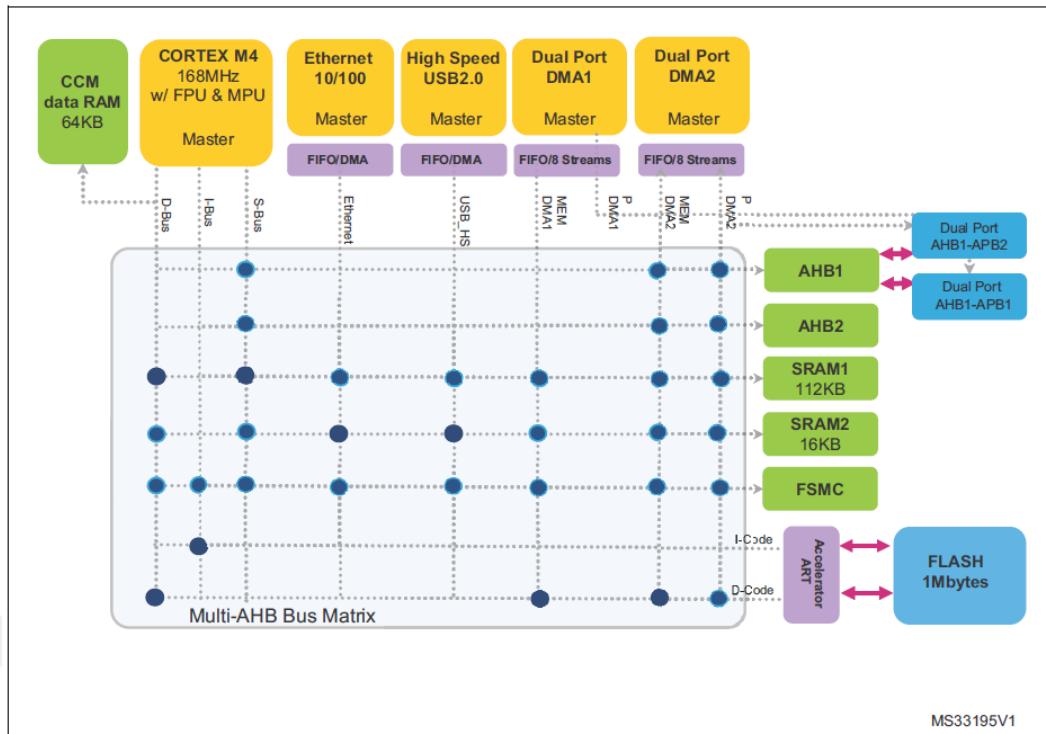

| <b>Figure 3.12</b>  | STM32F405VGT6 microchip designed by STM. ....                     | 59 |

| <b>Figure 3.13</b>  | General features of the STM32F405VGT6 chip by STM. ....           | 60 |

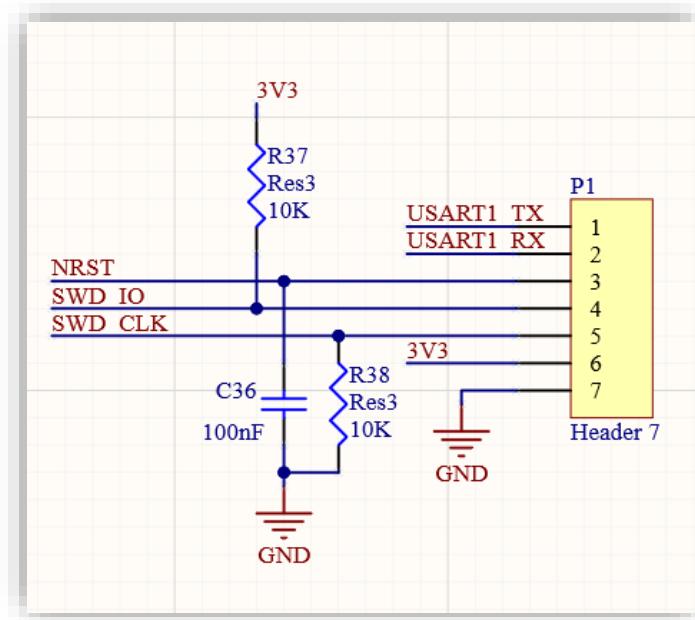

| <b>Figure 3.14</b>  | ST-LINK/V2 in-circuit debugger/programmer for STM8 and STM32      | 61 |

| <b>Figure 3.15</b>  | Serial communication debugger interface circuit .....             | 61 |

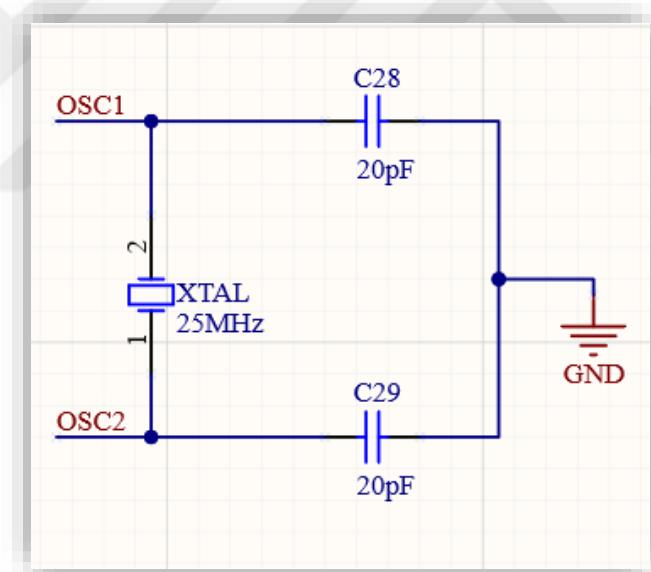

| <b>Figure 3.16</b>  | External Oscillator circuit .....                                 | 62 |

| <b>Figure 3.17</b>  | Human Hardware Interface TFT-LCD Front view.....                  | 63 |

| <b>Figure 3.18</b>  | Human Hardware Interface TFT-LCD Rear view .....                  | 63 |

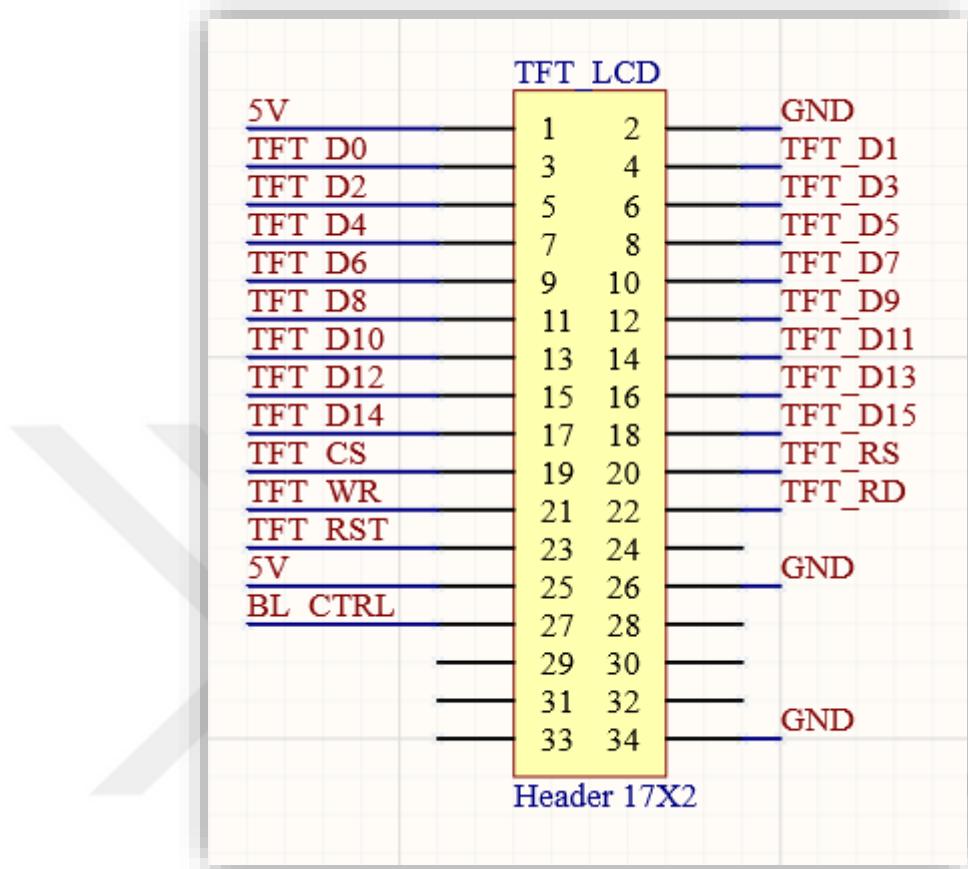

| <b>Figure 3.19</b>  | Header wiring diagram for connection between TFT-LCD and MCU..... | 64 |

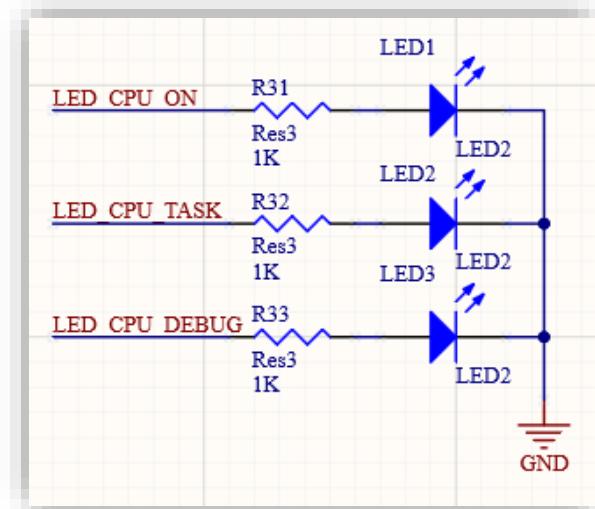

| <b>Figure 3.20</b>  | LED Indicators.....                                               | 65 |

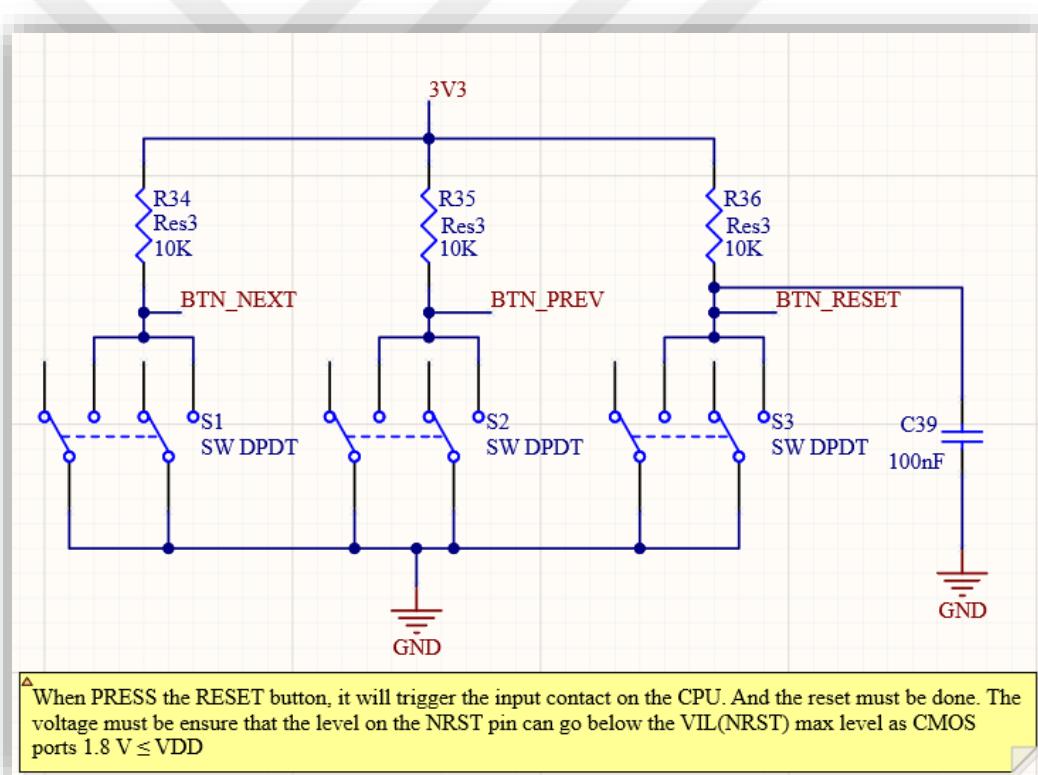

| <b>Figure 3.21</b>  | Human PCB Interface buttons .....                                 | 65 |

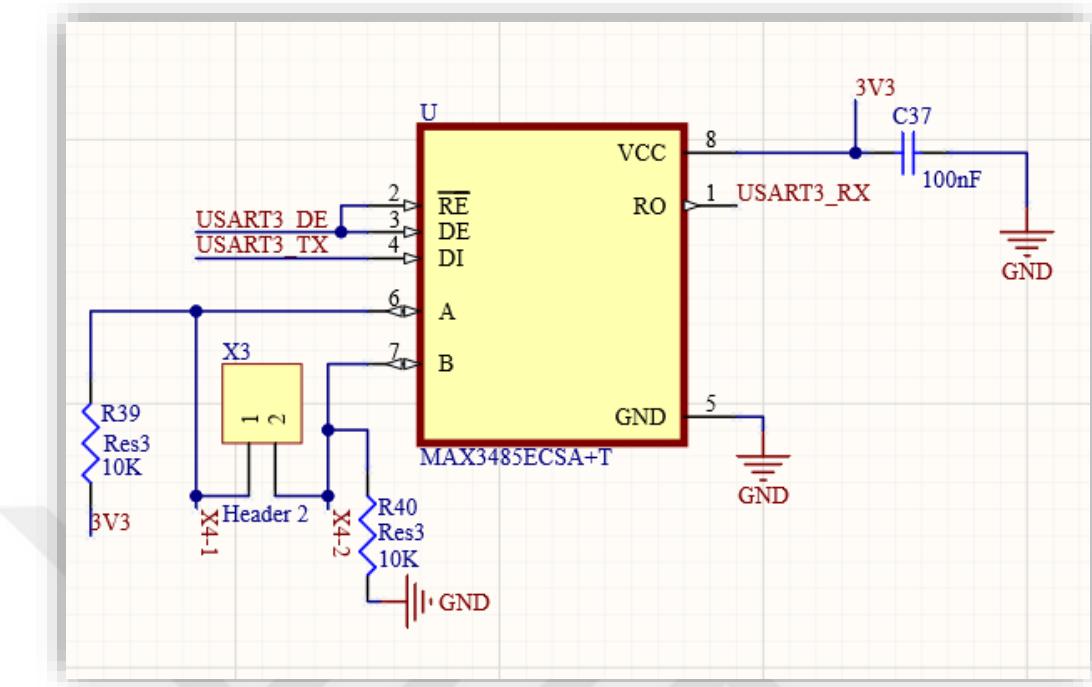

| <b>Figure 3.22:</b> | RS-485 Interface circuit with the MCU .....                       | 66 |

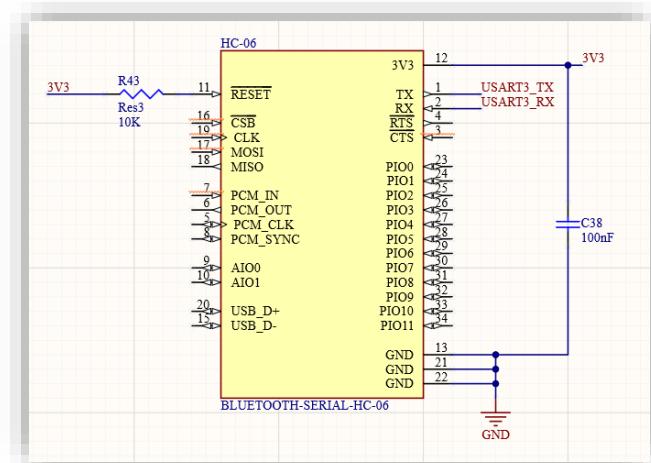

| <b>Figure 3.23</b>  | Bluetooth Serial Interface with the MCU .....                     | 66 |

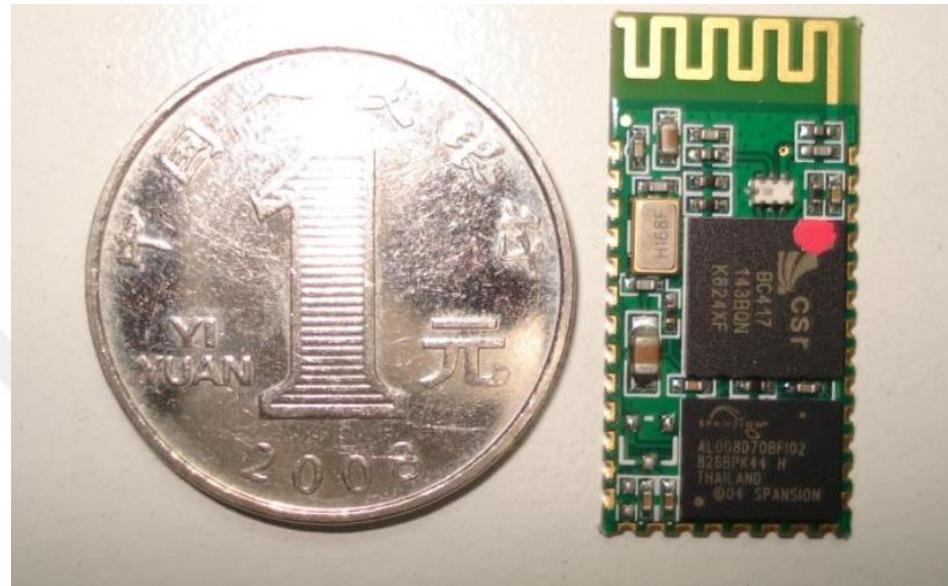

| <b>Figure 3.24</b>  | Preferred Bluetooth Module (HC-06).....                           | 67 |

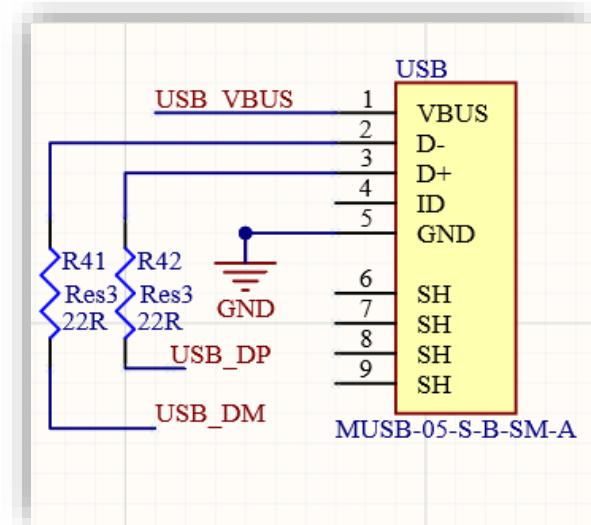

| <b>Figure 3.25</b>  | USB Full-speed Interface Circuit .....                            | 67 |

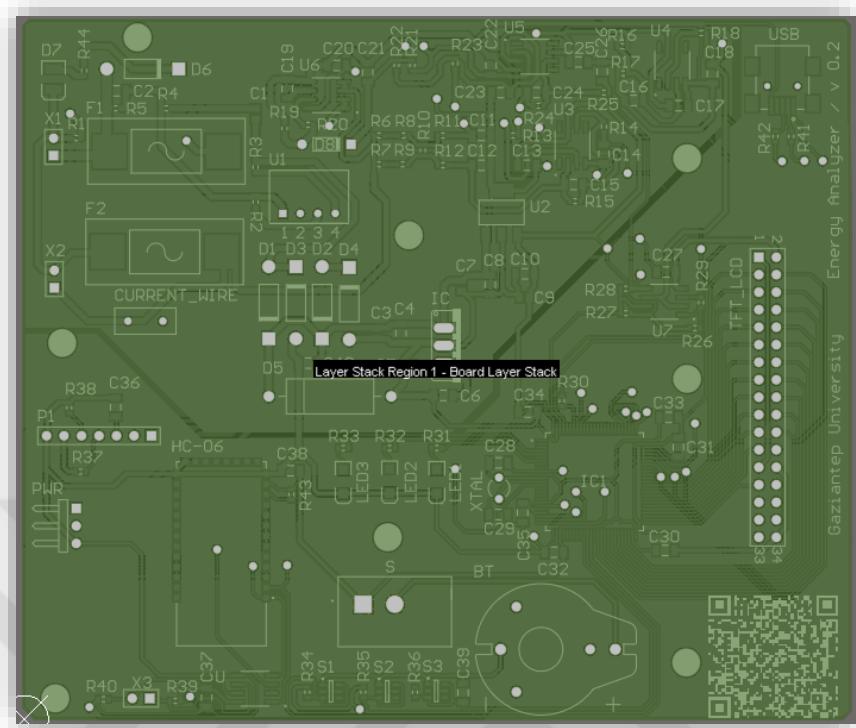

| <b>Figure 3.26</b>  | Designed PCB, Board Layer Stack Front view v.0.2 .....            | 68 |

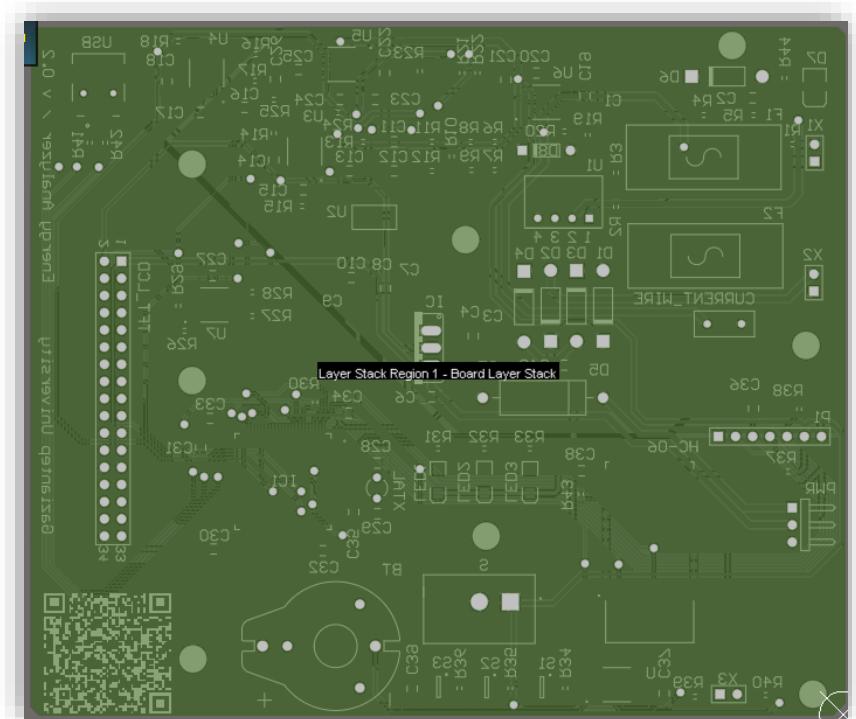

| <b>Figure 3.27</b>  | Designed PCB, Board Layer Stack Rear view v.0.2 .....             | 68 |

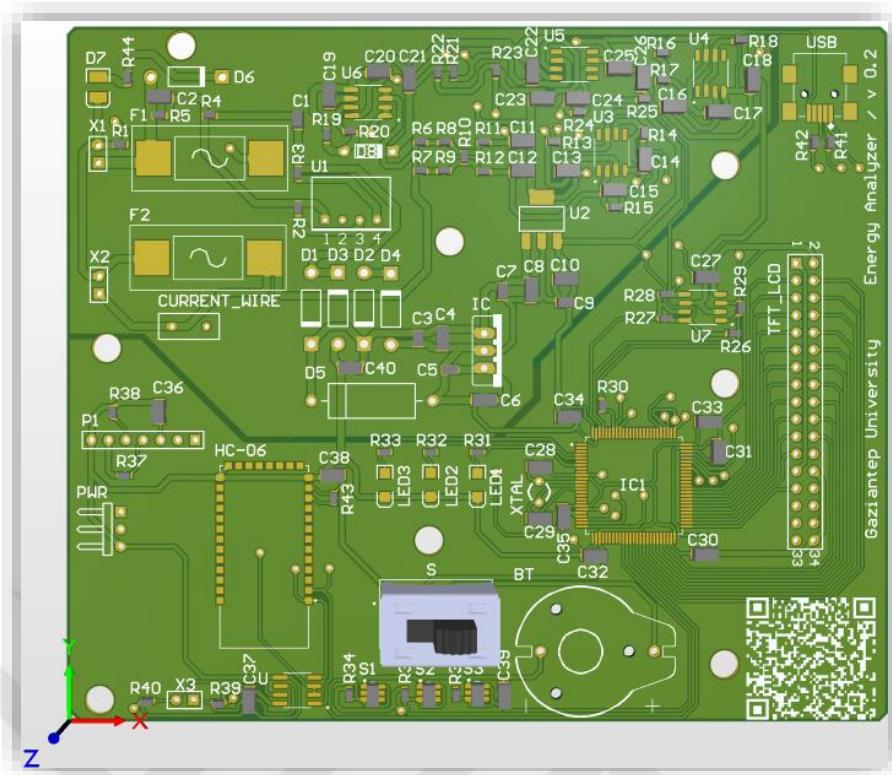

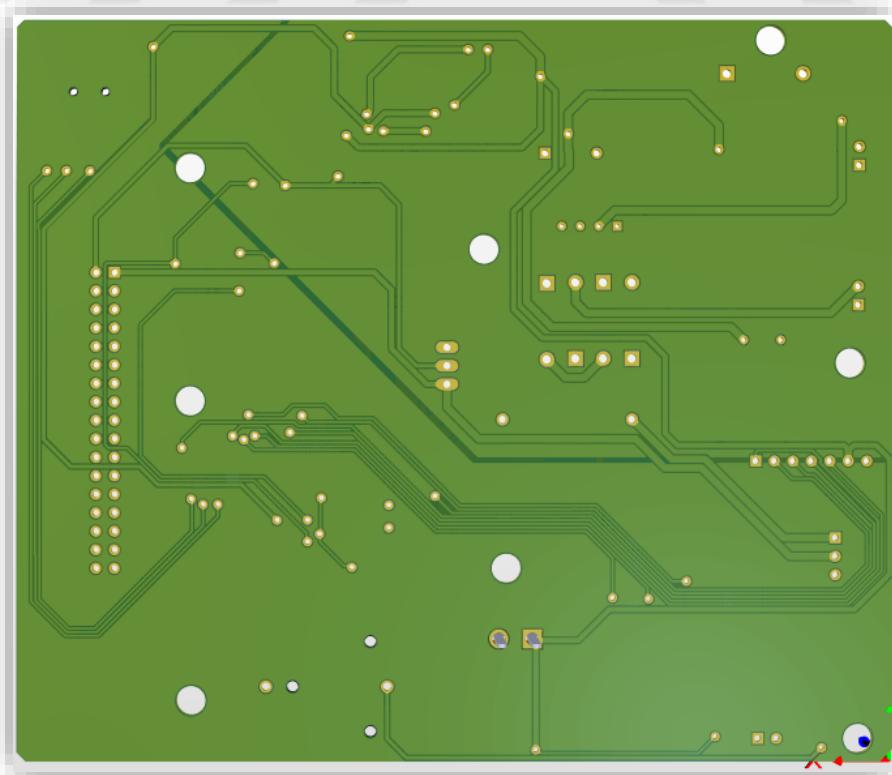

| <b>Figure 3.28</b>  | Designed PCB, 3D Front view v.0.2 .....                           | 69 |

| <b>Figure 3.29</b>  | Designed PCB, 3D Front view v.0.2 .....                           | 69 |

| <b>Figure 4.1</b>   | Message Queue Structure .....                                     | 70 |

| <b>Figure 4.2</b>   | AppWizard by SEGGER and GUI Builder by NXP .....                  | 74 |

| <b>Figure 4.3</b>   | emWin Bitmap Converter tool by SEGGER. ....                       | 74 |

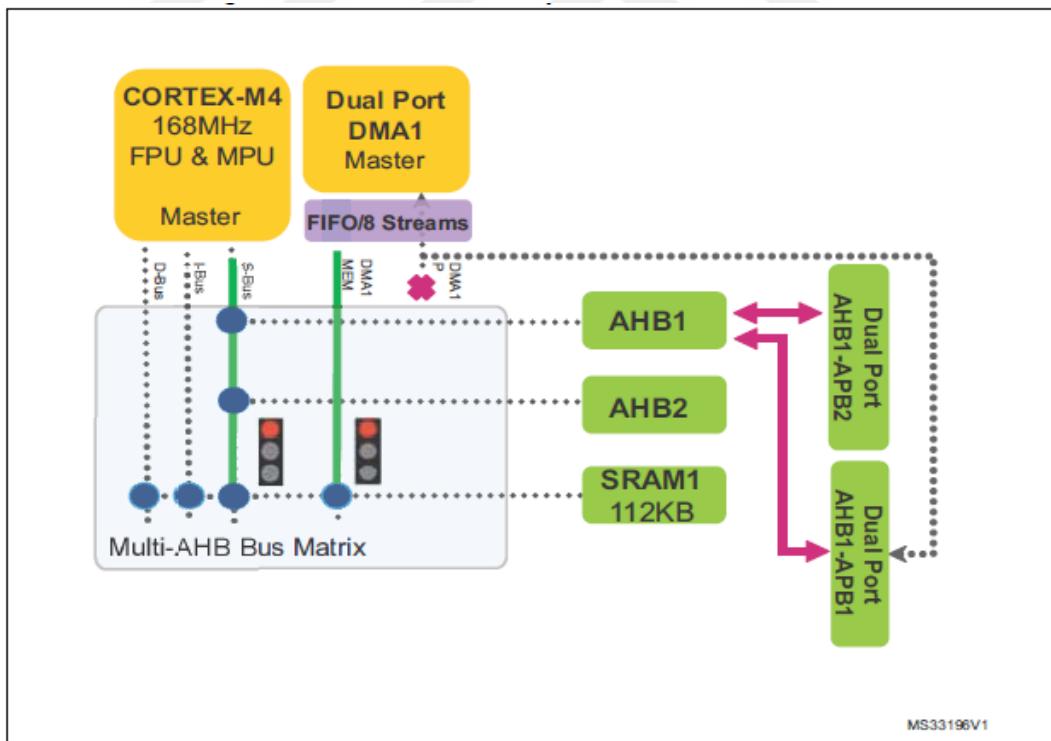

| <b>Figure 4.4</b>   | STM-32F405 DMA Structure.....                                     | 76 |

| <b>Figure 4.5</b>   | CPU and DMA1 request an access to SRAM1.....                      | 76 |

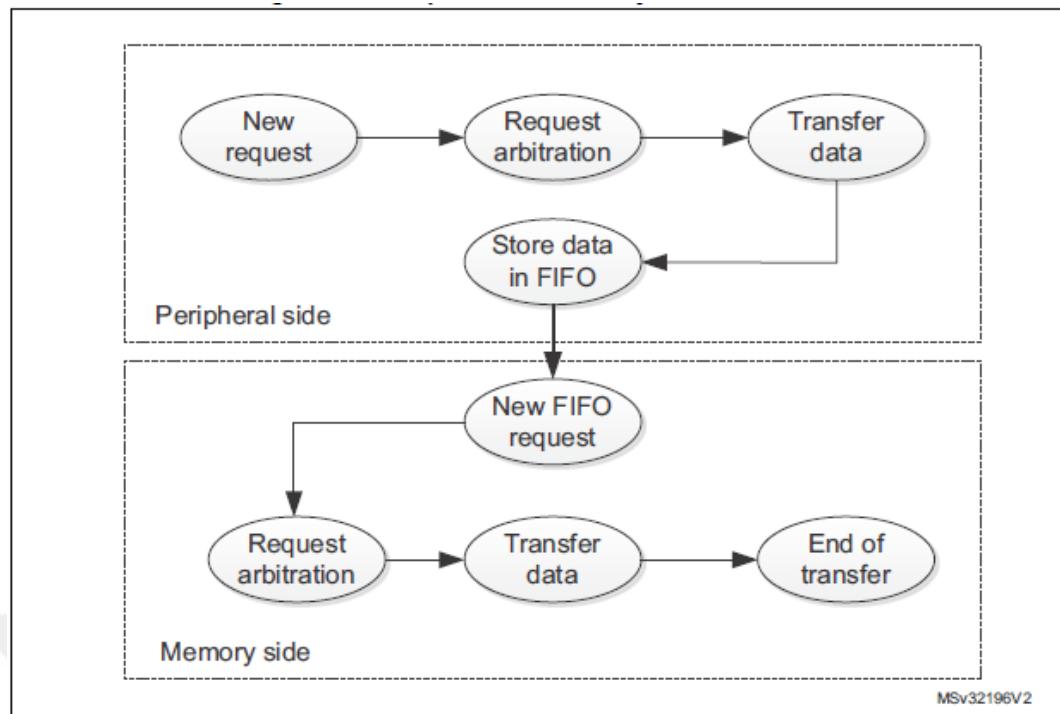

| <b>Figure 4.6</b>   | Peripheral-to-memory transfer states.....                         | 77 |

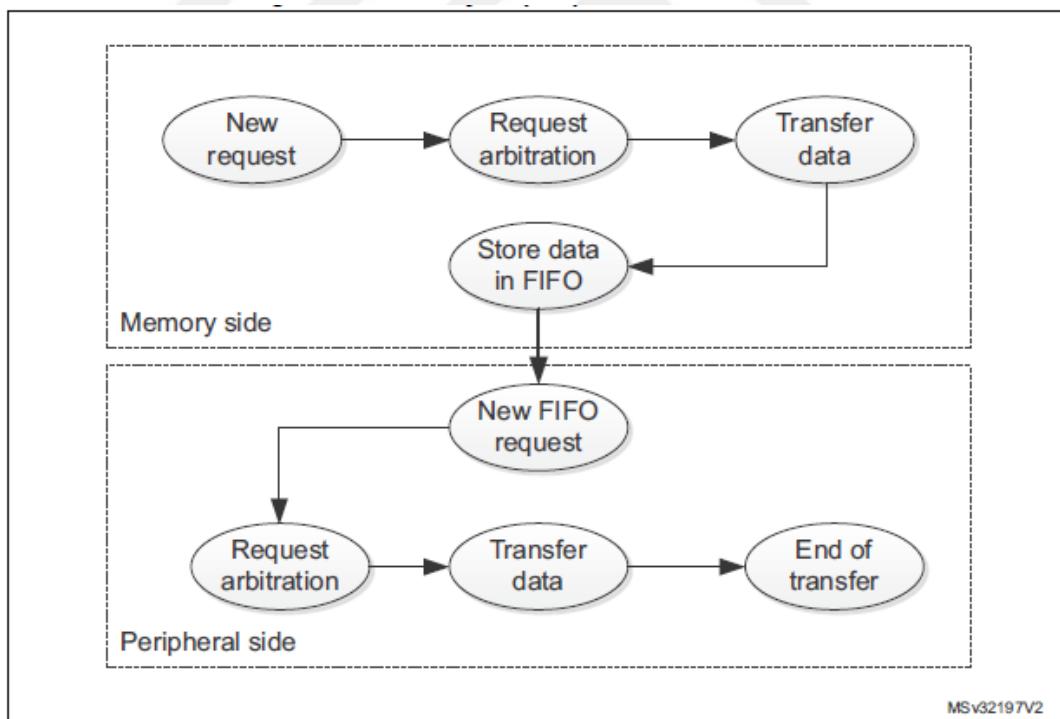

| <b>Figure 4.7</b>   | Memory-to-peripheral transfer states.....                         | 77 |

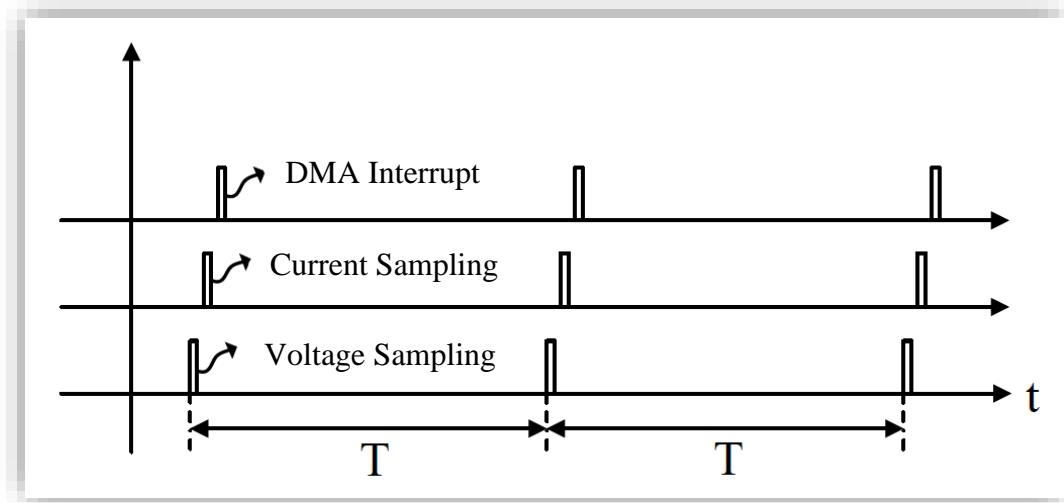

| <b>Figure 4.8</b>   | Timing diagram for sampling .....                                 | 78 |

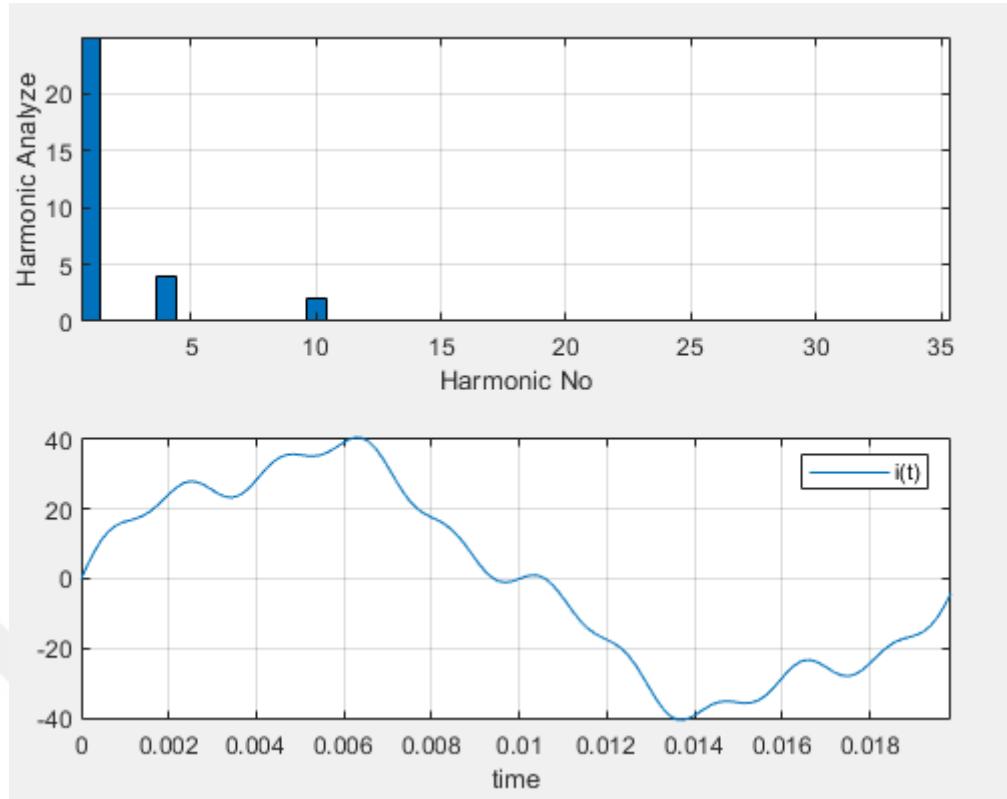

| <b>Figure 4.9</b>   | Effective values of the Current Harmonics.....                    | 82 |

|                    |                                                                                            |    |

|--------------------|--------------------------------------------------------------------------------------------|----|

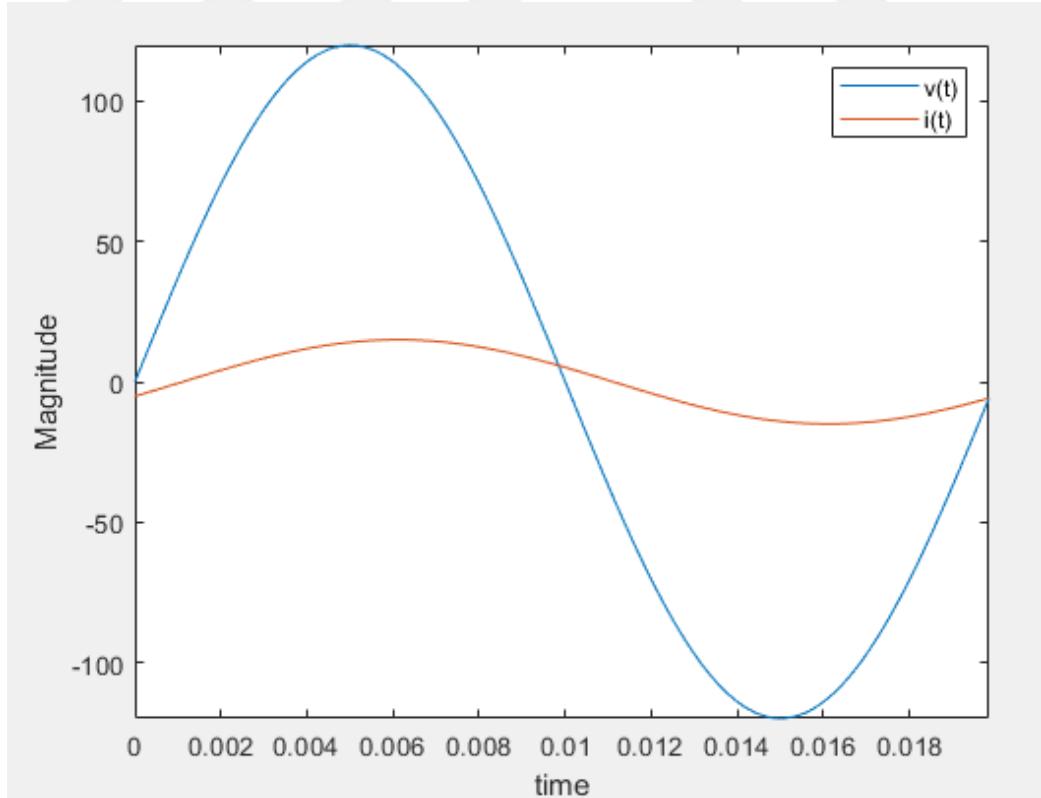

| <b>Figure 4.10</b> | Voltage and current signal to be calculated phase difference.....                          | 83 |

| <b>Figure 4.11</b> | MATLAB output of $\text{Cos } \varphi$ calculation for a harmonic-free system              | 84 |

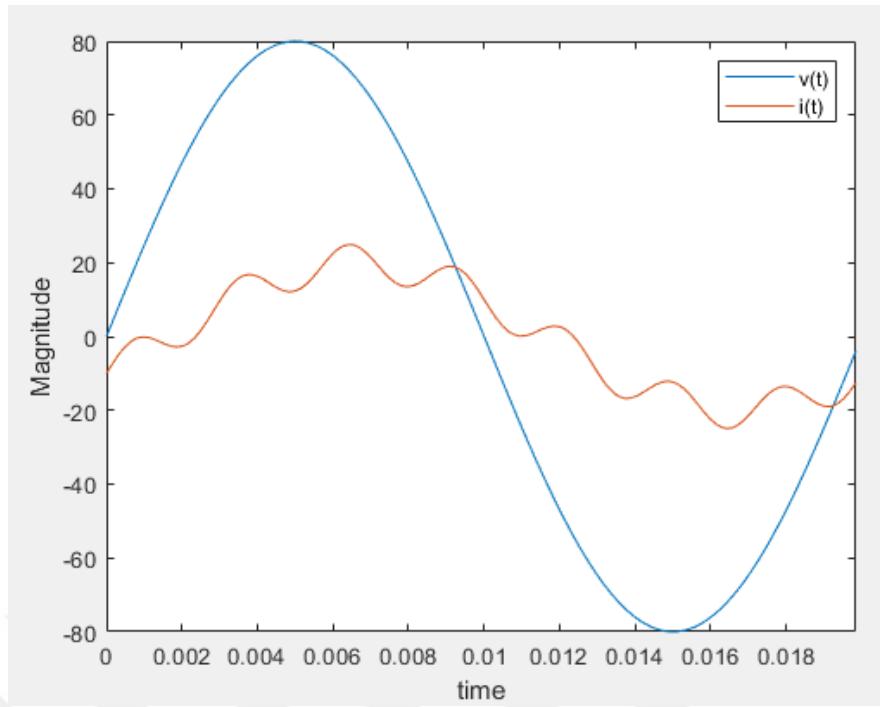

| <b>Figure 4.12</b> | Voltage and harmonic current signal to be calculated phase difference                      | 85 |

| <b>Figure 4.13</b> | MATLAB output of $\text{cos}\varphi$ calculation for a harmonic system .....               | 85 |

| <b>Figure 4.14</b> | Power factor calculation on MATLAB for a harmonic system.....                              | 87 |

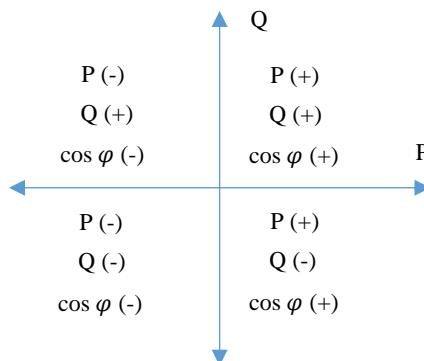

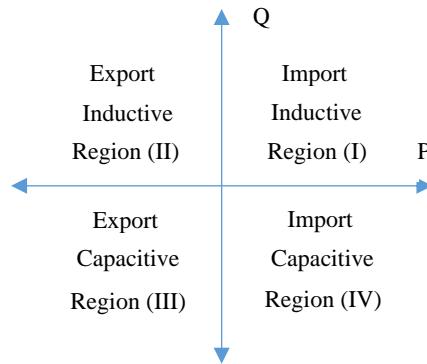

| <b>Figure 4.15</b> | State of powers according to the sign of the phase angle .....                             | 89 |

| <b>Figure 4.16</b> | Energy flow direction according to the state of forces .....                               | 88 |

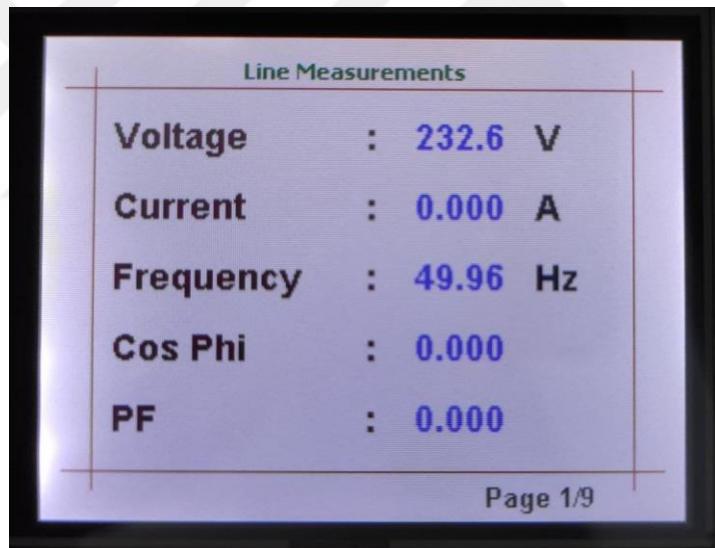

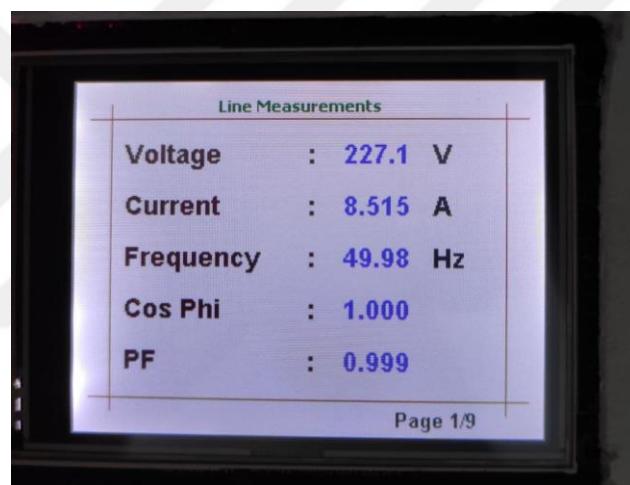

| <b>Figure 5.1</b>  | Voltage, Current, frequency, $\text{Cos } \varphi$ and PF analyze screen without the load  | 91 |

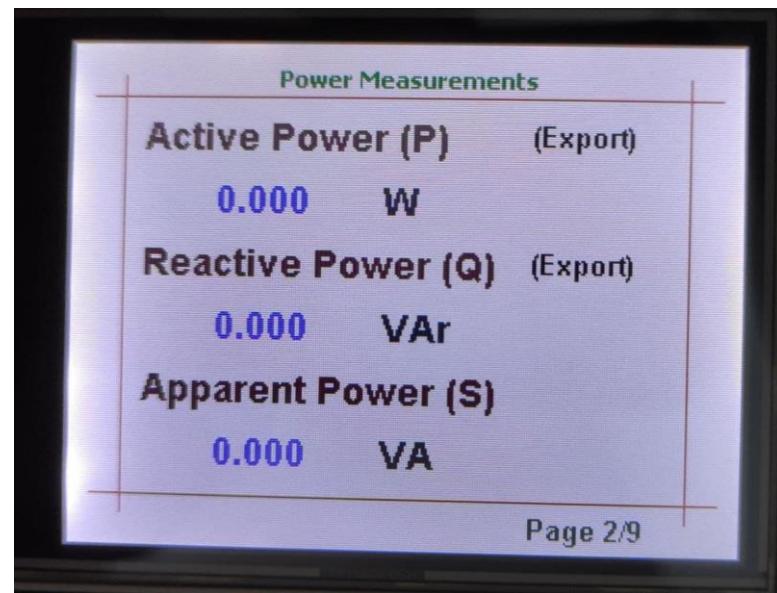

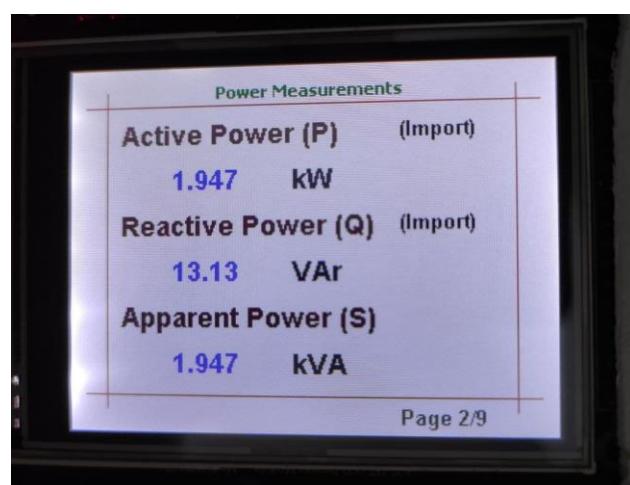

| <b>Figure 5.2</b>  | Active, Reactive and Apparent Power Analyze Screen without the load                        | 92 |

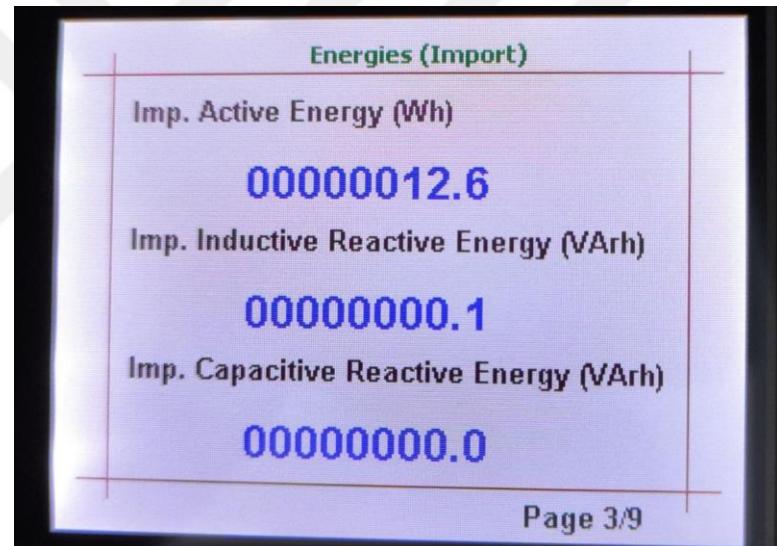

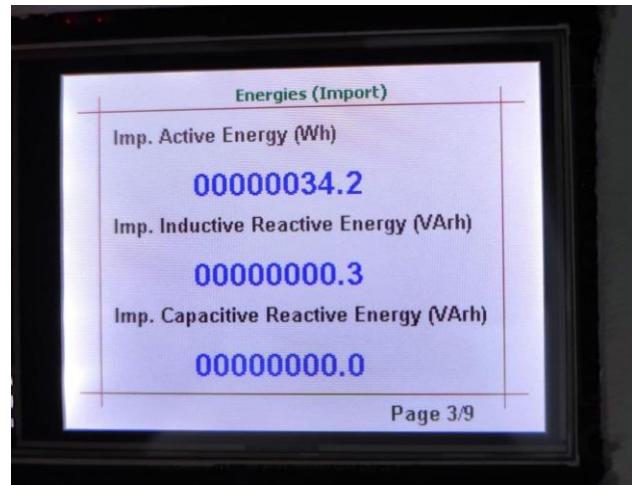

| <b>Figure 5.3</b>  | Imported Active, Inductive and Reactive Energy Analyze Screen without the load.....        | 92 |

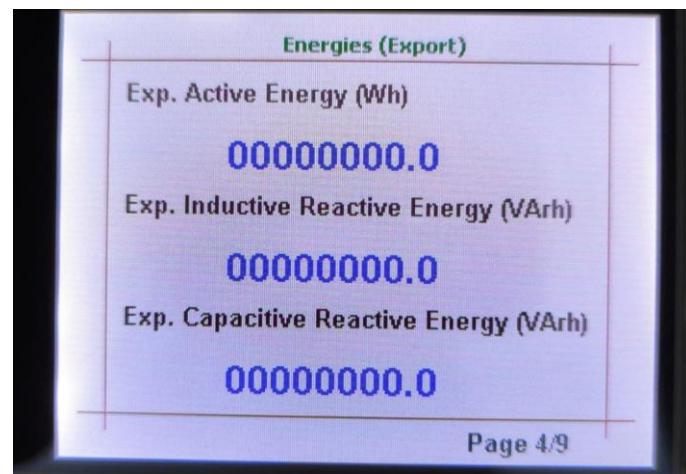

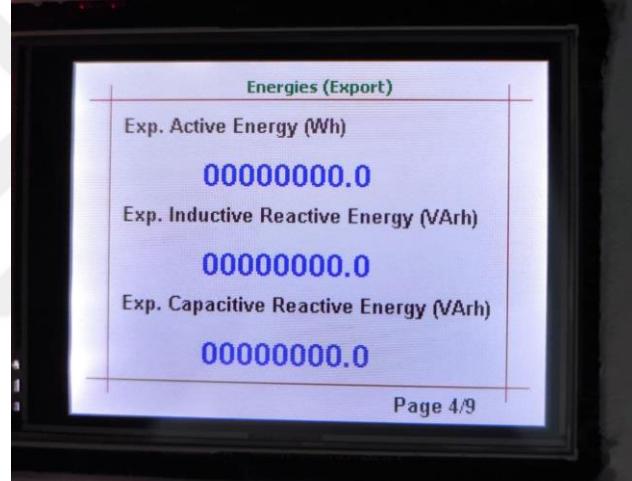

| <b>Figure 5.4</b>  | Exported Active, Inductive and Reactive Energy Analyze Screen without the load.....        | 93 |

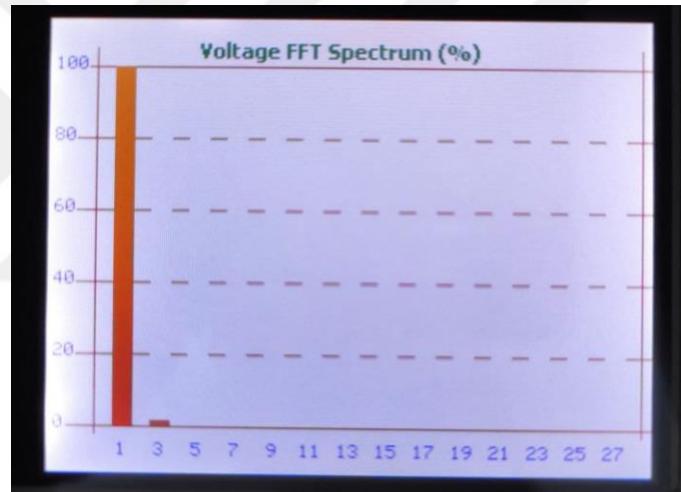

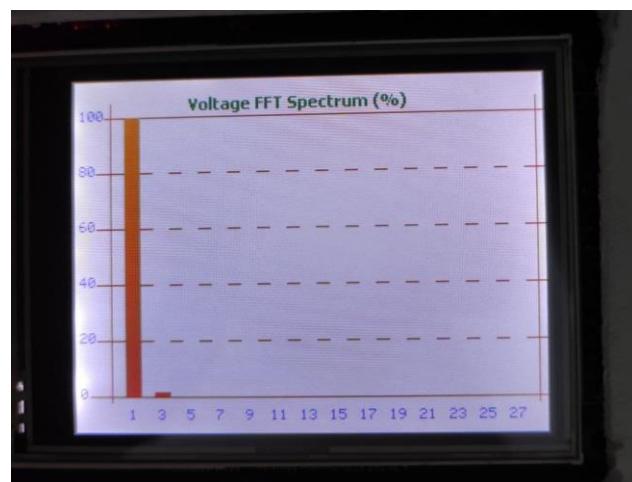

| <b>Figure 5.5</b>  | Voltage Harmonical Spectrum Graphical Analyze Screen without the load                      | 93 |

| <b>Figure 5.6</b>  | Voltage Harmonic Ratios Analyzed Values without the load .....                             | 94 |

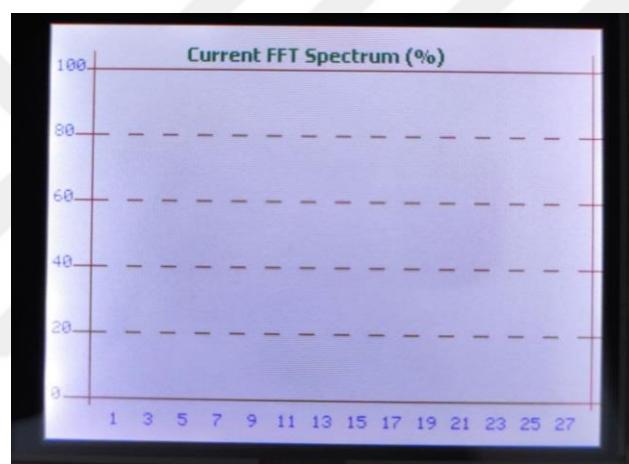

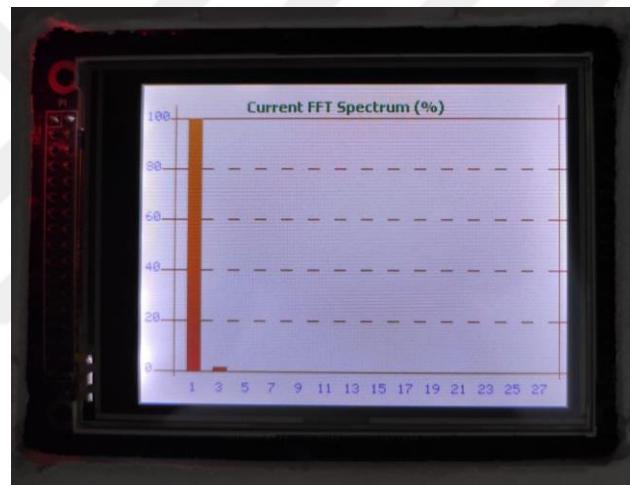

| <b>Figure 5.7</b>  | Current Harmonical Spectrum Graphical Analyze Screen without the load                      | 94 |

| <b>Figure 5.8</b>  | Current Harmonic Ratios Analyzed Values without the load.....                              | 94 |

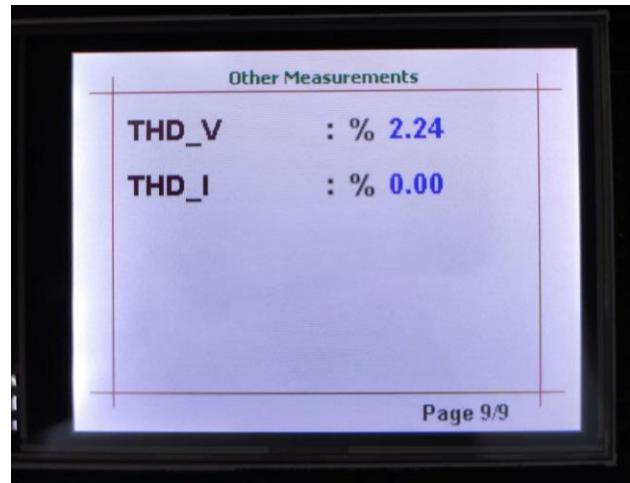

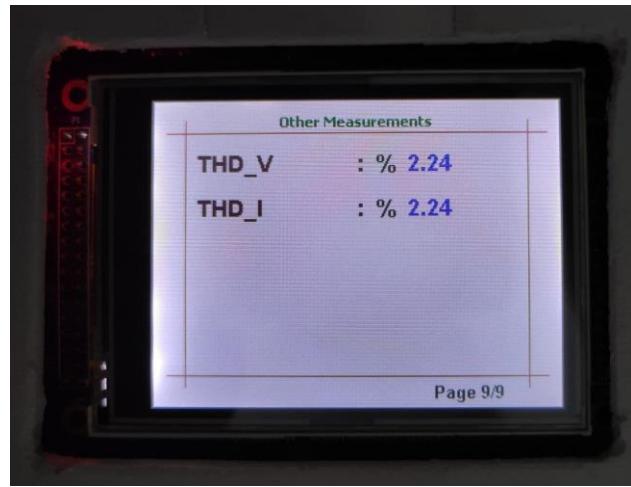

| <b>Figure 5.9</b>  | Total Harmonic Distortion on the Voltage and Current Analyze Screen without the load.....  | 95 |

| <b>Figure 5.10</b> | Voltage, Current, frequency, $\text{Cos } \varphi$ and PF analyze screen on the load ..... | 95 |

| <b>Figure 5.11</b> | Active, Reactive and Apparent Power Analyze Screen on the load.                            | 95 |

| <b>Figure 5.12</b> | Imported Active, Inductive and Reactive Energy Analyze Screen on the load                  | 96 |

| <b>Figure 5.13</b> | Exported Active, Inductive and Reactive Energy Analyze Screen on the load                  | 96 |

| <b>Figure 5.14</b> | Voltage Harmonical Spectrum Graphical Analyze Screen on the load                           | 96 |

| <b>Figure 5.15</b> | Voltage Harmonic Ratios Analyzed Values on the load .....                                  | 97 |

|                    |                                                                                        |     |

|--------------------|----------------------------------------------------------------------------------------|-----|

| <b>Figure 5.16</b> | Current Harmonical Spectrum Graphical Analyze Screen on the load                       | 97  |

| <b>Figure 5.17</b> | Current Harmonic Ratios Analyzed Values on the load.....                               | 97  |

| <b>Figure 5.18</b> | Total Harmonic Distortions on the Voltage and Current Analyze Screen on the load ..... | 98  |

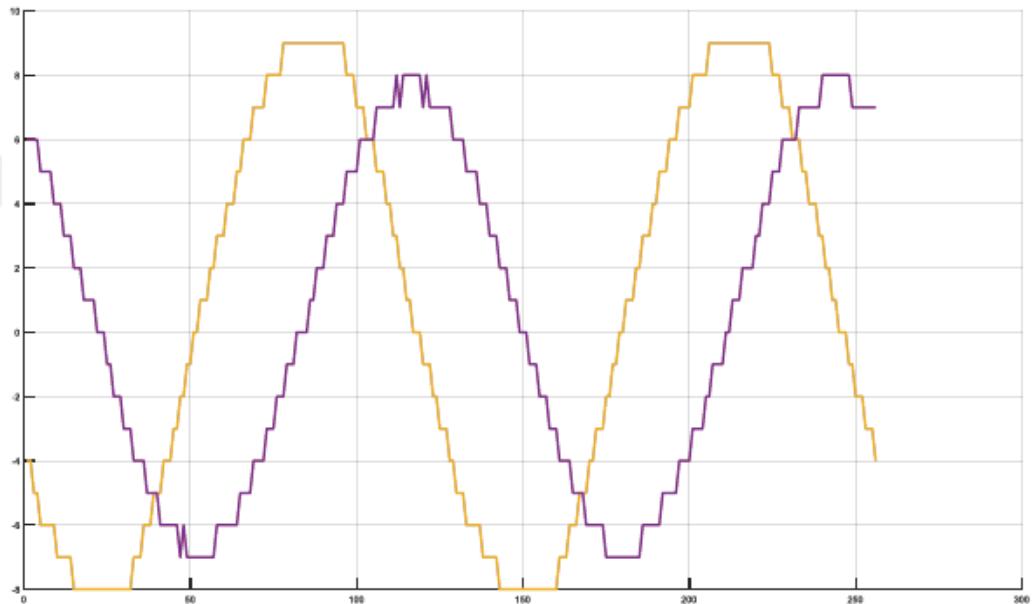

| <b>Figure 5.19</b> | Voltage and Current Graphs when the ADC has 6-bits resolution...                       | 99  |

| <b>Figure 5.20</b> | Voltage and Current Graphs when the ADC has 8-bits resolution...                       | 99  |

| <b>Figure 5.21</b> | Voltage and Current Graphs when the ADC has 10-bits resolution                         | 100 |

| <b>Figure 5.22</b> | Voltage and Current Graphs when the ADC has 12-bits resolution                         | 100 |

## LIST OF SYMBOLS

|           |                                              |

|-----------|----------------------------------------------|

| $\phi$    | Phase Difference between Voltage and Current |

| $f$       | Frequency                                    |

| $\Omega$  | Ohm                                          |

| $\pi$     | Pi                                           |

| $\omega$  | Angular Velocity                             |

| $f_c$     | Cutting Frequency                            |

| $f_s$     | Sampling Frequency                           |

| $T$       | Periodic Time                                |

| $T_s$     | Sampling Periodic Time                       |

| $\zeta$   | Damping Ratio                                |

| $K_v$     | Voltage Distortion Rate                      |

| $K_i$     | Current Distortion Rate                      |

| $P$       | Active Power                                 |

| $Q$       | Reactive Power                               |

| $S$       | Apparent Power                               |

| $THD$     | Total Harmonic Distortion                    |

| $THD_I$   | Total Harmonic Distortion in Current         |

| $THD_V$   | Total Harmonic Distortion in Voltage         |

| $V_{rms}$ | RMS Voltage                                  |

| $V_{ref}$ | Reference Voltage                            |

## LIST OF ABBREVIATIONS

|               |                                         |

|---------------|-----------------------------------------|

| <b>A/D</b>    | Analog to Digital Converter             |

| <b>AC</b>     | Alternate Current                       |

| <b>ADC</b>    | Analog to Digital Converter             |

| <b>AGND</b>   | Analog Ground                           |

| <b>APF</b>    | All-pass-filter                         |

| <b>BAM</b>    | Batch Acquisition Mode                  |

| <b>BPF</b>    | Band-Pass Filter                        |

| <b>CLK</b>    | Clock                                   |

| <b>CMOS</b>   | Complementary Metal Oxide Semiconductor |

| <b>CONVST</b> | Conversation Start                      |

| <b>CRC</b>    | Cyclic redundancy checky                |

| <b>D/A</b>    | Digital to Analog Converter             |

| <b>DAC</b>    | Digital to Analog Converter             |

| <b>DC</b>     | Direct Current                          |

| <b>DGND</b>   | Digital Ground                          |

| <b>DMA</b>    | Direct- memory Address                  |

| <b>DSP</b>    | Digital Signal Processor                |

| <b>DVMs</b>   | Digital Volt-meters                     |

| <b>FET</b>    | Field Effect Transistor                 |

| <b>FIFO</b>   | First IN First OUT                      |

| <b>FFT</b>    | Fast Fourier Transform                  |

| <b>FPU</b>    | Floating-point Unit                     |

| <b>FS</b>     | Full- Scale                             |

| <b>GUI</b>    | Graphical User Interface                |

| <b>IC</b>     | Integrated Circuit                      |

| <b>ISR</b>    | Interrupt Service Routine               |

| <b>LCD</b>    | Liquid Crystal Display                  |

|               |                                            |

|---------------|--------------------------------------------|

| <b>LPF</b>    | Low-Pass Filter                            |

| <b>LSB</b>    | Least Significant Bit                      |

| <b>MPU</b>    | Memory Protection Unit                     |

| <b>MSB</b>    | Most Significant Bit                       |

| <b>MSPS</b>   | Mega-Samples Per Second                    |

| <b>NZ</b>     | Nyquist Zone                               |

| <b>OSG</b>    | Orthogonal signal generator                |

| <b>P</b>      | Active Power- Magnitude of Complex Power   |

| <b>PCB</b>    | Printed Circuit Board                      |

| <b>PD</b>     | Phase Detect                               |

| <b>PF</b>     | Power Factor                               |

| <b>PCM</b>    | Pulse Code Modulation                      |

| <b>PGA</b>    | Programmable Gain Amplifier                |

| <b>PLL</b>    | Phase Lock Loop                            |

| <b>PWM</b>    | Pulse Width Modulation                     |

| <b>Q</b>      | Reactive Power- Magnitude of Complex Power |

| <b>RAM</b>    | Random Access Memory                       |

| <b>REFIN</b>  | Reference Input                            |

| <b>REFOUT</b> | Reference Output                           |

| <b>RD</b>     | Read                                       |

| <b>RMS</b>    | Root Mean Square                           |

| <b>RNG</b>    | Random number generator                    |

| <b>RTC</b>    | Real-time Clock                            |

| <b>RTD</b>    | Resistive Temperature Detector             |

| <b>RTOS</b>   | Real-Time Operating System                 |

| <b>S</b>      | Apparent Power- Magnitude of Complex Power |

| <b>SRAM</b>   | Static Random-Access Memory                |

| <b>SAR</b>    | Successive Approximation                   |

| <b>SFDR</b>   | Spurious-Free Dynamic Range                |

| <b>SHA</b>    | Sample and Hold Amplifier                  |

| <b>SNR</b>    | Signal to Noise Ratio                      |

| <b>SOGI</b>   | Second-order generalized integrator        |

| <b>SPI</b>    | Serial Peripheral Interface                |

|              |                                                         |

|--------------|---------------------------------------------------------|

| <b>T/H</b>   | Track and Hold                                          |

| <b>TF</b>    | Transfer Function                                       |

| <b>TFT</b>   | Thin Film Transistor                                    |

| <b>THD</b>   | Total Harmonic Distortion                               |

| <b>USART</b> | Universal Synchronous Asynchronous Receiver Transmitter |

| <b>VCO</b>   | Voltage-Controlled Oscillator                           |

| <b>WE</b>    | Windowing Effect                                        |

| <b>WRT</b>   | Write                                                   |

# CHAPTER I

## INTRODUCTION

### 1.1. Literature Summary

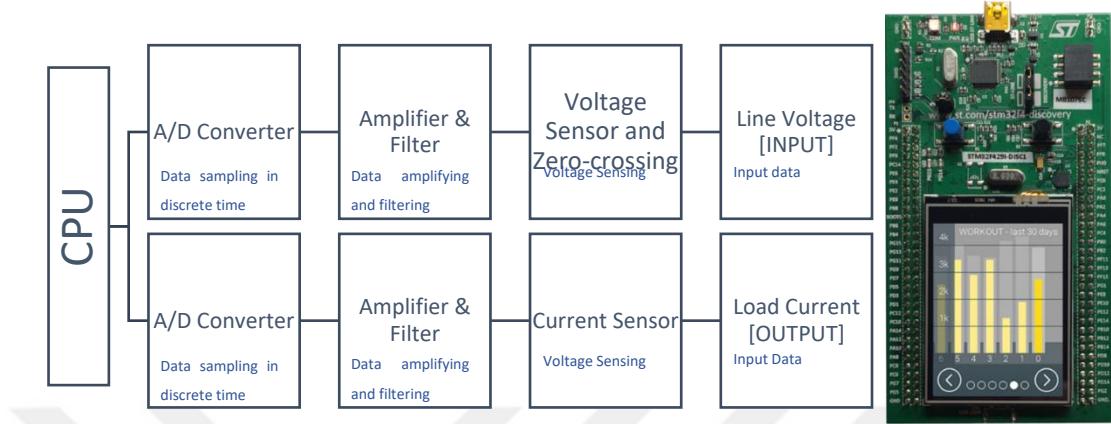

The measurement in electrical systems is generally a numerical expression of an electrical quantity. There are lots of data in the electrical networks. In alternative current systems, generally voltage, current, frequency, phase difference, power factor, active power, reactive power and energy values are numerically measured values. In the common systems for monitoring power circuits, we require to install individual measuring devices e.g., Voltmeter, Ammeter, Oscilloscope, Wattmeter etc. separately because of the increasing harmonic currents and voltages in the grids. Our design yields an industrial analyzer that sense the current and voltage at the input terminals then designed special circuit transmits signals proportional levels to the MCU which will be analyzed based on some standards such as IEEE Std 1459TM-2010 [1]. A 12-bit A/D converter, converts the voltage and current signals to the digital representation at regular intervals. MCU periodically samples ( $f_{sampling}=1600$  Hz,  $N=32$ , A/D resolution 12-bit) then analyze the voltage and current signals at regular intervals of time with the approximately 0,4 % error rate. (The error rate depends on the  $f_{sampling}$ ,  $N$ , and A/D resolution.) After that, stores the data of electrical variables which is analyzed. e.g., these electrical variables may be frequency, true RMS volts, true RMS amps,  $\cos(\phi)$  and even harmonic values, including energy variables. For the project ARM Cortex family as STM-32F405 and LCD-TFT screen which part number is HY-32D are one of the most important components. The features of this device completely provide our requirements with isolation circuits, fuses and another safety equipment for our PCB. As a summary, it is an objective of the thesis to develop an industrial analyzer which a single analyzer device that analyzes the variable parameters in a grid by eliminating the require of multiple measuring devices. Thanks

to the LCD, we are able to see all data only in a screen and it's completely mobilized. You can see block diagram of the analyzer in Figure (1.1).

**Figure 1.1** Equivalent system block diagram for an energy analyzer

### 1.1.1 Effective Value in AC Systems

Voltage and current magnitudes change according to time and have a certain amplitude and frequency. For this reason, it is usually expressed with its effective values. Effective value is a type of value that enables the expression of equivalent equivalents of magnitudes in alternating current systems in direct current systems. It can be expressed as the equivalent of AC voltage required to obtain the amount of heat energy generated in a resistance under a DC voltage [2].

The effective value can be represented as the RMS (Root Mean Square) value consisting of the effective value or the initials of its English equivalent. The active power expended on a load is obtained by equation (1.2) in alternating and direct current systems [2]. According to this equation, the effective value can be expressed as the square root of the mean of the square of the voltage (or current), the integral over a period. In digital systems, the sum of the squares of instantaneous samples of the signal is averaged. The square root of this value is calculated and therefore the effective value is found.

$$P = \frac{V^2}{R} \quad (1.1)$$

$$\frac{v_{dc}^2}{R} = \frac{1}{T} \cdot \int_0^T \frac{v(t)^2}{R} \cdot dt \quad (1.2)$$

$$V_{rms} = \sqrt{\frac{1}{T} \cdot \int_0^T v(t)^2 \cdot dt} \quad (1.3)$$

The effective (effective) value of the grid voltage in sine form can be written as in (1.5) equation.

$$v(t) = v_m \cdot \sin(\omega t) \quad (1.4)$$

$$v_{rms} = \sqrt{\frac{1}{T} \cdot \int_0^T \{v_m \cdot \sin(\omega t)\}^2 \cdot dt} \quad (1.5)$$

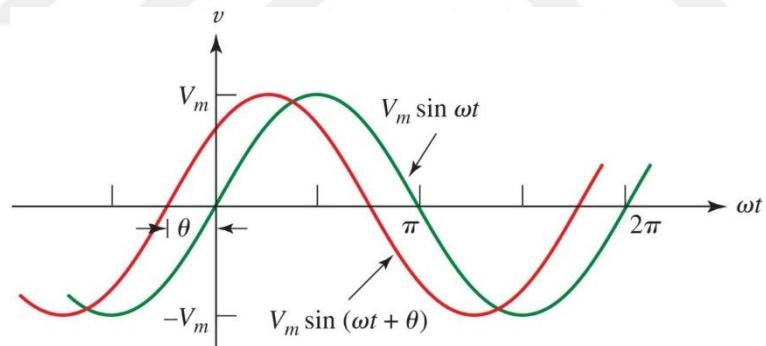

- The wave in red is said to *lead* the wave in green by  $\theta$ .

- The wave in green  $\sin(\omega t)$  is said to *lag* the wave in red by  $\theta$ .

- The units of  $\theta$  and  $\omega t$  must be consistent when computing the sine function.

**Figure 1.2** Value of the grid voltage in sine form

The effective value of the network voltage in the sine form in the range of  $[0, 2\pi]$  can be mathematically calculated by equation (1.6) where  $v_m$  as the peak value.

$$v_{rms} = \sqrt{\frac{1}{T} \cdot \int_0^T [v_m \cdot \sin(\omega t)]^2 \cdot dt} \quad (1.6)$$

$$v_{rms} = \frac{v_m}{\sqrt{2}} \quad (1.7)$$

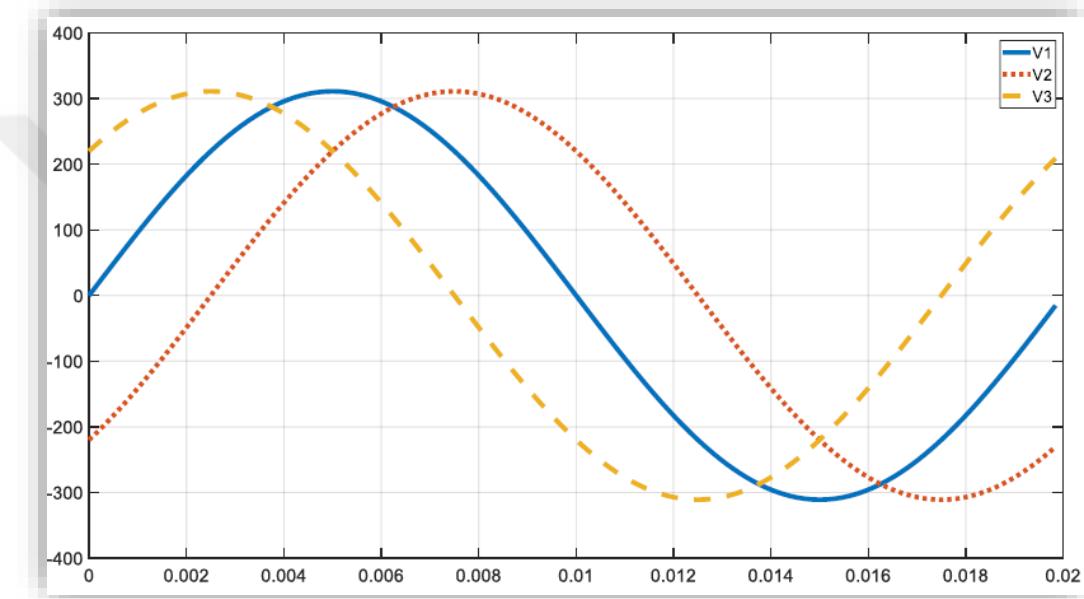

### 1.1.2 Phase Difference Between AC Voltage and AC Current

Inductance and capacitors in AC systems cause phase difference between voltage and current [3]. If we take the V1 signal as reference in Figure (1.3), the V2 signal is in reverse phase according to the V1 signal, and the V3 signal is in forward phase according to the V1 signal. Even if the amplitudes are not equal, the frequencies must be equal in order to be able to talk about the phase difference. If there is a DC component on the signal, this component can be reset and the phase difference can be checked [3].

**Figure 1.3** Sinusoidal signals that has the phase difference

If the load is pure ohmic, there is no phase difference between voltage and current [3]. In case of inductive load, the current is in phase back from the voltage, in case of capacitive load the voltage is in phase back from the current.

This phase difference between voltage and current is denoted by " $\varphi$ " and is called the phase angle. Since the phase angle close to zero is the most ideal situation for the network, the reactive power in the systems is compensated and the phase difference between the current drawn from the network and the voltage is tried to be reset. In this case, the reactive power required by the system is supplied from the compensation panel installed in the operation.

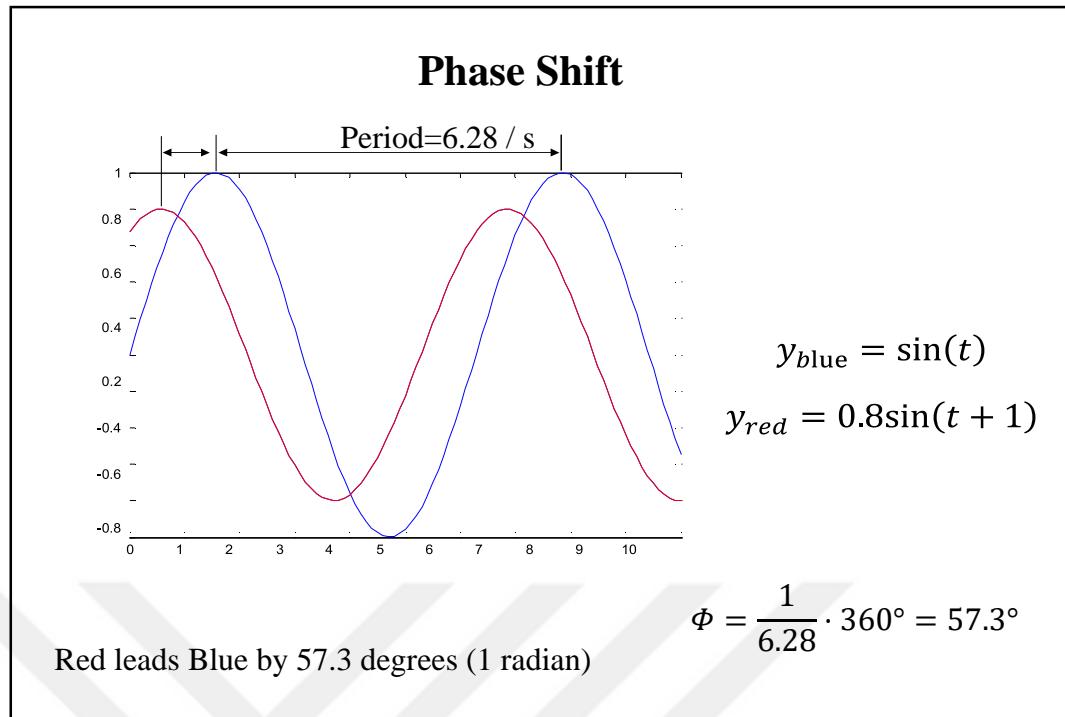

Current and voltage signals with a phase difference of  $57.3^\circ$  is shown in Figure (1.4).

**Figure 1.4** Sinusoidal signals that has phase difference

### 1.1.3 Power Calculation in AC Systems

Active power (P) in AC systems is defined as useful and usable power. Reactive power (Q) is defined as the power that does not work actively but is withdrawn from the network and then transferred back to the network. Apparent power (S) is the total resultant power formed by active and reactive power components. If the system has a pure ohmic load, there will be no phase difference between the current and voltage, so there will be no reactive power. Therefore, the active power value will be equal to the apparent power value. If there is a reactive power in the system, the apparent power will be equal to the combination of active and reactive powers.

$$S^2 = P^2 + Q^2 \quad (1.8)$$

$$P = S \cdot \cos \varphi \quad (1.9)$$

$$Q = S \cdot \sin \varphi \quad (1.10)$$

**Figure 1.5** Power Triangle, Relationship between Power factors

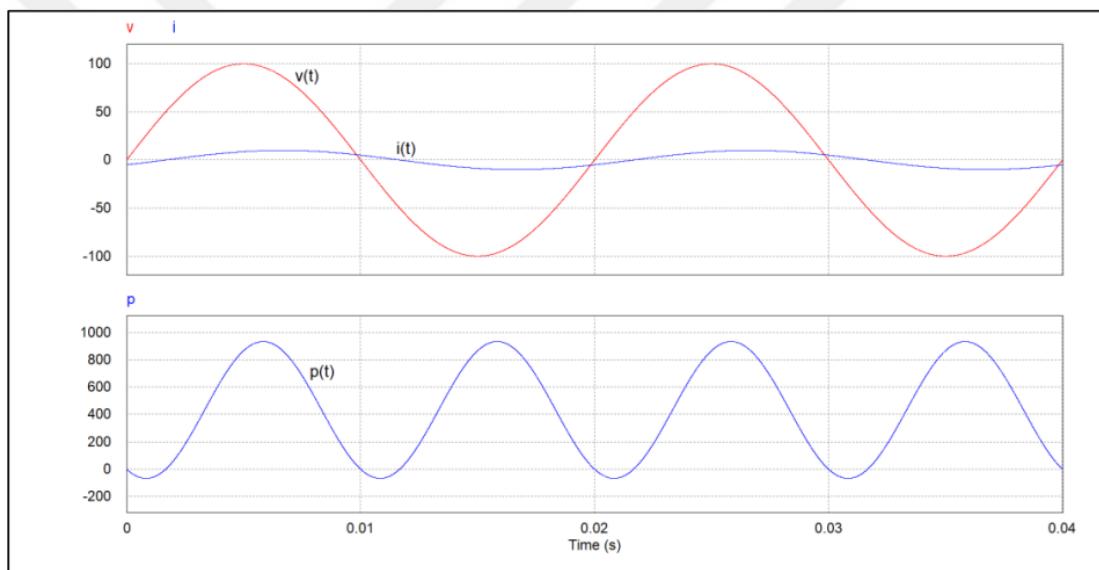

Instantaneous power value is obtained by multiplying the instantaneous values of the voltage and current components [3]. Instantaneous power value changes with twice the system frequency.

**Figure 1.6** Instantaneous voltage, current and power values

In electrical systems, instantaneous power is expressed by equation (1.10), where  $v(t)$  and  $i(t)$  are instantaneous values of voltage and current.

$$P(t) = v(t) \cdot i(t) \quad (1.11)$$

Devices that measure electrical power measure the average value of power [3]. In this case, if the instantaneous power expression is integrated over a period, the expression (1.13) can be written for the average power value (active power).

$$v(t) = v_m \cdot \sin(\omega t) \quad (1.12)$$

$$i(t) = i_m \cdot \sin(\omega t - \varphi) \quad (1.13)$$

$$P = \frac{1}{2\pi} \cdot \int_0^{2\pi} [v_m \cdot I_m \cdot \sin(\omega t) \cdot \sin(\omega t - \varphi)] \cdot d\omega t \quad (1.14)$$

$$P = v_{rms} \cdot I_{rms} \cdot \cos(\varphi) \quad (1.15)$$

The reactive power value can be calculated by the product of the voltage component and the  $90^\circ$  phase-shifted state of the current component or by the product of the current component and the  $90^\circ$  phase-shifted state of the voltage component. If the  $90^\circ$  phase shifted state of the current signal is expressed as  $I_q$ , the expression (1.17) can be written for the reactive power.

$$v(t) = v_m \cdot \sin(\omega t) \quad (1.16)$$

$$I_q(t) = i_m \cdot \sin\left(\omega t - \varphi + \frac{\pi}{2}\right) = i_m \cdot \cos(\omega t - \varphi) \quad (1.17)$$

$$Q = \frac{1}{2\pi} \cdot \int_0^{2\pi} [v_m \cdot I_m \cdot \sin(\omega t) \cdot \cos(\omega t - \varphi)] \cdot d\omega t \quad (1.18)$$

$$Q = v_{rms} \cdot I_{rms} \cdot \sin(\varphi) \quad (1.19)$$

As a summary power equation is follows,

$$\text{Active Power} \rightarrow P = v_{rms} \cdot I_{rms} \cdot \cos(\varphi) \quad (\text{Watt})$$

$$\text{Reactive Power} \rightarrow Q = v_{rms} \cdot I_{rms} \cdot \sin(\varphi) \quad (\text{Var})$$

$$\text{Apparent Power} \rightarrow S = v_{rms} \cdot I_{rms} \quad (\text{VA})$$

In digital systems, it is possible to calculate the phase difference and power values based on the instantaneous values of voltage and current. In MATLAB environment, instantaneous values of current and voltage and power values can be calculated by using averaging command.

#### 1.1.4 Power Factor ( $\cos \varphi$ ) in Power Systems

In power systems, the ratio of active power to apparent power is defined as the power factor [2]. If the network voltage and current are in sinusoidal form, that is, if the system does not contain a non-linear load,  $\cos \varphi$  is equal to the power factor (PF).

$$P = v_{rms} \cdot I_{rms} \cdot \cos(\varphi) \quad (1.20)$$

$$Q = v_{rms} \cdot I_{rms} \cdot \sin(\varphi) \quad (1.21)$$

$$S = \sqrt{P^2 + Q^2} \quad (1.22)$$

$$\cos(\varphi) = PF = \frac{P}{S} \quad (1.23)$$

In addition to that, if there are non-linear loads such as rectifiers, uninterruptible power supplies, electronic ballasts in power systems, current and voltage signal shapes move away from the sinusoidal form and harmonics occur in the system.

In a harmonic system, power expressions such as the effective value of the voltage fundamental component  $v_1$  and the effective value of the current fundamental component  $i_1$  can be written as follows [5].

$$S_1 = \sqrt{P_1^2 + Q_1^2} \quad (1.24)$$

$$P_1 = v_1 \cdot I_1 \cdot \cos(\varphi) \quad (1.25)$$

$$Q_1 = v_1 \cdot I_1 \cdot \sin(\varphi) \quad (1.26)$$

$$PF = \frac{v_1}{v_{rms}} \cdot \frac{i_1}{i_{rms}} \cdot \cos \varphi \quad (1.27)$$

$$PF = K_{v\_distortion} \cdot K_{i\_distortion} \cdot \cos(\varphi) \quad (1.28)$$

In equation (1.28),  $K_{distortion}$  coefficients are defined as distortion factors for current and voltage, and  $\cos \varphi$  is defined as the displacement factor. If it is assumed that there is no harmonic in the network voltage, the  $K_{v\_distortion}$  coefficient will have no effect and the power factor value will be as in equation (1.40) [5].

$$PF = 1 \cdot K_{i\_distortion} \cdot \cos(\varphi) = K_{i\_distortion} \cdot \cos(\varphi) \quad (1.29)$$

**Figure 1.7** A current signal with the 5th harmonic in it

### 1.1.5 Harmonic Distortion

In electrical power systems containing harmonics, the effective values of current and voltage can be expressed in the following equations.

$$v_{rms} = \sqrt{v_1^2 + v_2^2 + v_3^2 + \dots + v_n^2} \quad (1.30)$$

$$v_{rms} = \sqrt{v_1^2 + \sum_{h=2}^n v_h^2} \quad (1.31)$$

$$i_{rms} = \sqrt{i_1^2 + i_2^2 + i_3^2 + \dots + i_n^2} \quad (1.32)$$

$$i_{rms} = \sqrt{i_1^2 + \sum_{h=2}^n i_h^2} \quad (1.33)$$

Total harmonic distortion value can be defined as the ratio of harmonic components to fundamental components. This value can be written separately for current and voltage.

$$THD_v = \frac{\sqrt{v_2^2 + v_3^2 + \dots + v_n^2}}{v_1} \quad (1.34)$$

$$THD_i = \frac{\sqrt{i_2^2 + i_3^2 + \dots + i_n^2}}{i_1} \quad (1.35)$$

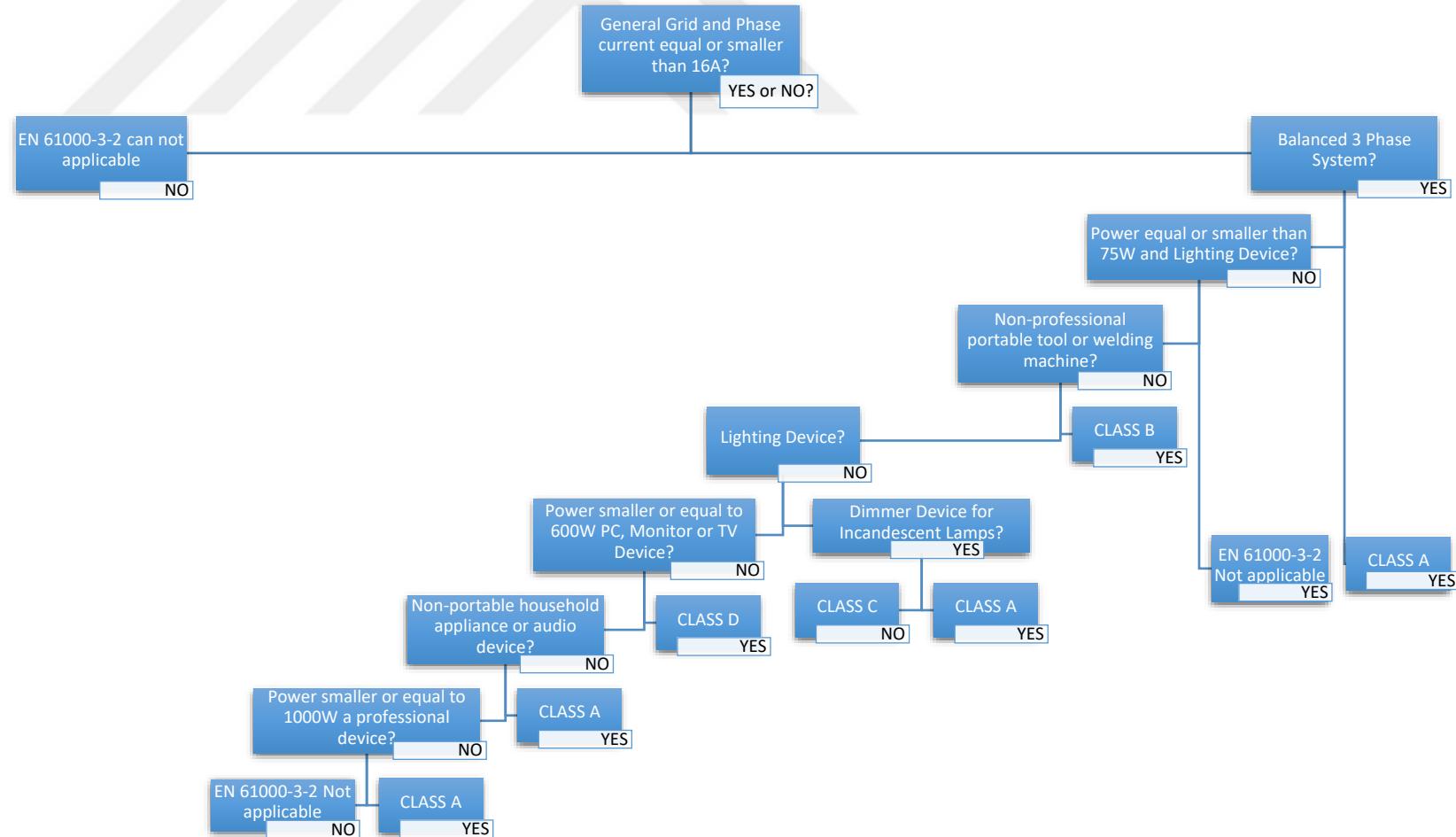

International standards such as IEEE 519 and IEC 61000 regarding energy quality have been put forward. The EN 61000 - 3 - 2 standard offered by IEC is implemented in our country as TS EN 61000 - 3 - 2: 2015, which was updated in 2015. Electrical devices are classified according to these standards and voltage and current harmonic limits are specified. Classification of devices below 16A per phase according to this standard is shown in Table (1.1). In addition, the flow chart for determining the classes in the EN 61000-3-2 standard is included in Figure (1.11). In addition, harmonic limits of these classes are given in Table (1.2), and voltage distortion limits according to IEEE 519 - 1992 standard are given in Table 1.3. [4]

**Table 1.1** Electrical device classification according to EN 61000 - 3 - 2 standard

| Class    | Definition                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| <b>A</b> | Balanced three-phase loaded devices, professional devices in the range of 75 - 1000W, electrical devices not defined in B / C / D classes |

| <b>B</b> | Non-professional portable electrical devices that consume 75W and above, non-professional welding devices                                 |

| <b>C</b> | Lighting devices below 1000W                                                                                                              |

| <b>D</b> | Computers, monitors, televisions and radio equipment in the 75W-600W range                                                                |

**Figure 1.8** Flow chart to apply standard EN 61000 - 3 -2

**Table 1.2** Harmonic limits according to EN 61000 - 3 - 2 standards

| Harmonic No.                   | Class A<br>(A) | Class B<br>(A) | Class C<br>( $I_n/I_1$ ) (%) | Class D<br>(mA/W) |

|--------------------------------|----------------|----------------|------------------------------|-------------------|

| <b>Odd numbered Harmonics</b>  |                |                |                              |                   |

| <b>3</b>                       | 2,30           | 3,45           | 30                           | 3,4               |

| <b>5</b>                       | 1,13           | 1,71           | 10                           | 1,9               |

| <b>7</b>                       | 0,77           | 1,155          | 7                            | 1,0               |

| <b>9</b>                       | 0,40           | 0,60           | 5                            | 0,5               |

| <b>11</b>                      | 0,33           | 0,495          | 3                            | 0,35              |

| <b>13</b>                      | 0,21           | 0,315          | 3                            | 0,3               |

| <b>15</b>                      | 0,15           | 0,220          | 3                            | 0,25              |

| <b>17≤h≤39</b>                 | 0,13*(15/h)    | 0,19*(15/h)    | 3                            | 3,85/n            |

| <b>Even numbered Harmonics</b> |                |                |                              |                   |

| <b>2</b>                       | 1,08           | 1,62           | 2                            | -                 |

| <b>4</b>                       | 0,43           | 0,645          | -                            | -                 |

| <b>6</b>                       | 0,30           | 0,45           | -                            | -                 |

| <b>8</b>                       | 0,23           | 0,34           | -                            | -                 |

| <b>10≤h≤40</b>                 | 0,23*(8/h)     | 0,345*(8/h)    | -                            | -                 |

**Table 1.3** Voltage distortion limits according to IEEE 519 - 1992 standard

| V                          | V <sub>n</sub> /V (%) | THD (%) |

|----------------------------|-----------------------|---------|

| <b>V ≤ 1kV</b>             | 5,0                   | 8,0     |

| <b>1kV &lt; V ≤ 69kV</b>   | 3,0                   | 5,0     |

| <b>69kV &lt; V ≤ 161kV</b> | 1,5                   | 2,5     |

| <b>161kV &lt; V</b>        | 1,0                   | 1,5     |

Apart from these standards, there are some other standards related to energy quality [5].

- ✓ EN 61000 - 3 - 3: It determines the voltage fluctuation limits in LV systems.

- ✓ EN 61000 - 3 - 4: They define harmonic limits for devices larger than 16A per phase.

- ✓ EN 50006: It determines the disruption limits caused by household and similar electrical devices containing electronic elements in the network.

- ✓ TS 9882: It determines the disruption limits caused by household and similar electrical devices in the network.

- ✓ VDE 0838: Home Appliances,

- ✓ VDE 0160: Converters,

- ✓ VDE 0712: Sets harmonic limits for fluorescent lamps and ballasts.

## 1.2 Purpose of the Thesis

The monitoring of electrical power is important to ensure that this energy resource is effectively generated, distributed and utilized. Utilities need to measure power coming out of a generation station or going into power station. In addition, to minimize power transmission losses, it's important to minimize the phase relationship between the current and voltage waveforms of the power being transmitted. In industrial control applications, it's important to be able to continuously monitor the current and phase of the power into a machine which may vary with the machine load. Traditional systems for monitoring power circuits require the installation of individual measuring devices to measure a specific power system parameter; for example, Watts, VARs, Amps, or Volts. These devices typically comprise discrete analog transducers which convert AC voltage and current signals from a power system into DC output signals proportional to the true power on the system. For example, typical utility revenue kilowatt hour meters measure power in an analog fashion. Where a data acquisition system must measure numerous circuits, requiring separate measuring devices for each circuit can add greatly to the overall cost of the system. Also, where a number of circuits are being remotely monitored for computer processing and display, the individual devices must be connected to a data acquisition device and suitably processed to interface with the computer. Further, multiple measuring devices greatly increase the overall error of the

system. Also, it is a complex system for measuring various parameters in multiple power circuits and the cost of purchasing installing and maintaining the system may be increased. Accordingly, it is a principal objective of the thesis to provide a simplified system for measuring various parameters in multiple power circuits to reduce the cost of purchasing, installing and maintaining the system. More specifically, it is an objective of the thesis to provide a system in which a single measuring device measures the fundamental parameters in a power system so that subsequent derived parameters can be computed in a controller data processing computer, thereby eliminating the necessity of multiple measuring devices. Additionally, the thesis aims to provide a power analyzer which reduces the cost of maintenance of the overall system and to provide a power analyzer which has very high precision through self-calibration and a non-synchronous measurement technique. It is one more objective of the thesis is to provide a microcontroller-controlled power analyzer that can continuously and rapidly monitor a plurality of circuits. With the thesis, low-cost power and energy analyzer will be developed. The power analyzer that will be developed in the thesis will include a microprocessor coupled to the circuit for performing additional calculations on the electrical variables to thereby derive electrical parameters relating to the performance of the power circuits. These parameters may include Watts, Watt-hours, VARs, Power Factor, etc. After the calculations whole results will be monitoring on the screen and also there will be a real time plotting of the spectrum. [36]

### **1.3 Conclusion and Key Findings**

It's proved that various factors directly affect the measurement quality. Temperature changes of electronic components used are one in all the important factors. thanks to the optimal working environment of the components are different, so as to attenuate the negative impact of this case, the materials used is preferred with higher sensitivity and lower temperature coefficient. Also, the field effect sensor utilized in the current input is tormented by the external magnetic field. To avoid negative effect of this case, it's going to be possible to produce magnetic isolation of the area where the sensor is located on the hardware or standard transformer like rated 100A/4mA is also accustomed get far better results with the high precision. However, a current transformer requires much space. Besides, sensitivity of the operational amplifiers

utilized in voltage and current inputs is critical. A low precision operational amplifier will cause irrelevant results, especially when making measurements too close to zero. To avoid this case, choosing a high quality and high precision operational amplifier will influence positively affect the results. Additionally, chosen MCU is vital. If a microcontroller with high performance and decimal processing capability isn't preferred, it'll influence negatively the results in order that it'll cause loss of sensitivity during the mathematical operations.

Also, the reference voltage for the calculations is critical. So, the battery voltage will also affect negatively the results.

The sampling frequency of the selected microcontroller to be used in the designed digital measurement system, the resolution of the analog-digital converter, the sampling rate and the number of ADC channels that can operate simultaneously are sufficient, calculation can be performed without losing time in sampling.

In addition, if the temperature dependence of the sensors and electronic materials used is calibrated with an external temperature measurement, an error-free measurement can be obtained.

## CHAPTER II

### PHASE LOCKED LOOP (PLL) DESIGN

The phase angle of use may be an important piece of information on the operation of power grids such as PV inverters. A locked phase loop is a closed system in which the internal oscillator is controlled to keep track of the time and the external time signal phase using the feedback loop. PLL is the only servo system that controls its output signal phase and specifies phase error between the output phase and the reference phase is small. Lock quality directly affects the operation of the control loop on applications that are tied to the grid. Since line measurement, voltage imbalance, line immersion, phase loss and frequency variations are common conditions for mechanical and electrical interactions, PLL needs to be able to reject these error sources and maintain a clean phase lock on the grid. [6]. In this section, various software loop lock options will be analyzed and the simulation results will be presented.

#### 2.1 Phase Locked Loop

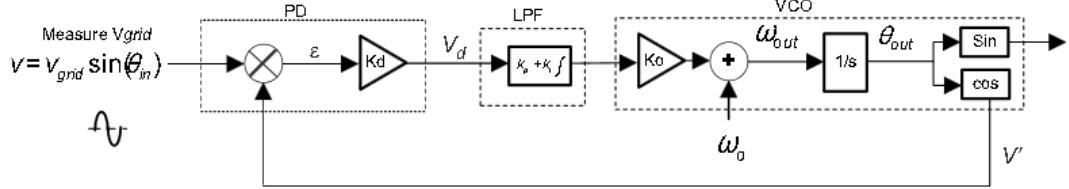

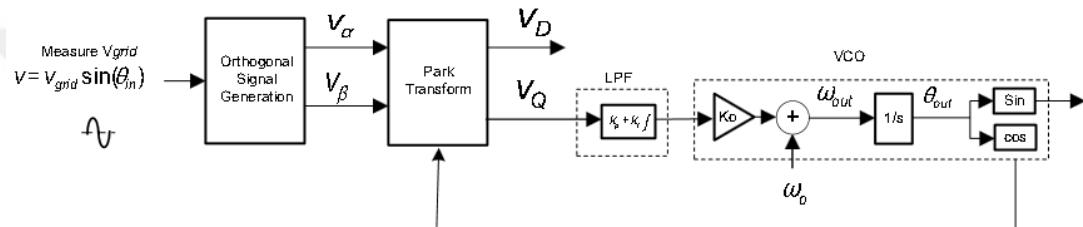

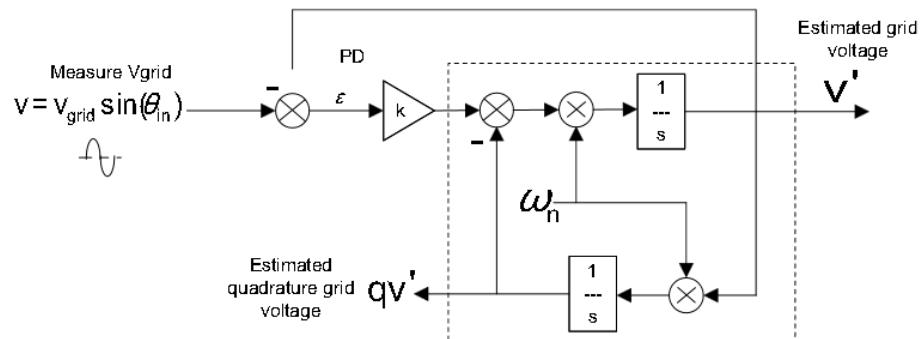

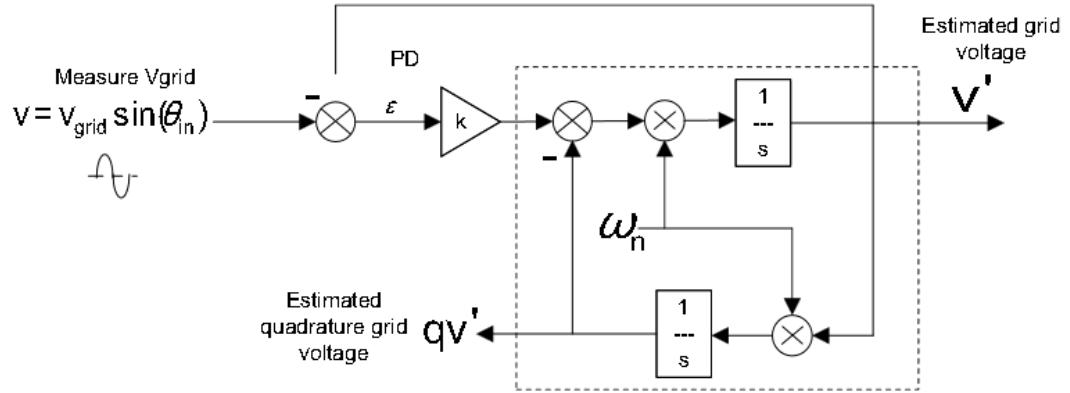

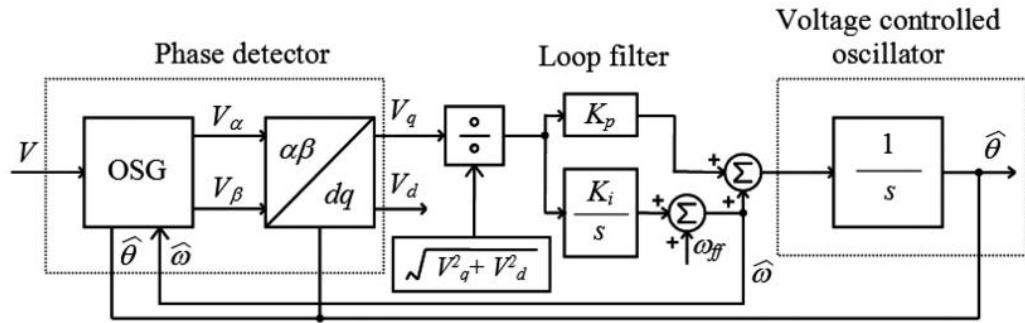

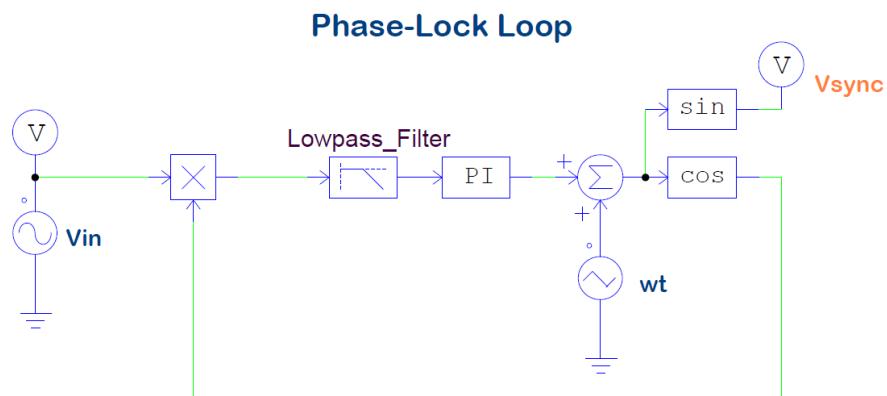

Typically, a phase loop is a closed loop control system with an internal oscillator so that it can lock out the external signal section using the feedback structure. It can be simply expressed as a servo control system that minimizes the phase difference between the reference signal and the output signal. In devices connected to the network, there may be situations such as frequency change, absence of phase or imbalance [6]. In such cases, a phase locked loop design should be designed to minimize these errors for the stability of measurement systems. As seen in Figure (2.1), a simple phase locked loop (PLL) consists of a phase detector, a PI controller and a voltage-controlled oscillator unit at its output.

A functional diagram of a PLL is showing in figure, which consists of a phase detect (PD), a loop filter (LPF), and a voltage-controlled oscillator (VCO).

**Figure 2.1** Phase Locked Loop Block Diagram

The measured grid voltage can be written in terms the grid frequency ( $\omega_{grid}$ ) as follows,

$$v = v_{grid} \cdot \sin(\theta_{in}) - v_{grid} \cdot \sin(\omega_{grid}t + \theta_{grid}) \quad (2.1)$$

Now, assuming that VCO produces sine waves near the sinusoid grid, the VCO output can be labeled,

$$v' = \cos(\theta_{out}) - \cos(\omega_{PLL}t + \theta_{PLL}) \quad (2.2)$$

The purpose of the phase detection block is to compare the input sine with the locked sine from the VCO and to generate the error signal in line with the angle error. In this case, the phase acquisition block doubles the VCO output and the estimated input value to be obtained:

$$v_d = \frac{K_d \cdot v_{grid}}{2} \left[ \sin((\omega_{grid} - \omega_{PLL})t + (\theta_{grid} - \theta_{PLL})) + \sin((\omega_{grid} - \omega_{PLL})t + (\theta_{grid} + \theta_{PLL})) \right] \quad (2.3)$$

From Equation (2.3), it is clear that the output of the PD block contains information about the lock error. However, the lock error information found in PD is linear, and has twice as much variation as grid frequency. To use this error lock information PLL angle, part of the double frequency grid must be removed. In the meantime, ignoring duplicate part of the grid frequency, a lock error is provided by:

$$v_d = \frac{K_d \cdot v_{grid}}{2} \sin((\omega_{grid} - \omega_{PLL})t + (\theta_{grid} - \theta_{PLL})) \quad (2.4)$$

For steady state operation, the  $\omega_{grid} - \omega_{PLL}$  term can be ignored, for small values of theta  $\sin(\theta) \sim \theta$ . Hence, a linearized error is given as:

$$err = \frac{v_{grid}(\theta_{grid} - \theta_{PLL})}{2} \quad (2.5)$$

This error is an input loop filter, which is nothing but a PI controller, which is used to reduce the lock error in the stabilization mode to zero. Small signal analysis is

performed using network theory, in which the response loop is broken to obtain an open loop transfer number and then a closed loop transmission function:

$$\text{Closed Loop TF} = \text{Open Loop TF} / (1 + \text{Open Loop TF}) \quad (2.6)$$

Thus, in response to the line the PLL transfer function can be written as follows:

Closed loop section TF:

$$H_0(s) = \frac{\theta_{out}(s)}{\theta_{in}(s)} - \frac{LF(s)}{s+LF(s)} - \frac{v_{grid} \cdot (k_p s + \frac{k_p}{T_i})}{s^2 + v_{grid} \cdot k_p s + v_{grid} \cdot \frac{k_p}{T_i}} \quad (2.7)$$

Closed loop error transfer function:

$$E_0(s) = \frac{v_d(s)}{\theta_{in}(s)} - 1 - H_0(s) - \frac{s}{s+LF(s)} - \frac{s^2}{s^2 + k_p s + \frac{k_p}{T_i}} \quad (2.8)$$

Comparing the closed loop transfer function with the standard second order system transfer function, provided:

$$H(s) = \frac{2 \cdot \zeta \cdot \omega_n s + \omega_n^2}{s^2 + 2 \cdot \zeta \cdot \omega_n s + \omega_n^2} \quad (2.9)$$

The natural frequency and reduction of the PLL rate in line is given by:

$$\omega_n = \sqrt{\frac{v_{grid} \cdot k_p}{T_i}} \quad (2.10)$$

$$\zeta = \sqrt{\frac{v_{grid} \cdot T_i \cdot k_p}{4}} \quad (2.11)$$

Note to PLL, PI serves two purposes:

- To filter out high frequency that is at twice the frequency of the carrier and grid

- Manage PLL response to track changes in grid shapes, for example, section jumps, size sources, and more. Since the loop filter has a low-pass filter feature, it can be used to filter a portion of the high frequency that was previously ignored. If the network frequency / lock signal frequency is high, the lower PI transition features are good enough to cancel twice the frequency of the network company frequency. However, in grid-connected systems as the grid frequency is very low (50Hz-60Hz), the roll off provided by the PI is not sufficiently satisfactory and introduces a high frequency feature at the loop filter output, which affects PLL performance. From the discussion above, it is clear that the LPF feature of the PI controller cannot be used to eliminate part of a double frequency to grid from the output phase in the case of grid-connected

applications. Therefore, other methods should be used that guide the PD block. In this application report, the two PLL modes that make up the PD exit line, are displayed:

- One uses a notch filter to filter out a double part of a grid frequency on a PD output

- The other uses an orthogonal signal generating method to use the PLL process for a fixed PLL framework in one PLL phase.

## 2.2 Phase Locked Loop (PLL) Methods

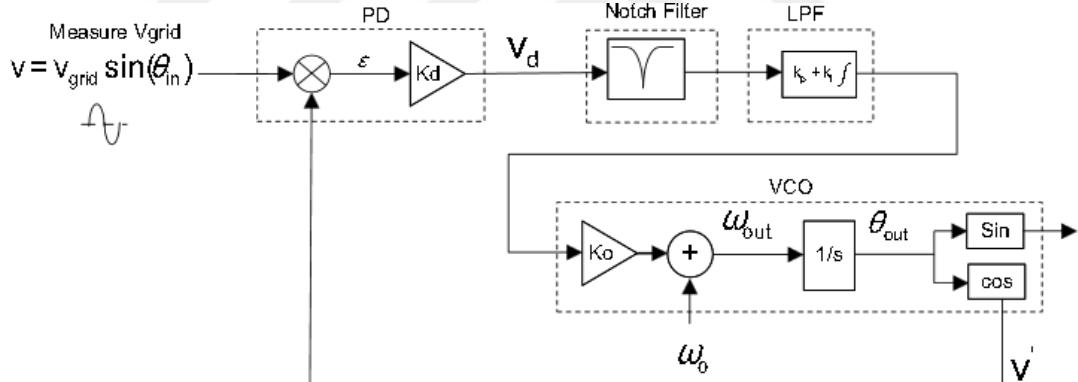

### 2.2.1 Notch Filtered Single Phase PLL

In this PLL method, a notch filter can be used to exit the phase detection block, which doubles the part of the grid frequency very well. The flexible notch filter can also be used for selection by selecting the correct frequency in the event of a grid frequency variation. Section (2.1) illustrates the process of selecting PI coefficients, their digital usage and mapping. The design of the flexible notch filter is displayed with the automatic coefficient calculation method, and in line is displayed using embed code. A single phase, phase locked loop structure with a notch filter is as follows.

**Figure 2.2 Single Phase PLL With Notch Filter**

As discussed in Section (2.1), with the addition of a notch filter, PI tuning can only be performed based on the PLL variable response. Section (2.1) illustrates the digital use of the PI controller and the selection of coefficients for the use of the PI control.

#### 2.2.1.1 Discrete Implementation of PI Controller

The loop filter or the PI is implemented as a digital controller with like this

$$y_{lf}[n] = y_{lf}[n-1] \cdot A_1 + y_{notch}[n] \cdot B_0 + y_{notch}[n-1] \cdot B_1 \quad (2.12)$$

Using z-transform, equation (2.12) can be re-written as:

$$\frac{y_{lf}(z)}{y_{notch}(z)} = \frac{B_0 + B_1 \cdot z^{-1}}{1 - z^{-1}} \quad (2.13)$$

It is well known the PI controller in Laplace transform is given by:

$$\frac{y_{lf}(s)}{y_{notch}(s)} = k_p + \frac{k_i}{s} \quad (2.14)$$

Using bi-linear transformation, replace  $s = \frac{2}{T} \cdot \left( \frac{z-1}{z+1} \right)$ , where  $T = \text{Sampling Time}$ .

$$\frac{y_{lf}(z)}{y_{notch}(z)} = \frac{-\left(\frac{2 \cdot k_p + k_i \cdot T}{2}\right) - \left(\frac{2 \cdot k_p - k_i \cdot T}{2}\right) \cdot z^{-1}}{1 - z^{-1}} \quad (2.15)$$

Equation (2.13) and Equation (2.15) can be compared to a map of the equity and completeness of PI control in a digital domain. The next challenge is to choose the right amount of benefit and total profit. Step response to standard second order calculations:

$$H(s) = \frac{\omega_n^2}{s^2 + 2 \cdot \zeta \cdot \omega_n s + \omega_n^2} \quad (2.16)$$

is given as:

$$y(t) = 1 - ce^{-\sigma t} \cdot \sin(\omega_d \cdot t + \varphi) \quad (2.17)$$

Ignoring the LHP zero from Equation (2.17). The settling time is given as the time it takes for the response to settle between an error band, say this error is  $\delta$ , then:

$$1 - \delta - 1 - ce^{-\sigma t_s} \rightarrow \delta - ce^{-\sigma t_s} \rightarrow t_s - \frac{1}{\sigma} \cdot \ln\left(\frac{c}{\delta}\right) \quad (2.18)$$

$$\text{Where, } \sigma = \zeta \cdot \omega_n \text{ and } c = \frac{\omega_n}{\omega_d} \text{ and } \omega_d = \sqrt{1 - \zeta^2} \cdot \omega_n \quad (2.19)$$

Using settling time as *30 milliseconds*, and the error band as 5% and damping ratio to be 0.7, the natural frequency is obtained to be 158,6859. Back substituting  $k_p = 222,1603$  and  $k_i = 25181,22$ . Back substituting these values into the digital loop filter coefficients:

$$B_0 = \left( \frac{2 \cdot k_p + k_i \cdot T}{2} \right) \text{ and } B_1 = \left( \frac{2 \cdot k_p - k_i \cdot T}{2} \right) \quad (2.20)$$

For 50 kHz run rate of the PLL,  $B_0 = 223,4194$  and  $B_1 = -220,901$ .

### 2.2.1.2 Adaptive Notch Filter Design

The notch filter used in the PLL shown in Figure (2.1) requires a double reduction of the grid frequency. The grid frequency, although stable, can vary somewhat, and with

the increase in renewable content major variations are possible. Therefore, in order to accurately write a grid frequency, a compatible notch filter is used. The standard notch filter number is “s-domain” as shown in Equation (2.21):

$$H_{n-f}(s) = \frac{s^2 + 2\cdot\zeta_2\cdot\omega_n s + \omega_n^2}{s^2 + 2\cdot\zeta_1\cdot\omega_n s + \omega_n^2} \quad (2.21)$$

where  $\zeta_2 \ll \zeta_1$  for notch action to occur.

Discretizing Equation (2.21) using zero order hold,  $s = \frac{(z-1)}{T}$ , the equation is reduced to:

$$H_{n-f}(z) = \frac{z^2 + (2\cdot\zeta_2\cdot\omega_n\cdot T - 2)\cdot z + (-2\cdot\zeta_2\cdot\omega_n\cdot T + 2\omega_n^2\cdot T^2 + 1)}{z^2 + (2\cdot\zeta_1\cdot\omega_n\cdot T - 2)\cdot z + (-2\cdot\zeta_1\cdot\omega_n\cdot T + 2\omega_n^2\cdot T^2 + 1)} - \frac{B_0 + B_1\cdot z^{-1} + B_2\cdot z^{-2}}{A_0 + A_1\cdot z^{-1} + A_2\cdot z^{-2}} \quad (2.22)$$

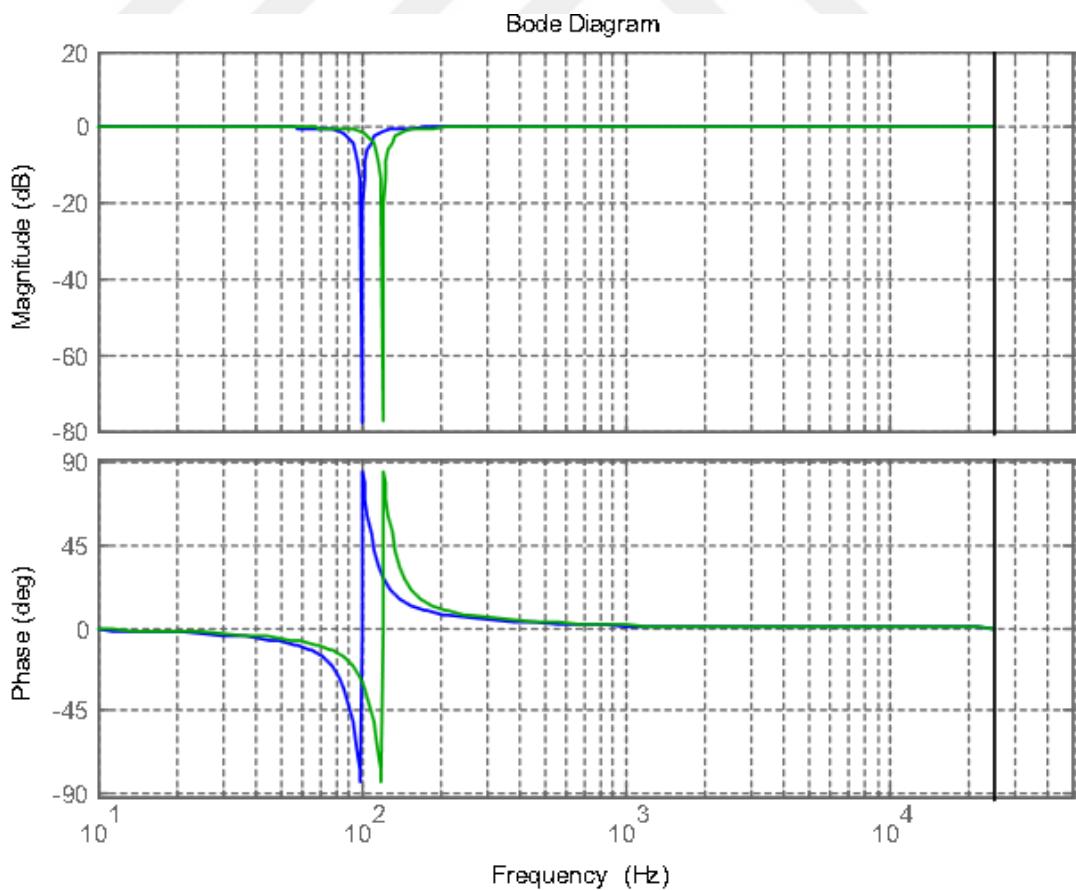

In the Equation (2.22) the maps are in digital format with two poses zero and the notch filter coefficients can be changed variable as the grid frequency varies by calling the posterior system measuring the coefficients based on the grid rating scale. For example, taking  $\zeta_2 = 0,00001$  and  $\zeta_1 = 0,1$  ( $\zeta_2 \ll \zeta_1$ ), the notch response as shown in Figure (2.2) of the 50 Hz and 60 Hz grid, where the coefficient is calculated based on the grid. The notch filter response is shown below in Figure (2.2).

**Figure 2.3** The response of the notch filter

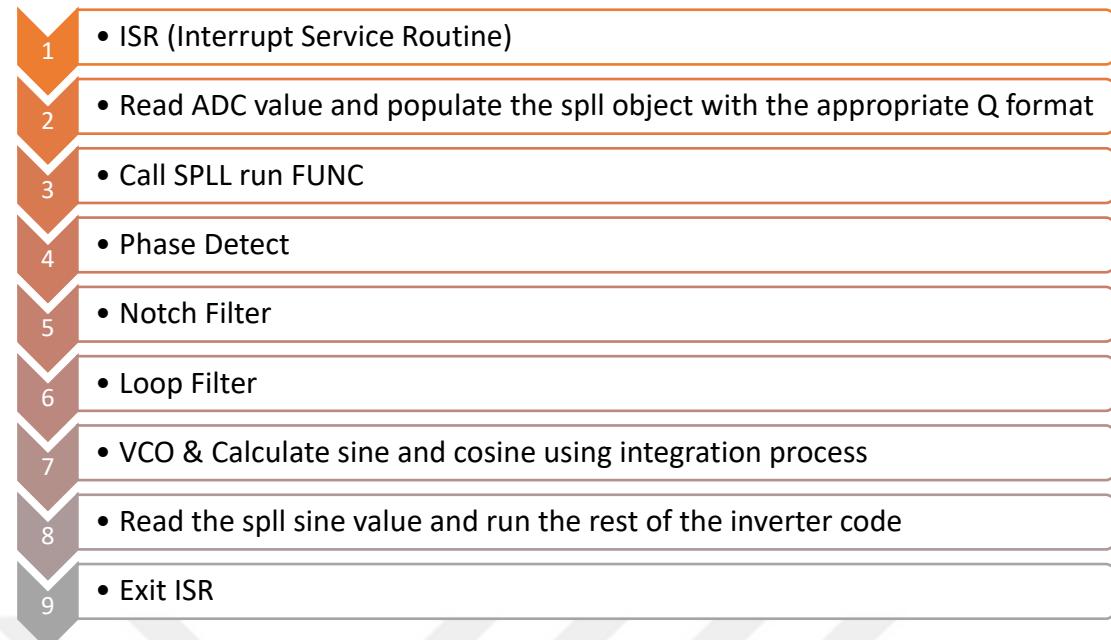

### 2.2.1.3 Sine and Cosine Generation

The PLL uses sine and cosine calculation, these calculations can consume large number of cycles in a typical microcontroller. To avoid this issue, the sine and cosine value is generated in this module by applying the principle of integration.

$$y(t + \Delta t) = y(t) + \frac{dy(t)}{dt} \cdot \Delta t \quad (2.23)$$

For sine and cosine signal, this reduces to:

$$\sin(t + \Delta t) = \sin(t) + \frac{d\sin(t)}{dt} \cdot \Delta t - \sin(t) + \cos(t) \cdot \Delta t \quad (2.24)$$

$$\cos(t + \Delta t) = \cos(t) + \frac{d\cos(t)}{dt} \cdot \Delta t - \cos(t) + \sin(t) \cdot \Delta t \quad (2.25)$$

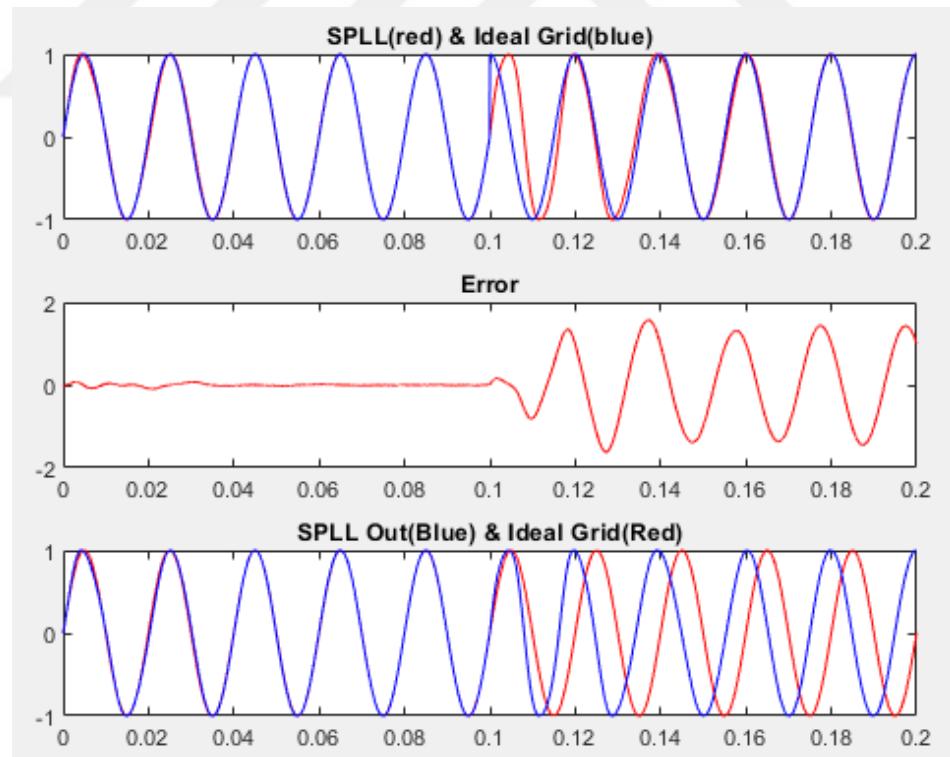

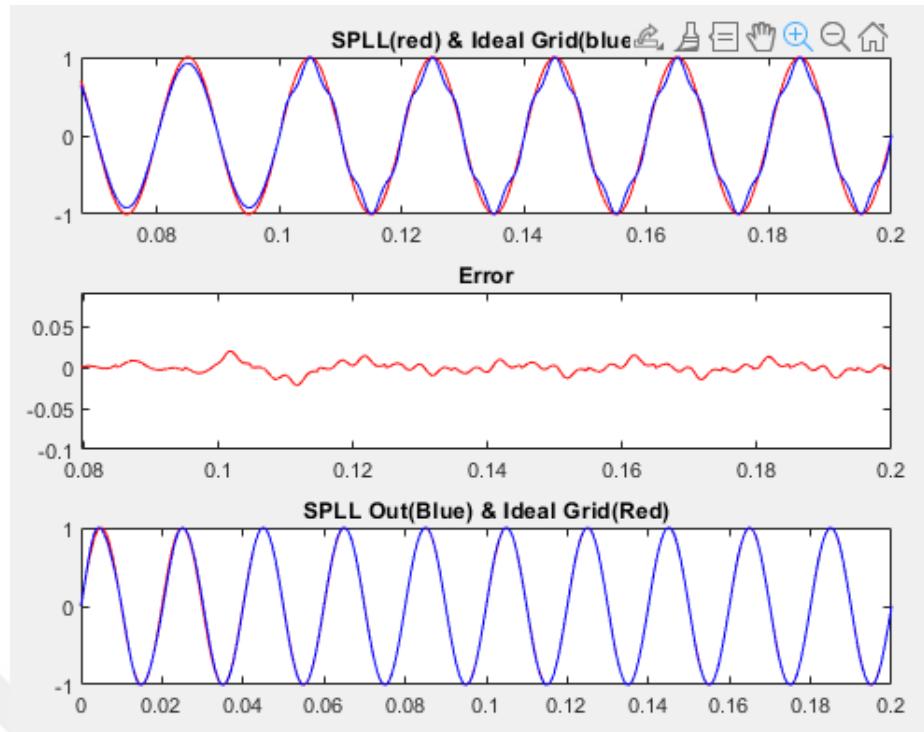

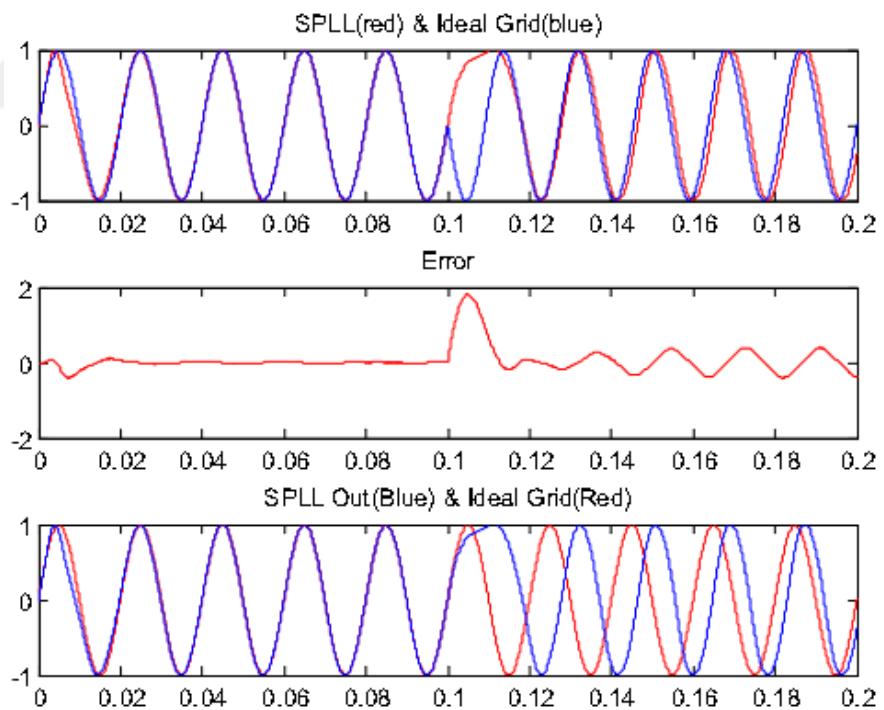

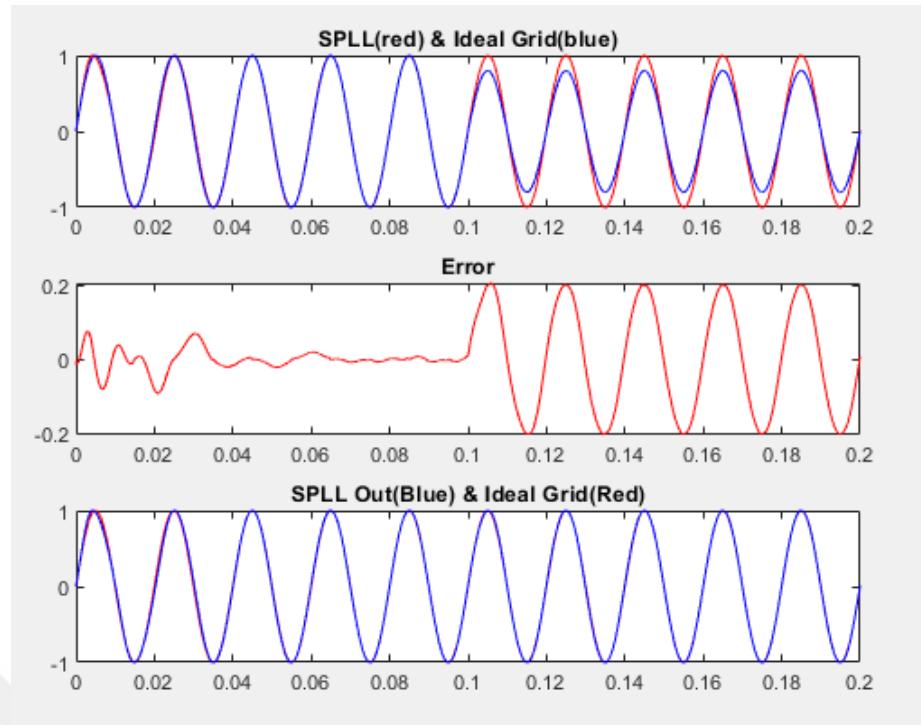

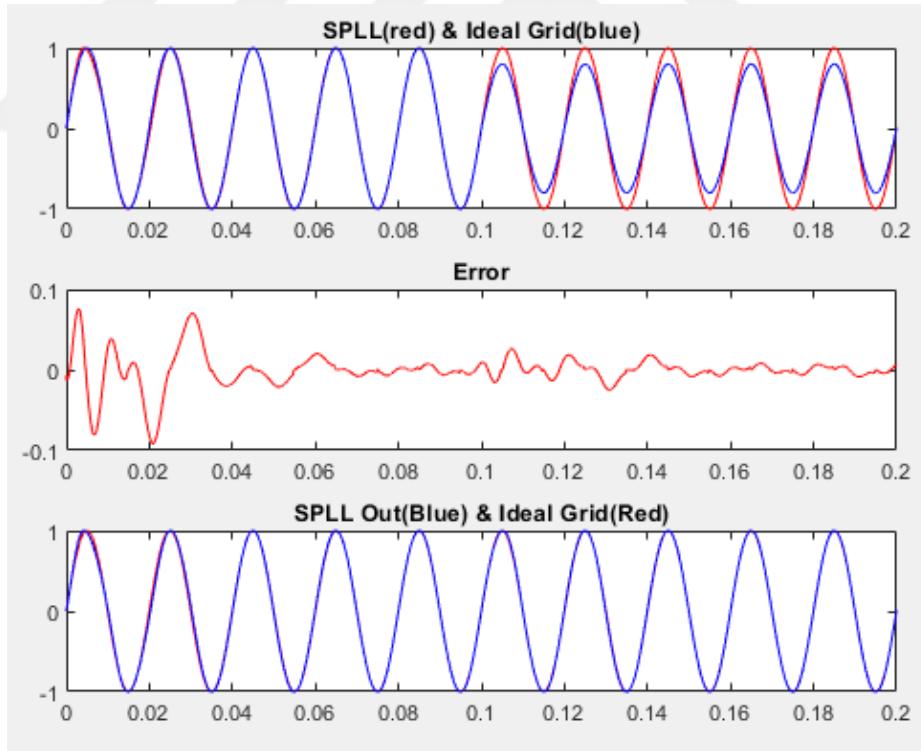

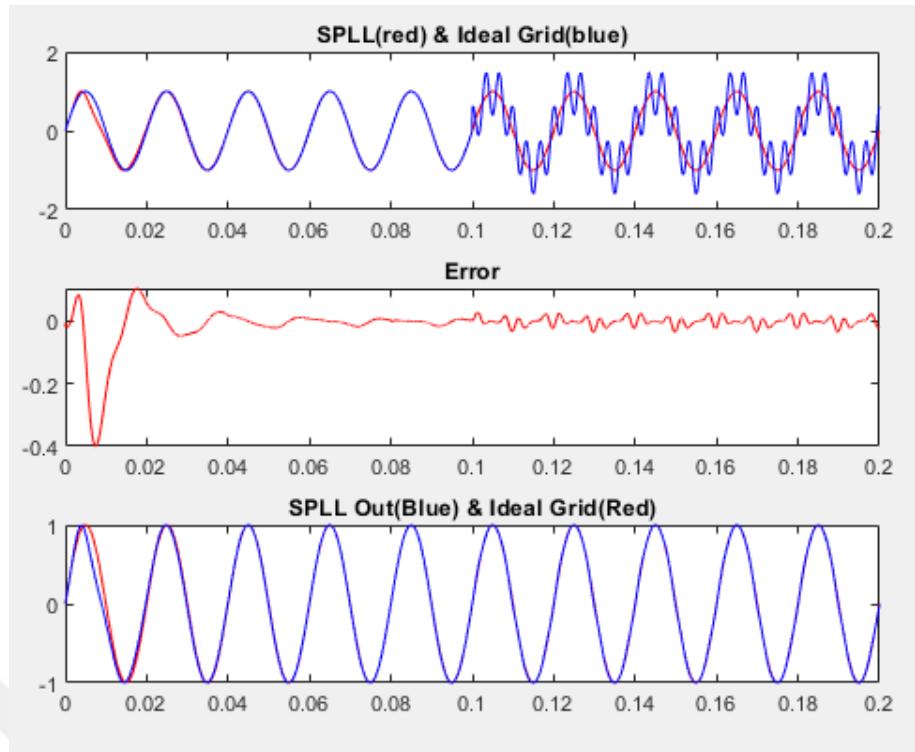

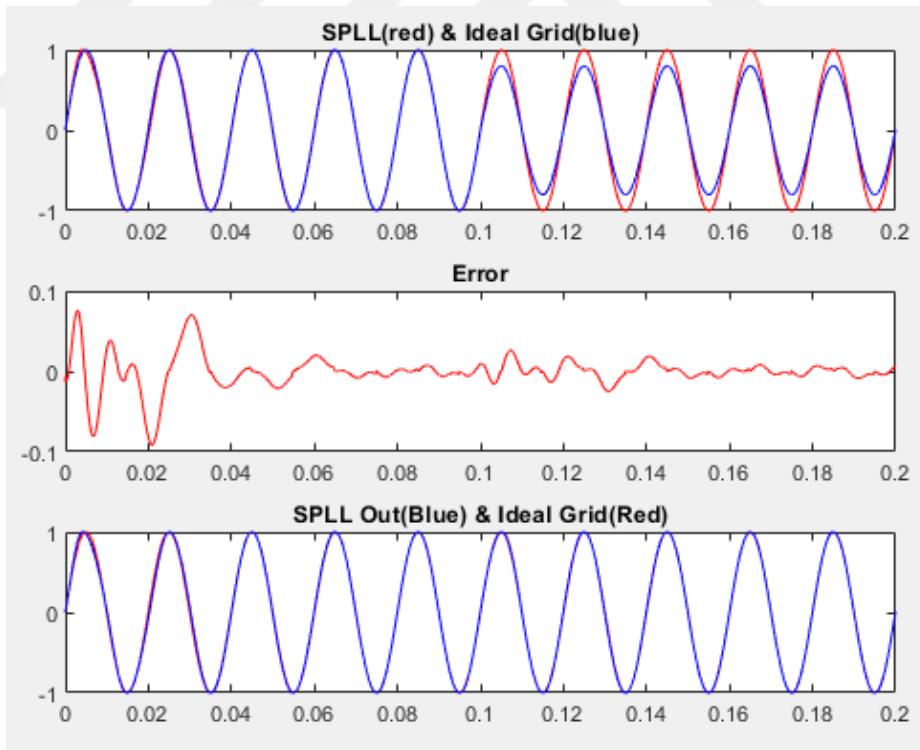

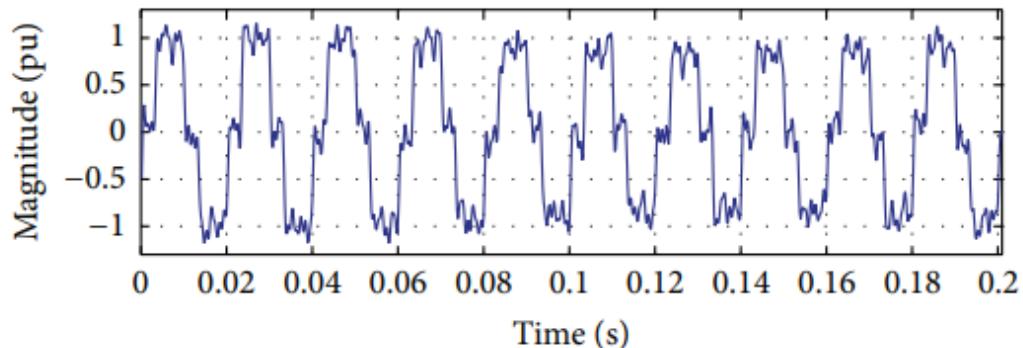

### 2.2.1.4 Simulating the Phase Locked Loop for Varying Conditions