### A NOVEL MODELING METHODOLOGY AND PERFORMANCE IMPROVEMENT TECHNIQUE FOR DMTL PHASE SHIFTERS

### A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

$\mathbf{B}\mathbf{Y}$

## İPEK İSTANBULLUOĞLU

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRICAL AND ELECTRONICS ENGINEERING

SEPTEMBER 2006

Approval of Graduate School of Natural and Applied Sciences

Prof. Dr. Canan ÖZGEN

Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof. Dr. İsmet ERKMEN

Head of Department

Prof. Dr. Tayfun AKIN

**Co-Supervisor**

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

Assoc. Prof. Dr. Sencer KOÇ

Supervisor

Examining Committee Members:

| Prof. Dr. Altunkan HIZAL      | (METU, EEE)   |  |

|-------------------------------|---------------|--|

| Assoc. Prof. Dr. Sencer KOÇ   | (METU, EEE)   |  |

| Prof. Dr. Tayfun AKIN         | (METU, EEE)   |  |

| Assoc. Prof. Dr. Şimşek DEMİR | (METU, EEE)   |  |

| Prof. Dr. Hayrettin KÖYMEN    | (BİLKENT, EE) |  |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

İpek İstanbulluoğlu

## ABSTRACT

# A NOVEL MODELING METHODOLOGY AND PERFORMANCE IMPROVEMENT TECHNIQUE FOR DMTL PHASE SHIFTERS

İstanbulluoğlu, İpek M. Sc., Department of Electrical and Electronics Engineering Supervisor: Assoc. Prof. Dr. Sencer Koç Co-Supervisor: Prof. Dr. Tayfun Akın

September 2006, 135 pages

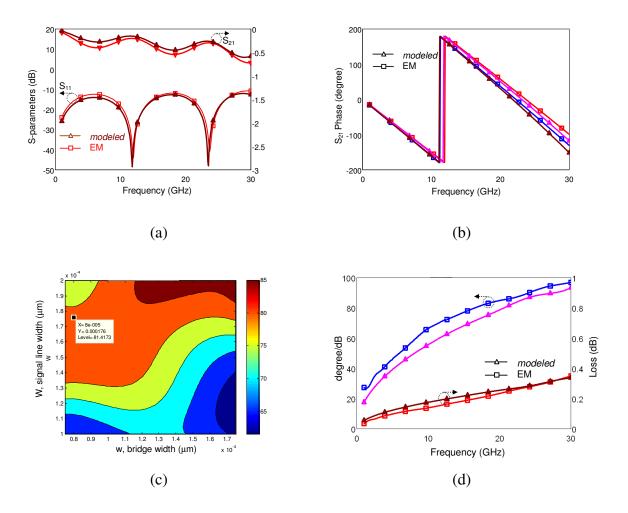

This thesis presents distributed MEMS transmission line (DMTL) phase shifters, emphasizing the circuit modeling and design as well as the performance improvement. A novel modeling methodology is introduced for DMTL unit sections, with bridge widths larger than 50  $\mu$ m. The introduced model is compared with EM simulation results and the *CLR* modeling results. For structures with bridge widths larger than 50  $\mu$ m, the introduced model fits the simulation results much better than the *CLR* model. The simulated structures are fabricated in METU micro-electronics facilities on glass substrates using gold structural layers. 1-20 GHz S-parameter measurement results of various DMTL structures are compared with the

introduced model. It is observed that the S-parameters match except for a scaling need in the insertion loss. The measurement results give 2 dB insertion and 15 dB isolation at 20 GHz.

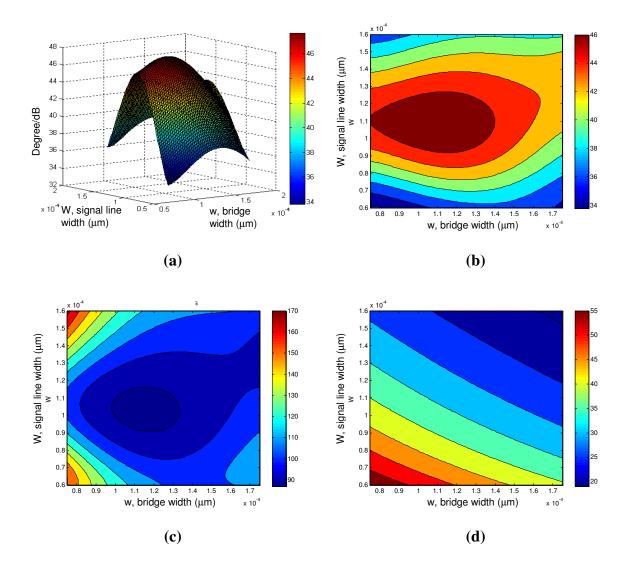

The ABCD parameters of the introduced model are converted into S-parameters. Loss and the phase shift of the DMTL structures are expressed in terms of these S-parameters. These expressions are re-written as MATLAB code, from which the phase shift/loss (degree/dB) performance is evaluated. Therefore degree/dB plots with respect to bridge widths and center CPW conductor widths are obtained. From these plots the optimum DMTL phase shifters, which give maximum phase shift for minimum loss are determined for a pre-defined DMTL structure.

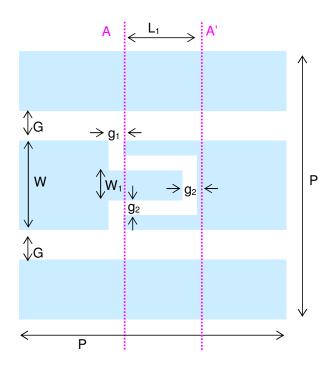

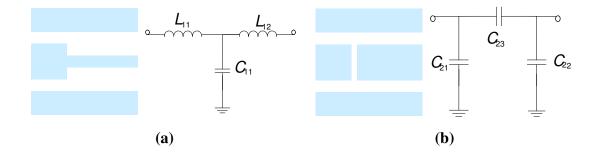

To increase the degree/dB performance of a DMTL phase shifter, a change in the geometry of the DMTL phase shifters is proposed. The geometry change is based on inserting an open-ended stub through the signal line and connecting one side of the stub to the bridge. By this way, the stub capacitance is added to the shunt capacitance of the bridge satisfying a larger phase shift. The simulations point out a performance of 217 degree/dB at 20 GHz with a 15 % change in the 25  $\mu$ m wide bridge height ratio.

Keywords: RF MEMS, Distributed loaded line phase shifters, CPW open-ended stubs, Modeling, Micromachining.

# DMİH FAZ KAYDIRICILAR İÇİN ÖZGÜN MODELLEME METODU VE PERFORMANS ARTTIRMA TEKNİĞİ

İstanbulluoğlu, İpek Yüksek Lisans, Elektrik ve Elektronik Mühendisliği Bölümü Tez Yöneticisi: Doç. Dr. Sencer Koç Ortak Tez Yöneticisi: Prof. Dr. Tayfun Akın

Eylül 2006, 135 sayfa

Bu tez, dağıtılmış hat MEMS iletim hattı (DMİH) faz kaydırıcılarını, devre modellemesi, tasarımı ve faz kaydırıma performansının iyileştirilmesi vurgulanarak sunmaktadır. Köprü genişliği 50 µm'den büyük olan DMİH'ların birim kesitleri için yeni bir modelleme yöntemi ortaya konmuştur. Önerilen model EM benzetim sonuçlarıyla ve *CLR* modellemesiyle karşılaştırılmıştır. Köprü genişliği 50 µm'den büyük olan yapılarda, önerilen yöntem *CLR*'a gore çok daha iyi sonuçlar vermektedir. Benzetimleri yapılan yapılar, METU mikro-elektronik tesislerinde taban malzemesi cam, yapısal malzemeler de altın olacak şekilde üretilmiştir. 1-20 GHz arası ölçülen S-parametreleri önerilen modelle karşılaştırmıştır. Araya girme kaybındaki artış dışında ölçümler modelle bire bir uyum göstermektedir. Ölçüm sonucunda, 20 GHz'te 2 dB araya girme kaybı, 15 dB yalıtım elde edilmiştir.

Önerilen modelin S-parametreleri ABCD parametreleri cinsinden ifade edilmiştir. Hattaki kayıp ve faz kaydırma miktarı elde edilen S-parametreleri cinsinden bulunmuştur. Bulunan ifadeler MATLAB kodu olarak tekrar yazılmış ve bu kod yardımıyla derece/kayıp performansı hesaplanmıştır. Bu sayede köprü genişliği ve sinyal hattı genişliğine göre değişen faz kaydırma/kayıp (derece/dB) grafikleri elde edilmiştir. Bu grafikleriden belirli bir DMİH faz kaydırıcı için maksimum derece/dB veren köprü ve sinyal hattı genişliği tesbit edilebilmektedir.

DMİH faz kaydırıcının derece/kayıp performansını arttırmak için, DMİH hattı yapısında fiziksel bir değişilik yapılması önerilmiştir. Yapılması planlanan değişiklik, sinyal hattına açık uçlu eş düzlemsel dalga kılavuzu kütük yerleştirilmesi esasına dayanmaktadır. Bu kütüğün açık olmayan ucu da köprüye bağlanmaktadır. Bu sayede, kütük kapasitansı da köprünün paralel kapasitansına eklenir ki bu da sonuçta elde edilen faz kaydırma miktarında bir artış demektir. EM benzetim sonuçları, 25 µm genişliğindeki köprülerin, köprü yüksekliğinin % 15 oranında değişmesi sonucu 217 derece/dB'lik bir performans öngörmektedir.

Anahtar Kelimeler: RF MEMS, Dağınık yüklenmiş hat faz kaydırıcılar, Açık uçlu EDK kütük, Modelleme, Mikroişleme.

To My Mother and My Father

## ACKNOWLEDGEMENTS

First and foremost, I wish to express my acknowledgements to my advisors Sencer Koç and Tayfun Akın for their supervision, and encouragement during my research. I also thank them for their helpful discussions of the problems I encountered. I am thankful to Şimşek Demir and Özlem Aydın Çivi for not only their contributions in this thesis, but also their support during my graduate studies. I also would like to thank to Altunkan Hızal for giving us the chance of studying in Millimeter and Microwave laboratories.

I am particularly grateful to Kağan Topallı for his encouragement, and inspiration throughout the development of my thesis. He has been an educator, an elder brother, and above all he has been an exceptional model for me during these two years with his academic insights and his guidance. I also would like to thank to Mehmet Ünlü for being a master in my graduate studies. I appreciate all his academic teachings and his supports.

I would like to express my everlasting gratitude to Engin Ufuk Temoçin for being an excellent colleague during these two years. I would like to thank him for his lively friendship, his non-monotonous perspective of life, and his assistance in every study I undertake. Without him, it would be much harder to accomplish the goals of this effort. I would like to express my thanks to Halil İbrahim Atasoy and Ömer Bayraktar for being wonderful group members, for being supportive all the time and for transforming the RF MEMS group to a family. I am also grateful to Halil İbrahim Atasoy for his time and effort during the measurements.

I would like to thank to whole MEMS-VLSI group for their friendship and their helps during my graduate studies. I am especially grateful to İlker Ender Ocak for his time while capturing the SEM photographs. I am thankful to the METU-MET stuff for their collaboration during the fabrication.

I would like to express my special thanks to Yusuf Bahadır Turhan for his understanding, his patience, and his support.

I thank to my mother and my father for everything in my life.

## **TABLE OF CONTENTS**

| PLAGIARISMi                                                   |

|---------------------------------------------------------------|

| ABSTRACTii                                                    |

| ÖZ                                                            |

| DEDICATION                                                    |

| ACKNOWLEDGEMENTSvii                                           |

| TABLE OF CONTENTS                                             |

| LIST OF TABLESxii                                             |

| LIST OF FIGURES                                               |

| 1. INTRODUCTION                                               |

| 1.1. PHASE SHIFTER OVERVIEW                                   |

| 1.1.1. RF MEMS Phase Shifters                                 |

| 1.1.2. Distributed MEMS Phase Shifters                        |

| 1.1.3. Previous DMTL Phase Shifter Studies at METU            |

| 1.2. THESIS OBJECTIVES AND ORGANIZATION                       |

| 2. COPLANAR WAVEGUIDE, MEMS SWITCH AND DMTL PHASE             |

| SHIFTER THEORY                                                |

| 2.1. COPLANAR WAVEGUIDE THEORY                                |

| 2.1.1. Conductor Backed Coplanar Waveguide (CBCPW)            |

| 2.1.2. CBCPW Analysis in the Presence of a Top Metal Cover    |

| 2.1.3. Attenuation Characteristics of CPW                     |

| 2.2. RF MEMS SWITCH THEORY                                    |

| 2.2.1. RF MEMS Shunt Switch                                   |

| 2.2.1.1. RF MEMS Shunt Switch Circuit Model (The CLR Model)23 |

| 2.2.1.2. RF MEMS Shunt Switch Electromagnetic Model           |

| 2.3. DISTIBUTED MEMS TRANSMISSION LINE THEORY                 |

|     | 2.3.1.     | DMTL Phase Shifters                                              |

|-----|------------|------------------------------------------------------------------|

| 3.  | DMTL       | PHASE SHIFTER DESIGN, MODELING AND STRUCTURAL                    |

| IMP | ROVEM      | ENT                                                              |

| 3.  | 1. DIS     | STRIBUTED MEMS TRANSMISSION LINE MODELING                        |

|     | 3.1.1.     | Theoretical Explanation the Proposed HICAPLO Model and           |

|     | Extraction | on of the Model Parameters                                       |

|     | 3.1.1.     | 1. High-impedance and Low-impedance Transmission Line            |

|     | Param      | neters 39                                                        |

|     | 3.1.1.     | 2. Parallel Plate Capacitance                                    |

|     | 3.1.2.     | Comparison of the Proposed HICAPLO Model and the CLR Model       |

|     | with the   | Simulations                                                      |

|     | 3.1.3.     | Low-impedance Line Loss Formulation                              |

| 3.2 | 2. OP      | TIMUM DMTL PHASE SHIFTER DESIGN USING THE                        |

| PF  | ROPOSE     | D HICAPLO MODEL                                                  |

|     | 3.2.1.     | Effect of Model Parameters on the degree/dB Performance56        |

|     | 3.2.2.     | Application of Proposed DMTL Modeling Approach in Degree/dB      |

|     | perform    | ance Calculation                                                 |

|     | 3.2.3.     | Optimum Phase Shifter Design using the Introduced Techniuque     |

|     | when K=    | =500 μm                                                          |

| 3.3 | 3. INS     | SERTION OF OPEN-ENDED STUB THROUGH THE SIGNAL LINE               |

| Ol  | F DMTL     | PHASE SHIFTER                                                    |

|     | 3.3.1.     | Open-Ended CPW Series Stub Overview                              |

|     | 3.3.2.     | Insertion of OES in the Center Conductor of Unit DMTL Section 72 |

| 4.  | FABRIC     | CATION OF THE DESIGNED DMTL PHASE SHIFTERS                       |

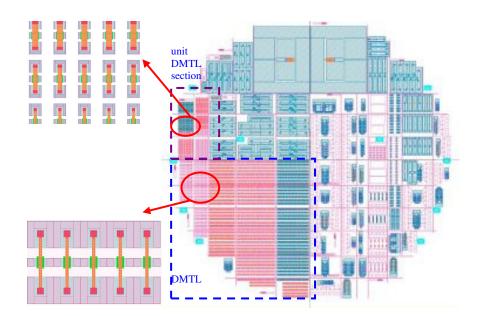

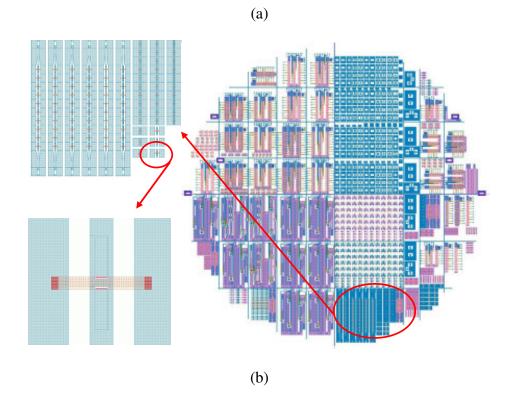

| 4.  | 1. LA      | YOUT DRAWING AND MASK GENERATION                                 |

| 4.2 | 2. FA      | BRICATION TECHNIQUES AND MATERIALS 89                            |

|     | 4.2.1.     | Film Deposition                                                  |

|     | 4.2.2.     | Photolithography                                                 |

|     | 4.2.3.     | Etching and Electroplating                                       |

|     | 4.2.4.     | Sacrificial Layer Coating and Release                            |

| 4  | .3.   | MA    | TERIALS                                                       | 93  |

|----|-------|-------|---------------------------------------------------------------|-----|

| 4  | .4.   | PRC   | DCESS FLOW USED IN DMTL FABRICATION                           | 95  |

| 4  | .5.   | FAE   | BRICATION RESULTS                                             | 102 |

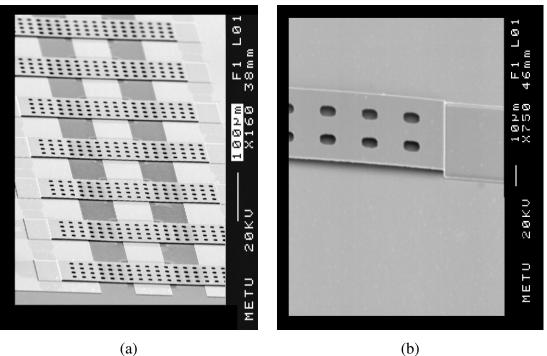

|    | 4.5.  | 1.    | SEM Pictures                                                  | 102 |

| 5. | ME    | ASU   | REMENT OF THE FABRICATION DMTL PHASE SHIFTERS                 | 106 |

| 5  | .1.   | ME    | ASUREMENT METHODOLOGY                                         | 106 |

|    | 5.1.  | 1.    | Measurement Setup                                             | 106 |

| 5  | .2.   | ME    | ASUREMENT RESULTS                                             | 108 |

|    | 5.2.  | 1.    | Measurement Results of the DMTL Structures Designed to Verify | the |

|    | Prop  | posed | HICAPLO Model                                                 | 108 |

|    | 5.2.2 | 2.    | Measurement Results of the DMTL structures designed to verify | the |

|    | tecn  | ique  | proposed to evaluate degree/dB performance                    | 116 |

| 6. | COI   | NCLU  | USIONS AND FUTURE WORKS                                       | 120 |

| RE | FERE  | NCE   | 2S                                                            | 126 |

| AP | PENE  | DIX   |                                                               | 133 |

## LIST OF TABLES

| Table 1.1 Performance comparison of FETs, PIN diode, and RF MEMS switches4           |

|--------------------------------------------------------------------------------------|

| Table 1.2 Average on Wafer Loss for MEMS and GaAs-FET 3-bit Phase Shifters $\dots 5$ |

| Table 1.3 Examples of fabricated DMTL Phase Shifters.    9                           |

| Table 3.1 Dimensions, calculated high-impedance line parameters for seven types of   |

| DMTL structures, @ 10 GHz, P=400 µm, L=400µm×20=8000 µm for all                      |

| structures                                                                           |

| Table 3.2 Dimensions, calculated low-impedance line parameters for seven types of    |

| DMTL structures, @10GHz, $P$ =400 µm, $L$ =400µm×20=8000 µm for all                  |

| structures                                                                           |

| Table 3.3 Calculated $C_S$ values for seven types of DMTL structures, @10GHz,        |

| P=400 $\mu$ m, L=400 $\mu$ m×20=8000 $\mu$ m for all structures                      |

| Table 3.4 The optimized and the calculated values of the shunt capacitance for       |

| different DMTL structures                                                            |

| Table 3.5 $A_n(W)$ coefficients used in Loss formulation                             |

| Table 3.6 M coefficients used in the extra loss formulation                          |

| Table 3.7 Dimensions of four types of DMTL structures designed on Pyrex 7740         |

| glass substrates, <i>H</i> =500 $\mu$ m ( $\epsilon_{r=}$ 4.6, tan $\delta$ =0.005 ) |

| Table 3.8 The capacitance values and the percent capacitance changes of Type I       |

| DMTL phase shifter for different bridge widths                                       |

| Table 3.9 Dimensions, calculated high-impedance line parameters for seven types of   |

| DMTL structures, @ 10 GHz, P=400 µm, L=400µm×20=8000 µm for all                      |

| structures                                                                           |

| Table 3.10 Dimensions of the DMTL structures to be fabricated                        |

| Table 3.11 Dimensions of the designed optimum DMTL phase shifter when $K=220$        |

|                                                                                      |

| Table 3.12. Dimensions of four types of OES embedded unit DMTL sections, where                                         |

|------------------------------------------------------------------------------------------------------------------------|

| $W=15 \mu m$ , $G=10 \mu m$ , $w=30 \mu m$ , $W_2=10 \mu m$ , $g_1=3 \mu m$ , $d=0.6 \mu m$ ,                          |

| $L_{l} = 14.5 \ \mu m.$                                                                                                |

| Table 3.13. Dimensions of four types of OES embedded unit DMTL sections, where                                         |

| $W=15 \mu m$ , $G=10 \mu m$ , $w=30 \mu m$ , $W_2=10 \mu m$ , $g_1=3 \mu m$ , $d=0.6 \mu m$ ,                          |

| $L_l = 14.5 \ \mu m.$                                                                                                  |

| Table 3.14. Total capacitance and phase shift amount of three types of unit DMTL                                       |

| sections, where W=15 $\mu$ m, G=10 $\mu$ m, w=30 $\mu$ m, W <sub>2</sub> =10 $\mu$ m, g <sub>1</sub> =3 $\mu$ m, d=0.6 |

| $\mu$ m, $L_I$ = 14.5 $\mu$ m and $Z_{unloaded}$ =48 $\Omega$                                                          |

| Table 3.15. Four types of unit DMTL sections, where $W=176 \mu m$ , $G=162 \mu m$ , $w=80$                             |

| $\mu$ m, $W_2$ =100 $\mu$ m, $g_1$ =15 $\mu$ m, $d$ =5 $\mu$ m, $C_{CLR, hdown=1.7 \mu m}$ =91 fF, $C_{CLR, hup=2}$    |

| μm=78fF79                                                                                                              |

| Table 3.16. Designed OES embedded unit DMTL sections, where $d=5 \mu m$ ,                                              |

| <i>g</i> <sub>2</sub> =5 μm82                                                                                          |

| Table 3.17. Designed unit DMTL sections without OES, $P = 1000 \mu m \dots 82$                                         |

| Table 5.1. Before / after annealing bridge heights of the fabricated DMTL structures                                   |

| with bridge widths larger than 50 $\mu$ m                                                                              |

| Table 5.2. Measured, HICAPLO modeled and CLR modeled phase shifts of                                                   |

| differend DMTL structures @ 20 GHz118                                                                                  |

|                                                                                                                        |

| Table 5.3.       Measured, HICAPLO modeled and CLR modeled insertion losses of                                         |

|                                                                                                                        |

| Table 5.3. Measured, HICAPLO modeled and CLR modeled insertion losses of                                               |

## **LIST OF FIGURES**

| Figure 1.1 A phased-array system overview                                             |

|---------------------------------------------------------------------------------------|

| Figure 1.2 (a) Reflection phase shifter. (b) Switched-line phase shifter. (c) Loaded- |

| line phase shifter                                                                    |

| Figure 1.3 Distributed MEMS transmission line (DMTL) schematic                        |

| Figure 1.4 (a) The measured DMTL phase shifter in the thesis work of Hüseyin          |

| Sağkol. (b) The results of the modeling study finalized in [29]10                     |

| Figure 2.1 Coplanar Waveguide schematic                                               |

| Figure 2.2 CBCPW with top cover limiting cases                                        |

| Figure 2.3 Schematic of (a) series switch (b) shunt switch                            |

| Figure 2.4 Side view of RF MEMS shunt switch with bridge anchors are connected        |

| to ground planes                                                                      |

| Figure 2.5 Top view of a shunt switch and its lumped element model23                  |

| Figure 2.6 Distributed MEMS transmission line (DMTL) schematic                        |

| Figure 2.7 Lumped element transmission line model of the unit length DMTL 28          |

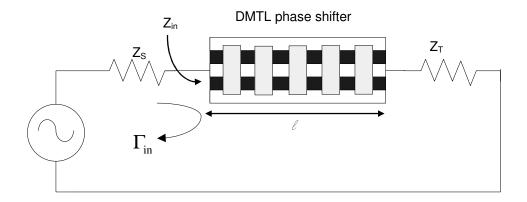

| Figure 2.8 A DMTL phase shifter placed in a terminated circuit system                 |

| Figure 3.1 (a) Top view of one of the DMTL unit sections, where $w >50\mu m$ .        |

| (b) Lumped-element CLR model of the unit section of DMTL [7].(c) Low-                 |

| impedance transmission line represented MEMS bridge model of the unit                 |

| section of DMTL [29]                                                                  |

| Figure 3.2 Two unit DMTL strucutures; one with bridge width smaller than 50 $\mu m$   |

| and the other with bridge width larger then 50 $\mu$ m                                |

| Figure 3.3 (a) S-parameter comparison of HFSS EM simulation and the CLR model         |

| of a DMTL structure with bridge width 230 and signal line width 225 $\mu$ m 38        |

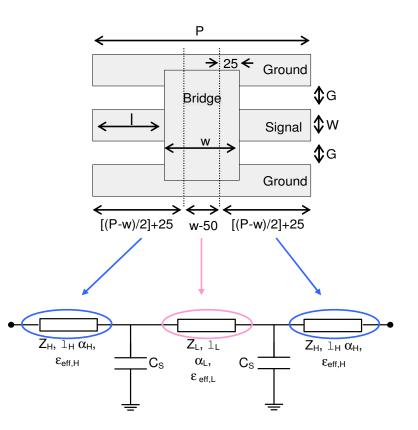

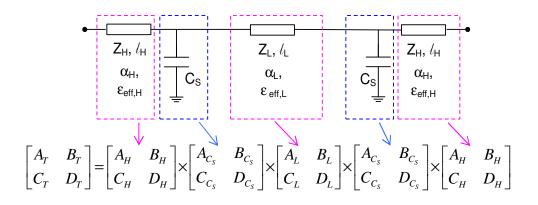

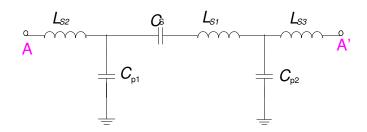

Figure 3.4. The proposed circuit model for the unit DMTL section, where the MEMS bridges are represented by using both low-impedance transmission lines and the *CLR* model.

38

Figure 3.5. The side view of parallel plates and the fringing field in between.

42

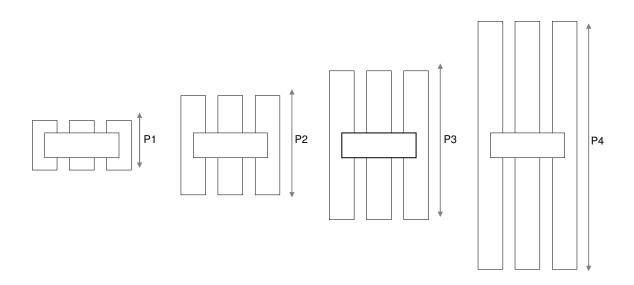

Figure 3.6. Different loading periodicityes of a sample DMTL structure, where P1=200 µm, P2=400 µm, P3=600 µm, P4=1000 µm.

44

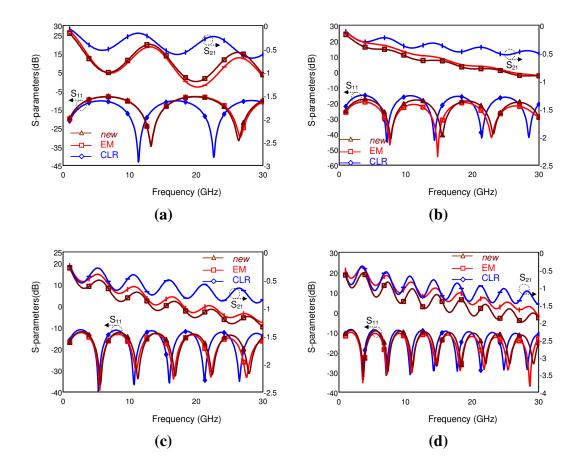

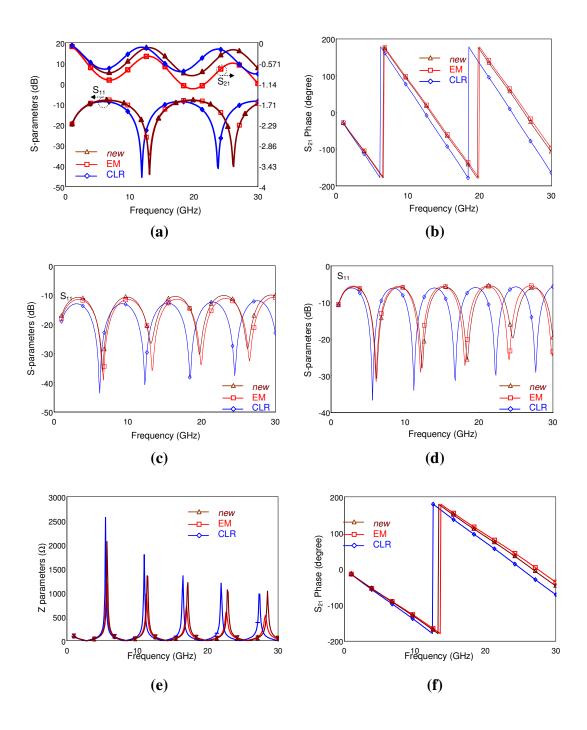

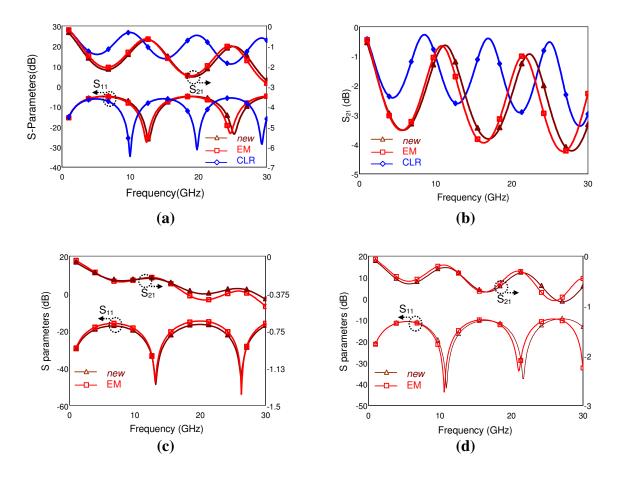

Figure 3.7. (a) EM and circuit simulation results for DMTL Type IV , where periodicity is 200 µm, (b) periodicity is 400 µm, (c) periodicity is 600 µm, and (d) periodicity is 1000 µm.

46

Figure 3.8. (a) EM and circuit simulation results for: DMTL Type VII, where periodicity is 200 µm (b) DMTL Type V, where periodicity is 400 µm, (d) DMTL Type VI, where periodicity is 400 µm, (d) DMTL Type VI, where periodicity is 400 µm (e) DMTL Type VII, where periodicity is 600 µm, (f) DMTL Type II, where periodicity is 400 µm.

47

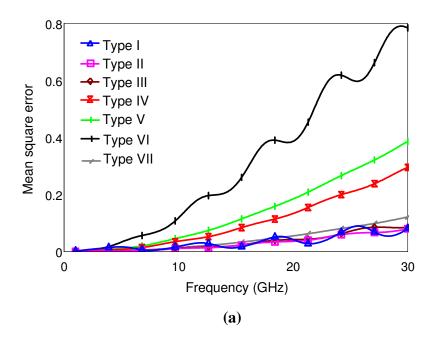

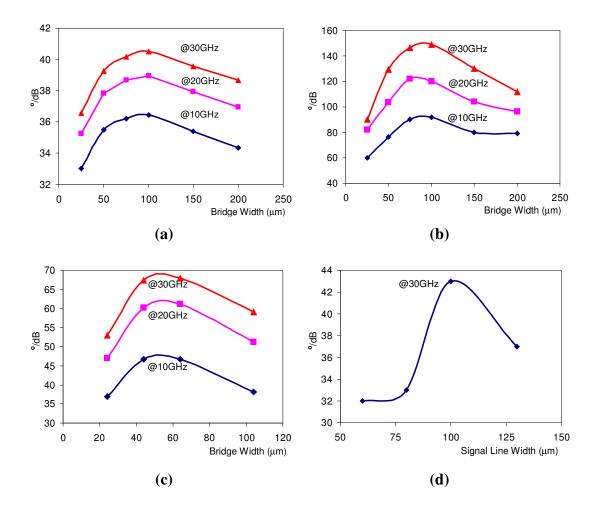

Figure 3.9 (a) Mean square error between the *CLR* model and simulation results (b)

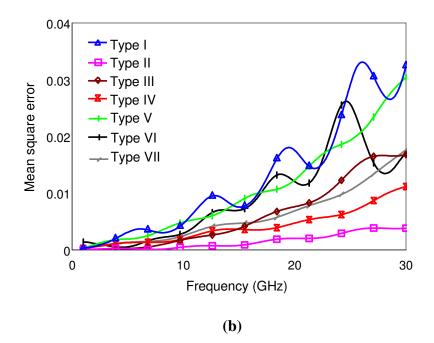

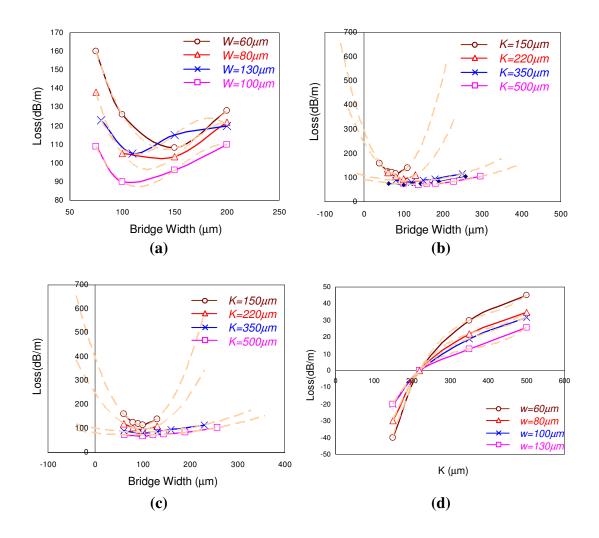

- Figure 3.10 (a) Extracted loss versus bridge width, w, for different signal line widths,

W. (b) Extracted loss values versus bridge widths for different K values. (c)

Shifted extracted loss values versus bridge widths for different K values. (d)

Extra loss plotted with respect to different K values for different signal line widths.

- Figure 3.11 (a) Low-impedance line loss distribution for K=220 μm (b) Loss difference between K=220 μm case and K=500 μm case (c) Low-impedance line loss distribution for K=500 μm (d) Low-impedance line loss distribution for K=150 μm.

- Figure 3.12 (a) EM and circuit simulation results for DMTL structure with signal line width, W=180 μm, G=20 μm, w=180 μm, h=1.7 μm and periodicity, P, is 400 μm, (b) for DMTL structure with signal line width, W=160 μm, G=30 μm w=180 μm, h=1.7 μm and P=400 μm (c) for DMTL structure with signal line

width,  $W=120 \ \mu\text{m}$ ,  $G=90 \ \mu\text{m}$ ,  $w=75 \ \mu\text{m}$ ,  $h=1.7 \ \mu\text{m}$  and  $P=400 \ \mu\text{m}$ , (d) for DMTL structure with signal line width,  $W=160 \ \mu\text{m}$ ,  $G=170 \ \mu\text{m}$ ,  $w=100 \ \mu\text{m}$ ,  $h=1.7 \ \mu\text{m}$  and  $P=400 \ \mu\text{m}$ .

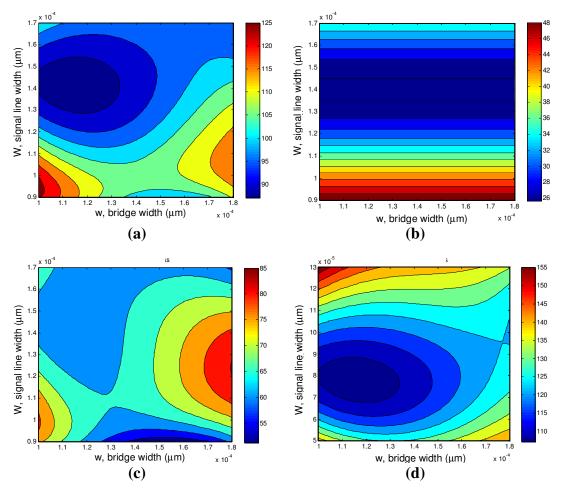

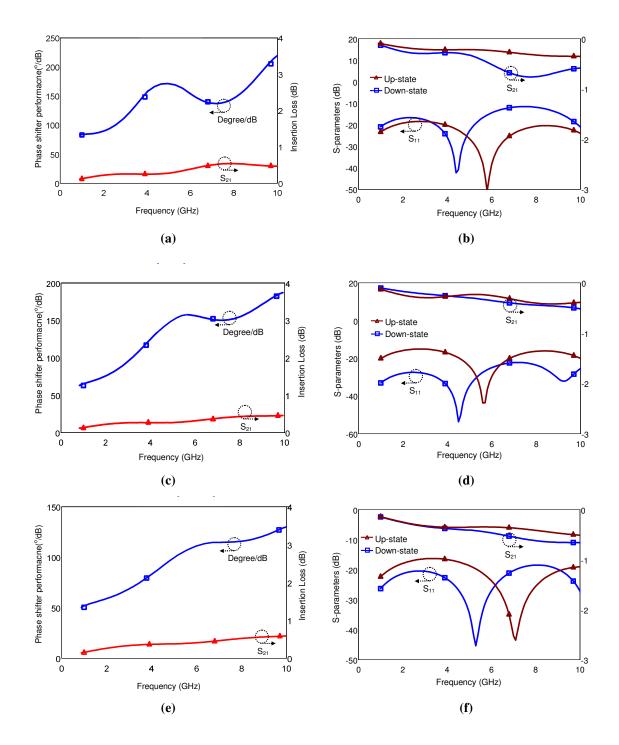

- Figure 3.13. (a) degree/dB performance for Type I DMTL when *h* is changed from 1.7 to 1.2  $\mu$ m, (b) Type III DMTL when *h* is changed from 2 to 1.2  $\mu$ m,(c) Type IV DMTL when *h* is changed from 2 to 1.7  $\mu$ m, (d) degree/dB performance variation for different signal line widths, where *K*=220  $\mu$ m and *w*= 75  $\mu$ m......57

- Figure 3.19. Open-End CPW series stub lumped element equivalent circuit model. 71

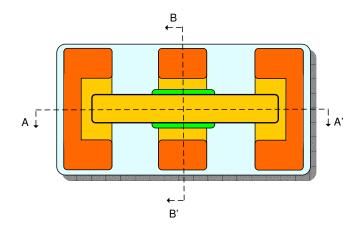

- Figure 3.21. Open-Ended CPW series stub embedded DMTL unit section snapshot74

| Figure 3.2 | 5 The simualtion results of OES inserted DMTL : (a) TYP                 | E XVIII | when |

|------------|-------------------------------------------------------------------------|---------|------|

| termi      | nated by 47 $\Omega$ , (b) TYPE XX when terminated by 50 $\Omega$ , (c) | c) TYPE | XXII |

| when       | terminated by 46 $\Omega$                                               |         | 81   |

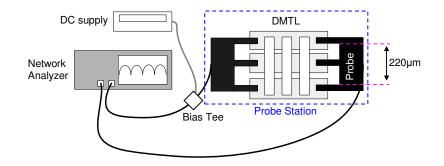

Figure 5.1 The measurement setup prepared for the DMTL structures......107

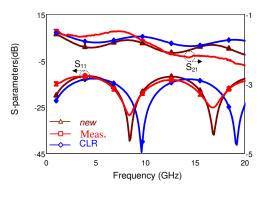

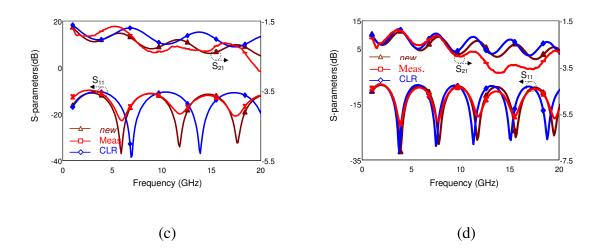

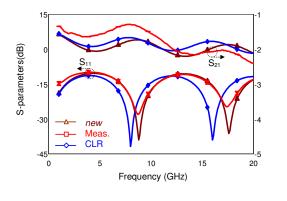

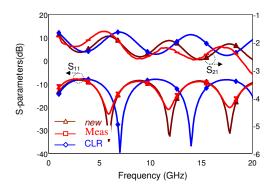

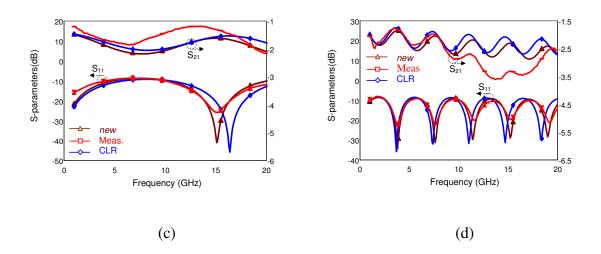

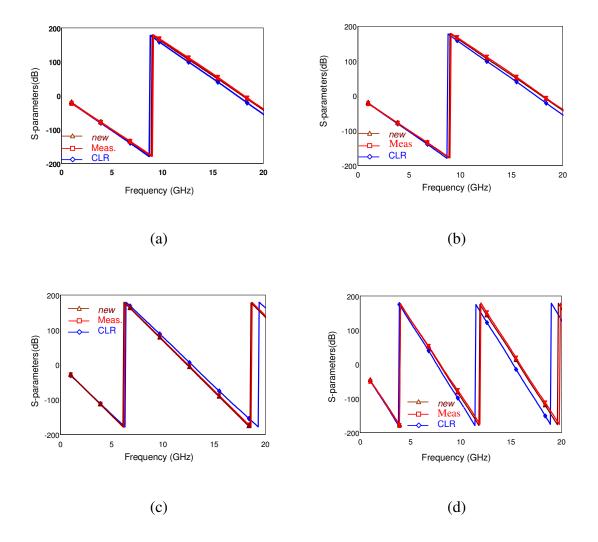

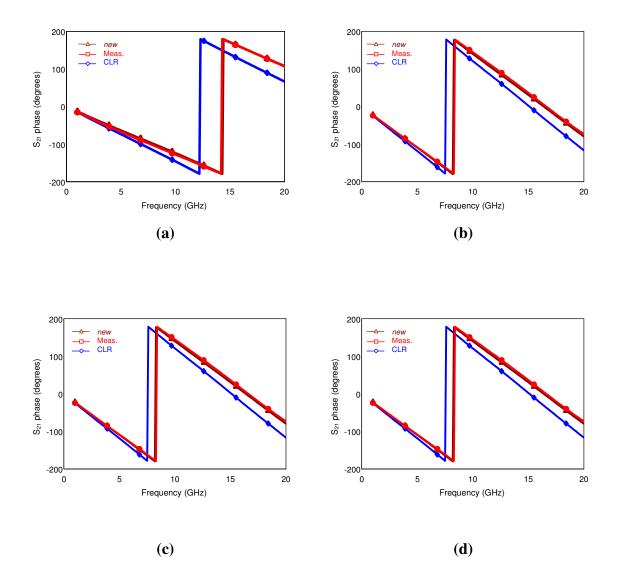

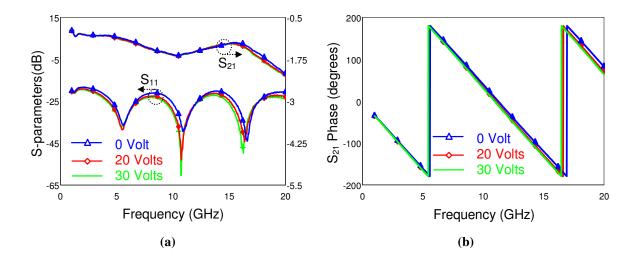

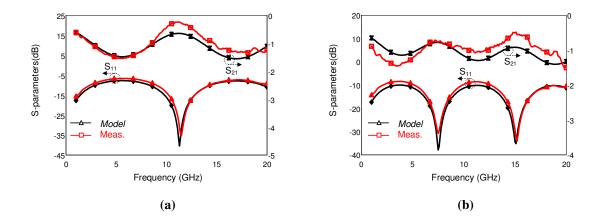

Figure 5.2 The measurement, CLR model and the new HICAPLO model results of

(a) DMTL NO 13 terminated by 40  $\Omega$ , (b) DMTL NO 14 terminated by 50  $\Omega$ ,

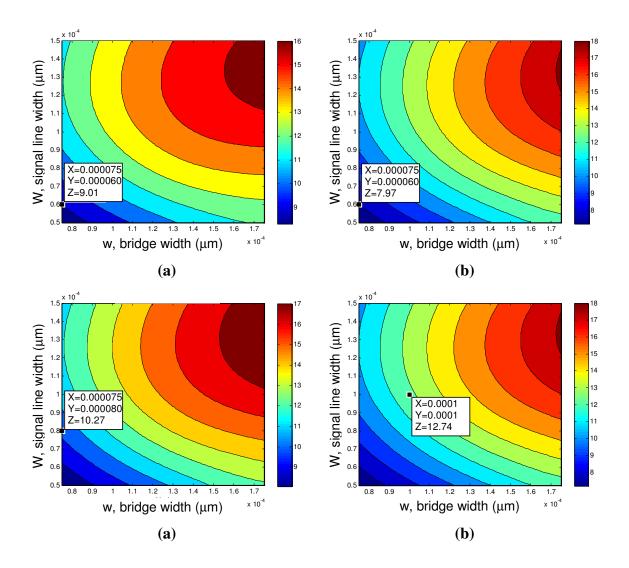

(c) DMTL NO 15 terminated by 50  $\Omega$ , and (d) DMTL NO 16 terminated Figure 5.3 The measurement, CLR model and the new HICAPLO model results of (a) DMTL NO 10 terminated by 50  $\Omega$ , (b) DMTL NO 31 terminated by 40  $\Omega$ , (c) DMTL NO 41 terminated by 50  $\Omega$ , and (d) DMTL NO 48 terminated Figure 5.4 Measurement, CLR model and the new HICAPLO model S<sub>21</sub> phase results of (a) DMTL NO 25 terminated by 50  $\Omega$ , (b) DMTL NO 26 terminated by 50  $\Omega$ , (c) DMTL NO 27 terminated by 50  $\Omega$ , and (d) DMTL NO 32 terminated Figure 5.5 Measurement, *CLR* model and the proposed model  $S_{21}$  phase results of (a) DMTL NO 45 terminated by 50  $\Omega$ , (b) DMTL NO 46 terminated by 50  $\Omega$ , (c) DMTL NO 12 terminated by 50  $\Omega$ , and (d) DMTL NO 29 terminated Figure 5.6 The measurement results of DMTL NO 43 structure for no actuation, 20 Figure 5.7 The measurement and the circuit model results of CPW transmission lines (a) for the structure with  $W = 90 \mu m$  (b) for the structure with  $W = 110 \mu m...116$ Figure 5.8 The degree/dB performance with respect to bridge width and center conductor width for (a) DMTL NO 10 with  $P=400 \mu m$ . (b) DMTL NO 12 with P= 1000  $\mu$ m. (c) DMTL NO 27 with P= 600  $\mu$ m. (d) DMTL NO 41 with

## **CHAPTER I**

## **INTRODUCTION**

The MESSENGER spacecraft is the first mission to the planet Mercury, which will achieve Mercury orbit in 2011 to look for the answers concerning the geologic history and the present conditions of the planet. The MESSENGER communication system is designed to transmit the mission science data, receive spacecraft commands from Earth, and provide high-precision navigation data. This communication between the spacecraft and the earth will be established through an antenna system, which is referred as phased array systems [1]-[2]. MESSENGER is the first deep-space mission to use phased-array antennas, which allows the spacecraft to return a large amount of data without using a deployable, gimbaled antenna.

On the other hand, it is not necessary to go to deep-space missions to find an application area for phased-array antennas. Many AM broadcast stations use these systems to enhance signal coverage in the city of license, while minimizing interference to other areas. They are also used by warships of several navies including the Japanese, Spanish, and United States' navies. Considering these and other similar applications, it will be an appropriate conclusion to state that phased-array systems are of great importance in several RF communication implementations. Therefore, the issue should be to investigate what phased-array systems are and which components they are made of.

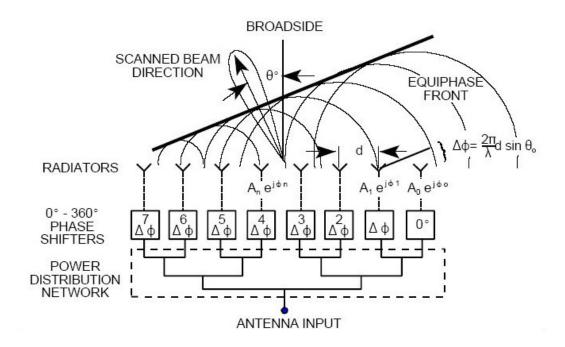

In telecommunication, a phased-array is defined as a group of antennas in which the relative phases of the respective signals feeding the antennas are varied in such a way

that the effective radiation pattern of the array is reinforced in a desired direction and suppressed in undesired directions (Figure 1.1). Therefore, the main components of a phased array system are power distributors, antennas, and some structures to change the relative phases of the respective signals. These structures are microwave phase shifters, which can be basically defined as circuit components used to change the transmission phase angle (phase of  $S_{21}$ ) of a network. While the most important application of microwave phase shifters is within a phased array antenna system, there are many other implementation areas such as instrumentation systems or wireless communication [3].

Figure 1.1 A phased-array system overview.

In this thesis it is aimed to present a complete modeling and performance improvement study on a specific type of microwave phase shifters, namely distributed micro-electro-mechanical (MEMS) transmission line (DMTL) phase shifters. The main goals of this thesis are to introduce an improved modeling approach for DMTL structures and perform an improved performance DMTL phase shifter.

This chapter presents, these objectives will be detailed and essential background information about phase shifters. Section 1.1 will give the phase shifter overview and Section 1.2 will present the thesis organization.

### **1.1. PHASE SHIFTER OVERVIEW**

The up to date phase shifters are mostly based on ferrite materials,PIN diodes,or FET switches [4]. The ferrite phase shifters are two-port components which satisfies a phase shift when the bias field of the ferrite is changed [5]. Although their performance is outstanding, their fabrication is expensive and they consume large amount of DC power. On the other hand, it is possible to built phase shifters by using switch mechanisms like PIN diodes or FET switches. Compared with ferrite phase shifters, the diode phase shifters offer small size structures and integration with planar circuitry. However, since the diodes require continuous bias current while a pulsed current is enough for ferrite devices, the DC power consumption is higher in PIN diode phase shifters. When the FET switch phase shifters are considered, it is observed that since they can be integrated with active elements on the same chip, the total assemble cost and size is reduced.

As stated previously, the phase shifting operation in the listed phase shifters currently depends on FET or PIN diode switches, when ferrite materials are eliminated because of their high power consumption. On the other hand, beside FET and PIN diode switches, RF MEMS switches have become a popular area of interest since 1995 because of the lower loss phase shifter designs they propose. Table 1.1

presents a performance comparison between the FET, PIN diode and RF MEMS switches [6]-[7], which brings the following comments:

- ⇒ The power consumption of MEMS switches is much lower than the other types of switches. This becomes a significant difference when phased-array like systems which contain a lot of switches are considered.

- ⇒ The up state capacitance is smaller in MEMS switches; therefore they can work in wider band operations.

- $\Rightarrow$  The isolation of MEMS switches is better for all frequencies up to THz.

- ⇒ Since the MEMS switch and the other RF components such as antennas can be built on the same substrate (glass, quartz, ceramic...), the overall cost of the systems reduce.

| Parameter               | RF MEMS   | PIN      | FET      |

|-------------------------|-----------|----------|----------|

| Voltage (V)             | 20-80     | 3-5      | 3-5      |

| Power Consumption (mW)  | 0.05-0.1  | 5-100    | 0.05-0.1 |

| Switching Time          | 1-300 µs  | 1-100 ns | 1-100 ns |

| C <sub>up</sub> (fF)    | 1-6       | 40-80    | 70-140   |

| Cut off Frequency (THz) | 20-80     | 1-4      | 0.5-2    |

| Isolation (1-10 GHz)    | Very high | High     | Medium   |

| Isolation (10-40 GHz)   | Very high | Medium   | Low      |

| Isolation (60-100 GHz)  | High      | Medium   | None     |

| Loss (1-100 GHz)        | 0.05-0.2  | 0.3-1.2  | 0.4-2.5  |

| C <sub>up</sub> (fF)    | 1-6       | 40-80    | 70-140   |

Table 1.1 Performance comparison of FETs, PIN diode, and RF MEMS switches.

On the other hand, RF MEMS switches have slower switching time, and lower power handling, which is in the order of 10 mWs. Because of these limitations they are not suitable for high-speed and high-power operations. However, beside these limitations, the major reasons which prevent RF MEMS switches to become the number one commercial switches are their reliability and packaging problems.

#### 1.1.1. **RF MEMS Phase Shifters**

The advantages using RF MEMS technology in switch implementation is already covered. It is also possible to observe the same advantages in RF MEMS phase shifters as Table 1.2 illustrates [7]. As it is obvious, for all the band operations, RF MEMS phase shifters result in lower loss. Therefore, any complicated structure such as communication or radar systems which get use of RF MEMS phase shifters will benefit from the loss. This benefit can be directed to a reduction in the number of amplifying stages in the overall systems. Finally, this reduction decreases the overall DC loss and cost of the system.

Table 1.2 Average on Wafer Loss for MEMS and GaAs-FET 3-bit Phase Shifters

| Frequency (GHz)    | X-Band       | Ka-Band      | V-Band       | W-Band       |

|--------------------|--------------|--------------|--------------|--------------|

| RF MEMS Loss (dB)  | -0.9 to -1.0 | -1.7 to -2.0 | -2.3 to -2.5 | -2.7 to -3.3 |

| GaAs FET Loss (dB) | -3 to -4     | -6 to -7     | -8 to -9     | -9 to -11    |

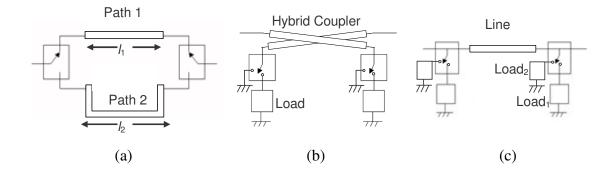

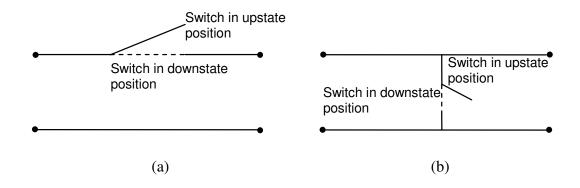

RF MEMS phase shifters, as well as PIN diode or FET phase shifters, can be examined in mainly three different types namely switched line, reflection, and loaded line, [8]-[9]. A simple switched-line RF MEMS phase shifter (Figure 1.2 (a)) is composed of two different length transmission lines  $(l_1, l_2)$  and SPDT (single pole double throw) MEMS switches, which are used to decide which path will be chosen,

[10]-[11].  $\Delta \phi = \beta (l_2 - l_1)$  is obtained as a differential phase difference between these two paths, where  $\beta$  is the propagation constant of the line. The two different length transmission lines and the corresponding switches compose a bit. It is possible to design N-bit phase shifters, which satisfies digital phase shifting, [4].

Reflection type phase shifters use hybrid couplers to divide the input signal into two signals out of phase as Figure 1.2 (b) demonstrates. These signals reflect from a pair of switched loads. The lengths of the loads are changed with the help of MEMS switches and this change modifies the phase of the reflected signal [12]-[13].

Figure 1.2 (a) Reflection phase shifter. (b) Switched-line phase shifter. (c) Loaded-line phase shifter.

The last category of phase shifter is the loaded-line phase shifter, which usually gives smaller phase shifts compared to reflection type, [14]-[15]. The study of loaded-line phase shifters began nearly half century ago and extensive analysis were executed during 1960s and 1970s [16]-[19]. In loaded-line phase shifters, the loads are connected to a transmission line such that they affect the phase of the signal significantly, while they have a small effect on the amplitude (Figure 1.2 (c)). Switching between two different loads, which are generally selected to be reactive and are shunt connected to the lines, changes the phase of the system.

#### 1.1.2. Distributed MEMS Phase Shifters

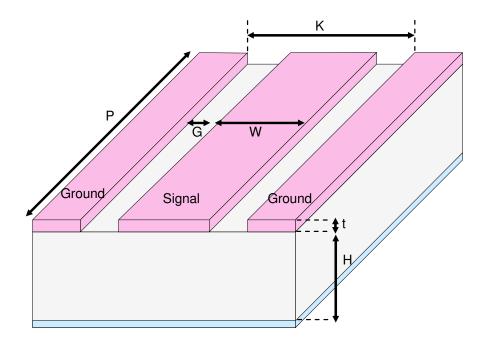

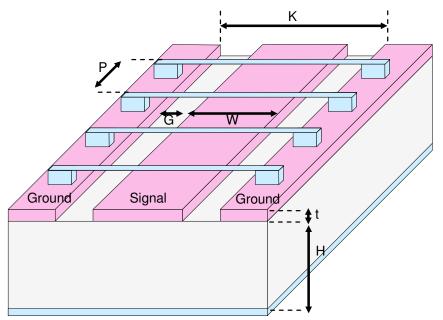

This thesis mainly studies periodically loaded-line phase shifters with MEMS switch implementation, which are referred as distributed MEMS transmission lines (DMTL) [20]-[21]. In a distributed MEMS transmission line, the loading is realized by the MEMS bridges suspending over the center conductor. These bridges satisfy shunt capacitance for the transmission line. By adjusting the height of the bridges this capacitance is changed. Figure 1.3 shows such a configuration for a CPW based structure. It is also possible to use micro-strip (MS) lines instead; however, it will bring implementation difficulties, considering via holes needed in MS lines. Free from the type of the transmission line selected, usually the characteristic impedance of the unloaded line is selected to be larger than 50  $\Omega$ , since this value will decrease as the line is loaded. The conspicuous advantages of DMTL phase shifters can be listed as follows:

- $\Rightarrow$  They can be designed using straightforward equations.

- $\Rightarrow$  They offer wideband performance.

- $\Rightarrow$  They can work well at very high frequencies.

The DMTL phase shifters can be categorized into two as analog and digital. In an analog type DMTL phase shifter, all the bridge heights are adjusted using a single bias voltage. By applying different actuations, the height of the bridges can be decreased continuously up to theoretically 2/3 of its original height, which satisfies an increase in the shunt capacitance. This brings a continuous change in phase shift amount [22] depending on the actuation voltage. In the digital distributed phase shifters, a discrete capacitor is placed in series with the MEMS bridge [23]-[26]. When there is no actuation, the effective capacitance is the up-state capacitance of the bridge. On the other hand, after actuation, the MEMS bridge is in the down-state

position and the effective capacitance becomes the discrete series capacitance. Therefore by actuation, the distributed capacitance can be digitally controlled. Many sections of digital phase shifters can with predefined phase shifts can be cascaded in order to have N-bit digital phase shifters.

Figure 1.3 Distributed MEMS transmission line (DMTL) schematic.

It is better to decide the performance of a DMTL phase shifter by considering its phase shift amount for 1 dB loss (degree/dB). Barker and Rebeiz did an optimization study on analog type distributed phase shifters [27], where they obtained an U-band design wit a performance of 50 °/dB at 20 GHz with a change of 17 % in the loading capacitance. Before Barker and Rebeiz, another optimization was done by Nagra and York using Schottky diodes [22]. Table 1.3 presents some other studies made on DMTL phase shifters.

| Freq.<br>(GHz) | Bits   | Design  | Substrate | Average<br>Loss (dB) | Return<br>Loss (dB) | Ref. |

|----------------|--------|---------|-----------|----------------------|---------------------|------|

| 13.6           | 2      | CPW     | Quartz    | -1.2                 | -12.5               | [14] |

| 16.0           | 4      | µ-strip | Silicon   | -3.0                 | -9.5                | [15] |

| 26.0           | 3      | CPW     | Glass     | -1.7                 | -7.0                | [16] |

| 37.7           | 2      | CPW     | Quartz    | -1.5                 | -11.5               | [14] |

| 60.0           | 2      | CPW     | Quartz    | -2.2                 | -10.0               | [17] |

| 94.0           | Analog | CPW     | Quartz    | -2.5                 | -11.0               | [18] |

Table 1.3 Examples of fabricated DMTL Phase Shifters.

#### 1.1.3. Previous DMTL Phase Shifter Studies at METU

The previous studies done in METU concerning DMTL phase shifters can be examined in two separate areas. First one is the initial DMTL phase shifter design, fabrication, and measurement study which was handled during the master thesis of Hüseyin Sağkol [28]. This study involves two different DMTL phase shifters: one with standard MEMS shunt bridge structure and another with T-wing type MEMS switch. The standard phase shifter is measured to give a phase shift of 15 degrees at 20 GHz when actuated by 40 volts, where the T-wing type could not be measured because of sticion problem during the release process. The result of the measured DMTL phase shifter in this thesis work is presented in Figure 1.4 (a).

The second study concerning DMTL structures is the modeling study which is finalized as in [29]. The model proposed in this study uses shunt capacitor and series inductor parameters to describe the discontinuities arise around the MEMS bridge.

Although, the model reactance parameters can not be analytical expressed, it gives better results compared with the *CLR* model as Figure 1.4 (b) points out.

Figure 1.4 (a) The measured DMTL phase shifter in the thesis work of Hüseyin Sağkol. (b) The results of the modeling study finalized in [29].

### **1.2. THESIS OBJECTIVES AND ORGANIZATION**

The main objectives of this thesis are to introduce an improved modeling approach for DMTL structures and perform an improved performance DMTL phase shifter. the specific objectives of this thesis can be listed as follows:

⇒ Improvement of the modeling studies for DMTL structures with bridge widths larger than 50 um. The *CLR* model and the previously introduced model [29] should be investigated in order to detect their deficiencies. A new and simple model which fills these deficiencies should be developed and its model parameters should be analytically expressed. This model should give very close results with the simulations and its validity should be verified by the measurements. Using this new model, a practical way to evaluate the

degree/dB performance of DMTL phase shifters should be developed in order to find the optimum performance phase shifter for a pre-defined DMTL structure before making long duration simulations.

- ⇒ Improvement of degree/dB performance of DMTL phase shifters by changing the structure topology. Coplanar Waveguide (CPW) discontinuities and their possible uses in DMTL structures should be investigated. The capacitance ratio for the up and down-states of the DMTL bridges should be increased satisfying a larger phase shift, using these discontinuities.

- ⇒ Setting a process flow for the fabrication of the designed DMTL structures in order to verify the introduced model and setting a measurement setup for the fabricated structures. The process flow developed at METU should be updated to result in a low loss and low stress structural layers. The calibration techniques for the measurement of the DMTL structures should be selected.

The thesis is organized as follows:

Chapter II introduces the background theory of the main structures mentioned in the following sections of the thesis. Coplanar waveguide (CPW) theory, RF MEMS switch theory, distributed MEMS transmission line (DMTL) theory, and DMTL phase shifter theory are explained in this chapter. This chapter also gives the details of the conductor backed and top covered CPW structures with attenuation characteristics analysis.

Chapter III describes the main design methodology of the DMTL phase shifters beginning with the modeling study. The expressions of the model parameters are extracted and the introduced model is compared with the *CLR* model and the

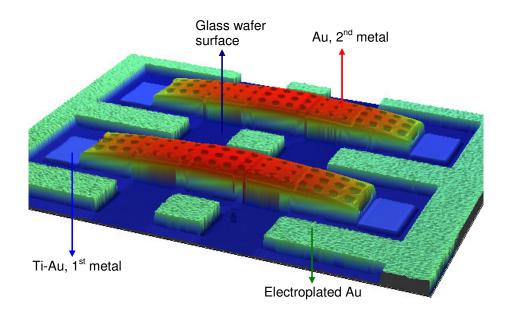

simulations. Additionally, in this chapter a MATLAB code is constructed from the introduced model ABCD parameters to evaluate the degree/dB performance of DMTL phase shifters. This chapter also presents an alternative way to improve degree/dB performance of DMTL phase shifters by inserting open-end stub CPW discontinuity through the center conductor of DMTL.

Chapter IV describes the major steps of the fabrication. Layout drawing and mask generation of the designed DMTL structures are summarized and general properties of fabrication materials and techniques are explained. SEM pictures of the fabricated structures are presented and thin-film stress observations are made in this chapter.

Chapter V presents the measurement results of the fabricated structures. The measurement setup is basically described and the measurement data are compared with the model results.

Finally, Chapter VI summarizes the research developed in this thesis, discusses the conclusions, and gives possible future works.

## **CHAPTER II**

## COPLANAR WAVEGUIDE, MEMS SWITCH AND DMTL PHASE SHIFTER THEORY

In this chapter essential basic background theory of some RF components will be resented. Section 2.1 will give the theory of coplanar waveguides, Section 2.2 will give the theory of RF MEMS switches, and Section 2.3 will give the theory of distributed MEMS transmission lines.

### 2.1. COPLANAR WAVEGUIDE THEORY

A coplanar waveguide (CPW) structure consists of a signal line centered on a dielectric substrate and separated from two ground planes by gaps as Figure 2.1 shows. This structure is first introduced by C. P. Wen in 1969 [30] and since then, it encountered several developments. Coplanar waveguides are classified as:

- ✓ Conventional CPW

- ✓ Conductor backed CPW (CBCPW)

- ✓ Micromachined CPW

The first introduced type is the conventional CPW in which the ground planes are extending to infinite, which is not possible in practice. In conductor backed CPW, there exist a ground plane covering the bottom side of the dielectric layer [31]. The micromachined CPWs are classified into two. First one is the microshield line and the second one is the CPW suspended by a silicon dioxide membrane above a micromachined groove which find detailed explanation in [32] and [33].

Coplanar waveguide structure has several advantages over the micro-strip line. The main advantage is that there is no need for via holes in CPW in spite of micro-strip lines. Therefore, series-shunt element mounting and fabrication is easier with CPW technology. As a second advantage, in CPW, the characteristic impedance ratio depends on only W/G ratio. This enables a reduction in CPW circuit size by lowering W and G values. Moreover, in CPW structures, the ground planes cover signal lines from both sides, which mostly eliminates the cross talk effects between two signal lines are mostly eliminated. Considering these advantages, it is obvious that CPW is suitable for both MIC and MMIC applications [30].

Figure 2.1 Coplanar Waveguide schematic.

#### 2.1.1. Conductor Backed Coplanar Waveguide (CBCPW)

As mentioned in the previous section, there exists a ground plane covering the bottom side of the dielectric layer in CBCPW. This additional ground plane mechanically supports the substrate and operates as a heat sink for active device circuits. Moreover, it is advantageous to have such a ground plane at the bottom when CPW and micro-strip structures are designed to be built on the same substrate. The main parameters which are determined from the CPW dimensions are the characteristic impedance and the effective permittivity of CPW. These parameters are defined by (2.1)-(2.4) [34]-[35].

$$\varepsilon_{eff,H-CLR} = \frac{1 + \varepsilon_r \frac{K(k')}{K(k)} \frac{K(k_3)}{K(k_3)}}{1 + \frac{K(k')}{K(k)} \frac{K(k_3)}{K(k_3)}}$$

(2.1)

where *K* is the elliptic integral of the first order.

$$Z_{H,CLR} = \frac{60\pi}{\sqrt{\mathcal{E}_{eff,H-CLR}}} \frac{1}{\left(\frac{K(k)}{K(k')} + \frac{K(k_3)}{K(k'_3)}\right)}$$

(2.2)

$$k = W / K \qquad k_3 = \frac{\tanh(\pi W / 2H)}{\tanh(\pi K / 2H)}$$

(2.3)

$$k' = \sqrt{1 - k^2}$$

$k'_3 = \sqrt{1 - k_3^2}$  (2.4)

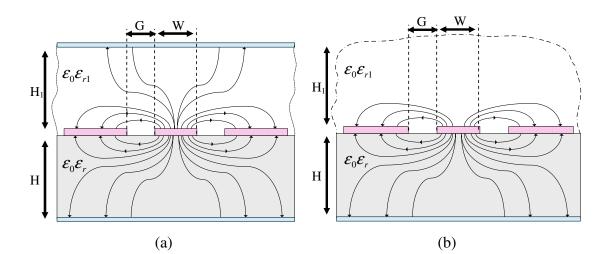

#### 2.1.2. CBCPW Analysis in the Presence of a Top Metal Cover

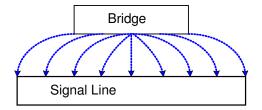

The CBCPW structure can be used with a metal top cover over the signal and ground lines, which brings extra fields in the solution region as Figure 2.2 illustrates. With this configuration, basically four different situations [36] arise as a result of the variations in the height of the top metal,  $H_1$  and the gap distance, G. The top metal height,  $H_1$  is comparable with the substrate thickness, H and the ground planes are not at a very far distance from the center conductor in the first situation. With this configuration the structure shows the properties of a CBCPW with a top cover. Different from this case, in the second situation, the top cover height is much larger than the substrate height, which makes the structure behave as a simple CBCPW. The third situation is similar to the first situation, this time the ground planes are at a far distance from the center conductor, making G value increase. When this G value exceeds a limit, the fields in the solution region show the characteristics of a microstrip line rather than a CPW. Therefore, for this situation the case resembles like a shielded micro strip line. Finally, the last situation differs from the third one by the increase in the height of the top cover, which converges to a simple micro strip line structure. For the topics covered in this thesis, the last case will be of great importance.

Since the last case resembles micro strip line, it will be a good approximation to use the micro-strip line equations to evaluate the characteristic impedance and the effective permittivity of this case as given in equations (2.5)-(2.7).

Figure 2.2 CBCPW with top cover limiting cases.

$$\varepsilon_{eff,L} = \frac{(\varepsilon_r + 1)}{2} + \frac{(\varepsilon_r - 1)}{2}F - \frac{(\varepsilon_r - 1)}{\varepsilon_{r1}}\frac{t}{h\sqrt{W/h}}$$

(2.5)

$$Z_{0} = \frac{120\pi}{\sqrt{\varepsilon_{eff,L}} \left(\frac{\chi}{h} + 1.393 + 0.667 \ln\left(\frac{\chi}{h} + 1.444\right)\right)}$$

(2.6)

$$\chi = h \left( \frac{W}{h} + \frac{1.25t(1 + \ln 2h/t)}{\pi h} \right)$$

(2.7)

For this last case, it is stated that the back conductor is closer to the signal line compared to the top cover. On the other hand, if the top cover gets much closer to the signal line compared to the back conductor, the line again behaves as a micro strip line. However, this time  $\varepsilon_r$  and  $\varepsilon_{r1}$  should be interchanged in equation (2.5). Moreover, if the second dielectric is air, i.e. the top cover is suspending in the air,  $\varepsilon_{r1}$  becomes unity and so does  $\varepsilon_{eff,L}$ .

### 2.1.3. Attenuation Characteristics of CPW

The total CPW attenuation can be defined as the attenuation due to the dielectric losses in the substrate and the attenuation due to the conductor losses in the center conductor, ground planes and the bottom conductor [30].

$$\alpha_{H} = \alpha_{C} + \alpha_{D} \tag{2.8}$$

The attenuation due to the dielectric loss can be defined as:

$$\alpha_{D} = \frac{8.686\pi f}{c} \frac{\varepsilon_{r}}{\sqrt{\varepsilon_{eff,H}}} \tan \delta_{e} q \, \mathrm{dB/m}$$

(2.9)

where  $\tan \delta_e$  is the loss tangent of the substrate and q is defined as:

$$q = \frac{K(k_1)K(k')}{2K(k_1)K(k)}$$

(2.10)

On the other hand, the attenuation due to the conductor losses is expressed as:

$$\alpha_c = 8.686 \frac{R_c + R_G}{2Z_H} \, dB/m \tag{2.11}$$

where,  $R_C$  is the series resistance of the center conductor and  $R_G$  is the distributed series resistance of the ground planes in ohms per unit length.

$$R_{c} = \frac{R_{s}}{4W(1-k^{2})K^{2}(k)} \left(\pi + \ln(4\pi W/t) - k\ln\frac{1+k}{1-k}\right)$$

(2.12)

$$R_{G} = \frac{kR_{S}}{4W(1-k^{2})K^{2}(k)} \left(\pi + \ln(4\pi K/t) - \frac{1}{k}\ln\frac{1+k}{1-k}\right)$$

(2.13)

$$k_{1} = \frac{\sinh(\pi W / 4H)}{\sinh(\pi K / 4H)} \qquad k_{1} = \sqrt{1 - k_{1}^{2}}$$

(2.14)

$$R_s = \frac{1}{\delta\sigma} \ \Omega \quad \delta = \sqrt{\frac{2}{\omega\mu\sigma}} \ \mathrm{m}$$

(2.15)

here,  $R_s$  is the skin effect surface resistance,  $\sigma$  is the conductivity of the conductor and  $\delta$  is the skin dept [37].

### 2.2. RF MEMS SWITCH THEORY

A switch is a device which allows signal transmission in one position and prevents it in the other. RF MEMS switches satisfy this operation at RF to millimeter wave frequencies with the help of mechanical movement and by achieving short or open circuits in the RF transmission line [38]. This movement is mostly realized by electrostatic, magnetic, piezoelectric or thermal actuators. RF MEMS switches have advantages over the other types of switches namely pin diode or FET switches. These advantages are: low power consumption, very high isolation, very low insertion loss, and low cost. On the other hand, they also have disadvantages like low switching speed, low power handling, and high voltage drive. Moreover, packaging difficulty, reliability and the overall cost after packaging are the other issues which can be counted as the drawbacks of RF MEMS switches.

Although, there are several ways to achieve a mechanical movement, the most common way is the voltage actuation [38]. Voltage actuation depends on the idea of creating a voltage difference between the bridge and the bias electrode. Therefore, a downwards electrostatic force will occur between the bridge and the electrode which can be expressed as:

$$F_{electostatic} = \frac{1}{2} \varepsilon_0 A E^2 = \frac{\varepsilon_0 A V^2}{2 \left(g + \frac{t_d}{\varepsilon_{rd}}\right)^2}$$

Nt (2.16)

where, A is the area of the intersection area of the bridge and the electrode, V is the voltage and g is the gap distance between the bridge and the electrode,  $t_d$  is the thickness and  $\varepsilon_{rd}$  is the relative permittivity of the dielectric layer on top of the electrode (Figure 2.4).

On the other hand, as a result of the deflection of the bridge an upwards force coming from the spring constant of the bridge arises as (2.17) expresses. Here,  $g_0$  is the original gap distance before actuation and k is the spring constant.

$$F_{spring} = -k(g_0 - g) \text{ Nt}$$

(2.17)

For, stability these two forces should be in equilibrium. When the downwards force gets sufficiently larger, the bridge collapses on the electrode. This situation becomes possible when the bridge is deflected to make the gap 2/3 of its original position [38]. Therefore, if the expressions for the two forces are equated and the *g* is taken as  $2g_0/3$ , the pull-down voltage can be found as in (2.18). Below this pull-down voltage, the bridge continues to bend, whereas above this value it collapses.

$$V_{pull-down} = \sqrt{\frac{8kg_0^3}{27\varepsilon_0 A}} \text{ Volts}$$

(2.18)

As previously mentioned, long switching time is one of the disadvantages of RF MEMS switches. The expression for the switching time is found from nonlinear dynamic analysis of MEMS beams and expressed as [38]:

$$t = 3.67 \frac{V_{pull-down}}{V_s \omega_0} \text{ seconds}$$

(2.19)

where  $V_S$  is the applied voltage. As the limitations on  $V_S$  and the resonant frequency are considered, it is expected that the practical switching time will be about 1  $\mu$ s.

There are two types of switches used in RF MEMS applications, namely series and shunt switch. The series switch enables a path for the signal when it is actuated (down-state position). When no bias is applied, it behaves as an open circuit as Figure 2.3 (a) illustrates. The shunt switch, conversely, allows the signal to pass through the transmission line when there is no actuation and the switch is in the upstate position. When a bias is applied, it connects the signal line to the ground and prevents the signal to reach to the other side of the transmission line. More detailed discussions about RF MEMS shunt switches will be presented in the next sections.

Figure 2.3 Schematic of (a) series switch (b) shunt switch.

### 2.2.1. RF MEMS Shunt Switch

The switch configuration that will be explained in this section is CPW RF MEMS shunt switch, which Figure 2.4 illustrates. Here, the bridge is suspending over the center conductor (signal line) and it is connected to ground planes on two sides.

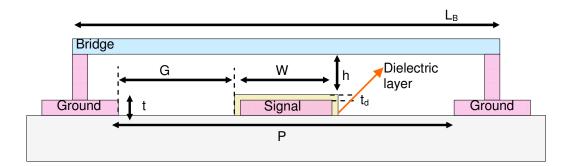

Figure 2.4 Side view of RF MEMS shunt switch with bridge anchors are connected to ground planes.

The actuation points for this configuration are the ground planes and the signal line; therefore, when a bias is applied, there will be a potential difference between the bridge and the signal line. As a result of this difference, an electrostatic force occurs, which pulls the bridge down. The change in the position of the bridge causes a change in the amount of parallel plate capacitance between the signal line and the ground. When the applied voltage reaches and exceeds the pull-down voltage, the bridge collapses, which increases this parallel plate capacitance significantly. By this way, the signal going on the center conductor finds a low-impedance path to ground.

### 2.2.1.1. RF MEMS Shunt Switch Circuit Model (The CLR Model)

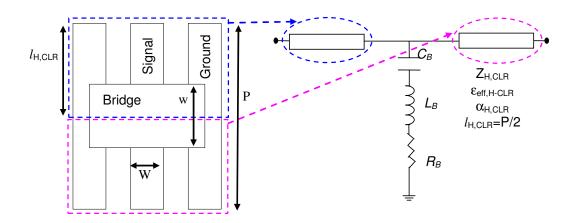

The top view and the *CLR* lumped model of the shunt switch is presented in Figure 2.5. As the figure reveals, the switch is modeled as two transmission lines and the *CLR* representation of the bridge [7]. The transmission lines are of P/2 length where the other parameters of these lines are calculated using the standard CPW transmission line equations (2.1)-(2.4).

Figure 2.5 Top view of a shunt switch and its lumped element model.

From this *CLR* model the overall impedance of the switch can be driven as:

$$Z_{s} = R_{B} + j\omega L_{B} + \frac{1}{j\omega C_{B}}$$

(2.20)

From this equality, it is obvious that  $Z_S$  can be approximated as follows for different frequency ranges:

$$Z_{S} = \begin{cases} \frac{1}{j\omega C_{B}} & \text{for} \quad f \ll f_{0} \\ R_{B} & \text{for} \quad f = f_{0} \\ j\omega L_{B} & \text{for} \quad f \gg f_{0} \end{cases}$$

(2.21)

where,

$$f_0 = \frac{1}{2\pi \sqrt{L_B C_B}}$$

(2.22)

From the overall impedance expression, the cut off frequency, which is defined as the frequency at which the up and down-state impedance ratio is one [7], can be evaluated as:

$$f_{C} = \frac{1}{2\pi C_{B_{-}up}R_{B}}$$

(2.23)

where,  $C_{B_{-}up}$  is the up-state parallel plate capacitance. This cut off frequency determines the RF performance of a switch and it is in the order of 10-100 THz for RF MEMS switches.

### 2.2.1.2. RF MEMS Shunt Switch Electromagnetic Model

The defined parameters of the CLR model are extracted using some techniques which will be covered in this section. To begin with, the parallel plate capacitance when the bridge is in the up-state position is simply evaluated by:

$$C_{B_{-up}} = \varepsilon_0 \frac{wW}{h + t_d / \varepsilon_{rd}}$$

(2.24)

This value is the sum of the capacitance of the air and the capacitance of the dielectric layer, which where w, W, h, and  $t_d$  are defined in Figure 2.4. For down-state position, the expression is shorter since the capacitance through the air is eliminated.

$$C_{B_{-}down} = \varepsilon_0 \frac{\varepsilon_{rd} wW}{t_d}$$

(2.25)

As opposed to the capacitance expressions, the resistance,  $R_B$  and the inductance,  $L_B$  do not have accurate formulas. Instead, they are modeled using numerical electromagnetic techniques [7]. Even though it can not be formulated, the inductance can be stated to depend on the part of the bridge which is on the gaps. Since the current distribution is mostly concentrated about the edges of the conductors. On the other hand, the resistance can be expressed as a sum of two components, which arise due to the transmission line loss and the bridge loss, [7]. The part which is due to the transmission line loss is evaluated using the expression:

$$R_{B_{TL}} = 2Z_0 l \alpha$$

, where  $\alpha$  is the line loss in Np/m (2.26)

The resistance due to the bridge needs a more complicated evaluation process which will not be detailed here but can be found in [7].

After the electromagnetic modeling parameters are defined, what should be determined is the loss of the RF MEMS switch. It should be noted that the loss can not be expressed by  $|S_{21}|^2$  alone, since it is only the insertion loss. However, what prevents the transmission of all the power to the other side of the line is the effect of both the insertion loss and the reflection. Therefore, the overall loss can be expressed as [7]:

$$Loss = 1 - |S_{11}|^2 - |S_{21}|^2$$

(2.27)

For the up-state position where, the switch is not touching the signal line, the reflection coefficient can be given as:

$$S_{11} = \frac{-jC_{B_{up}}Z_0}{2+j\omega C_{B_{up}}Z_0} \qquad |S_{11}|^2 = \frac{\omega^2 C_{B_{up}}Z_0}{4} \qquad (2.28)$$

which enables a direct calculation of up-state capacitance value. The second identity in equation (2.28) is found by assuming that  $S_{11}$  is much smaller than -10dB or  $\omega C_{B_{-}up}Z_0$  is much smaller than 2. For the down-state, the isolation, which can be defined as the amount of signal transferred from one port to the other when the signal line is shorted to ground, is found by:

$$S_{21} = \frac{1}{1 + j\omega C_{B_{down}} Z_0 / 2} \qquad |S_{21}|^2 = \begin{cases} \frac{4}{\omega^2 C_{B_{down}}^2 Z_0^2} & \text{for} & f \ll f_0 \\ \frac{4R_B^2}{Z_0^2} & \text{for} & f = f_0 \\ \frac{4\omega^2 L_B^2}{Z_0^2} & \text{for} & f \gg f_0 \end{cases}$$

(2.29)

### 2.3. DISTIBUTED MEMS TRANSMISSION LINE THEORY

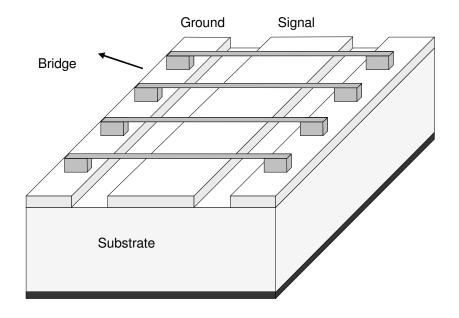

A transmission line can be loaded placing periodically spaced capacitive elements on it. In a distributed MEMS transmission line, this loading can be realized by the MEMS bridges suspending over the center conductor. Figure 2.6 shows such a configuration for a CPW based structure. It is also possible to use micro-strip lines instead; however, it will be difficult to implement since via holes are needed in micro-strip lines. Whatever the type of the transmission line selected, usually the characteristic impedance of the unloaded line is selected to be larger than 50  $\Omega$ , since the characteristic impedance of the line will decrease as it is loaded [39]. Therefore, if the loading is adjusted properly, the loaded line can have about 50  $\Omega$  characteristic impedance, which will match the 50  $\Omega$  feedings.

Figure 2.6 Distributed MEMS transmission line (DMTL) schematic

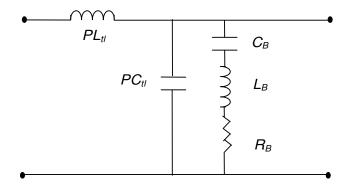

Figure 2.7 presents the lumped equivalent model of the unit length DMTL. Here, the  $L_{tl}$  and  $C_{tl}$  stand for per unit length inductance and capacitance of the unloaded line and P is the spacing between the consecutive MEMS bridges. (2.30) gives the

expressions for per unit length inductance and capacitance, where (2.31) defines the relation between the loaded line impedance and the model parameters.

Figure 2.7 Lumped element transmission line model of the unit length DMTL

$$C_{tl} = \sqrt{\frac{\varepsilon_{eff,H}}{cZ_0}} \qquad \qquad L_{tl} = C_{tl}Z_0^2 \qquad (2.30)$$

$$Z_{loaded} = \sqrt{\frac{PL_{tl}}{PC_{tl} + C_B}} \sqrt{1 - \left(\frac{\omega}{\omega_B}\right)^2}$$

(2.31)

The discontinuities that arise due to the periodic loading of capacitive bridges create reflections. In other words, each capacitor causes a reflection while the signal propagates through the transmission line. At a certain frequency the reflected and the incident signals interfere destructively, which prevents the transmission of the signal to the other port. This frequency is defined as the Bragg frequency (2.32) and acts as a cut off point for DMTL structures [39].

$$\omega_{B} = \frac{2}{\sqrt{PL_{tl}(PC_{tl} + C_{B})}}$$

(2.32)

The operating frequency of a DMTL structure must be smaller than the Bragg frequency in order to satisfy a power transfer. At the Bragg frequency, the loaded

line impedance,  $Z_{loaded}$  becomes zero as (2.31) predicts. When the operating frequency is much smaller than  $\omega_B$ , the loaded line impedance becomes:

$$Z_{loaded} = \sqrt{\frac{PL_{tl}}{PC_{tl} + C_B}}$$

(2.33)

On the other hand, from time delay calculations; it is possible to find the effective dielectric constant of the loaded line as [7]:

$$\sqrt{\varepsilon_{eff,loaded}} = \frac{c\sqrt{PL_{ll}(sC_{ll} + C_{u})}}{P} = \frac{2c}{P\omega_{B}}$$

(2.34)

where c is the speed of the light in m/s.

When the line is loaded, the loss of the line differs from. The overall loss for a loaded transmission line can be shown to be [7]:

$$\alpha_{loaded\_line} = \frac{R_{ll}}{2Z_{loaded}} + \frac{G_{ll}Z_{loaded}}{2}$$

(2.35)

where, the first term accounts for the transmission line conductor losses and the second term represents the dielectric losses. Here,  $R_{tl}$  is a series resistance and  $G_{tl}$  is a shunt admittance which are used together with  $L_{tl}$  and  $C_{tl}$  to represent the per unit length loaded transmission line. On low loss substrates, the dielectric loss can be ignored and equation 2.35 simplifies to  $R_{tl} / 2Z_{loaded}$ . As it is seen, the loss is inversely proportional to the loaded line impedance. The bridge itself also adds a loss which is due to the  $R_B$  value and can be expressed as:

$$\alpha_{Bridge} = \frac{R_B Z_{loaded} \omega^2 C_B}{2}$$

(2.36)

The transmission line loss and the bridge loss together form the overall loss per section of a DMTL:

$$\alpha_{loaded} = \frac{R_{tl}}{2Z_{loaded}} + \frac{R_B Z_{loaded} \omega^2 C_B}{2}$$

(2.37)

### 2.3.1. DMTL Phase Shifters

A distributed line phase shifter consists of a high impedance  $\geq 50 \Omega$ , line which is loaded by the periodic placement of capacitors. By actuating the switches, their height changes, which directly changes the capacitance and the phase velocity. This phase velocity change satisfies a phase shift, which is the main idea behind DMTL phase shifters. The phase shift per unit length in DMTL phase shifters is found as:

$$\Delta \phi = \beta_1 - \beta_2 = \omega \left(\frac{1}{\nu_1} - \frac{1}{\nu_2}\right) = \frac{\omega Z_o \sqrt{\varepsilon_{eff}}}{c} \left(\frac{1}{Z_{lu}} - \frac{1}{Z_{ld}}\right) \text{rad/m}$$

(2.38)

where,  $\varepsilon_{eff}$  is the effective permittivity of the unloaded line formulated in (2.1),  $Z_{lu}$ and  $Z_{ld}$  represents the loaded line impedances for up and down-states of the bridges, respectively, and  $v_1$  and  $v_2$  accounts for the phase velocities of up and down-states. Although this equation gives the phase shift amount, this quantity is not enough to decide the performance of a DMTL phase shifter. A commonly excepted performance criterion for DMTL phase shifters is the ratio of the phase shift to the insertion loss. This criterion was first introduced by Rodwell et al. [40]-[41] and Nagra et al. [42]. Since the amount of the phase shift is formulated, what is left for the evaluation of the degree/dB performance is the loss. The loaded line loss is inversely proportional to the characteristic impedance of line as explained in the previous section. By using (2.39), which is the open form of (2.8), the unloaded line loss can be calculated and (2.46)can be used as the relation between the unloaded line loss and loaded line loss. With the defined equations for the loss and the phase shift, it is possible to find the degree/dB performance of a DMTL phase shifter.

$$\alpha_{unloaded} = \beta \frac{8.686 \times 10^{-2} R_s \sqrt{\varepsilon_{r,eff}}}{4\eta_0 GK(k) K(k')(1-k^2)} \times \frac{2K}{W} \times \left(\pi + \ln\left(\frac{4\pi W(1-k)}{t(1+k)}\right)\right) + 2\left(\pi + \ln\left(\frac{4\pi S(1-k)}{t(1+k)}\right)\right) dB/cm$$

(2.39)

$$Z_{loaded} Z_{unloaded} = \alpha_{loaded} \alpha_{unloaded}$$

(2.40)

The performance optimization can be extended by following the method in [43]. The main principle behind this method depends on relating the input reflection coefficient to the loaded line impedance of the DMTL structure, as will be explained next.

The input impedance of a terminated lossless transmission line (Figure 2.8) is given by [44] as:

$$Z_{in} = Z_{loaded} \frac{Z_T + jZ_{loaded} \tan \beta \ell}{Z_{loaded} + jZ_T \tan \beta \ell}$$

(2.41)

Where,  $Z_T$  is the termination impedance and  $\ell$  is the length of the DMTL. Hayden [43] uses quarter wavelength DMTLs ( $\ell = \lambda/4$ ) in the rest of the analysis; however

in this thesis study the length will be left as a parameter. Input reflection coefficient and the return loss are defined as:

$$\Gamma_{in} = \frac{Z_{in} - Z_S}{Z_{in} + Z_S} \qquad RL = 20\log(\Gamma_{in}) \qquad (2.42)$$

The relation between the input impedance and the return loss (RL) is obtained by combining (2.41) and (2.42) as:

$$Z_{in} = Z_s \frac{1 + 10^{RL/20}}{1 - 10^{RL/20}} = Z_{loaded} \frac{Z_T + jZ_{loaded} \tan \beta \ell}{Z_{loaded} + jZ_T \tan \beta \ell}$$

(2.43)

In a 50  $\Omega$  system, such as  $Z_T=Z_S=50 \Omega$ , (2.43) reduces into:

$$50\frac{1+10^{RL/20}}{1-10^{RL/20}} = Z_{loaded} \frac{50+jZ_{loaded}\tan\beta\ell}{Z_{loaded}+j50\tan\beta\ell}$$

(2.44)

Figure 2.8 A DMTL phase shifter placed in a terminated circuit system.

The positive root of (2.44) is found to be:

$$Z_{loaded} = \frac{j50}{\tan\beta\ell(10^{RL/20} - 1)} \left( 10^{RL/20} + \sqrt{10^{RL/10} + (\tan\beta\ell)^2 (10^{RL/10} - 1)} \right)$$

(2.45)

To illustrate the use of this formulation, a specific case can be examined. For instance, when the maximum return loss is selected to be -30 dB and the length is selected as 4 mm, which is 0.67 guided wavelength at 30 GHz, the loaded line impedance is evaluated as  $51.6\Omega$ . For a DMTL phase shifter, there are two states, namely up and down-states. The relation between the loaded line impedance of these states in a 50  $\Omega$  system can be chosen as:

$$(50)^2 = Z_{lu} Z_{ld} \tag{2.46}$$

Therefore, if the upstate impedance is found as 51.6  $\Omega$  for the above example, then from (2.46), the down-state impedance should be 48.5  $\Omega$ . For these values, the input reflection coefficient is 0.031. If the maximum return loss is selected to be -15 dB instead of -30 dB, then the up and down-state characteristic impedances will be 59.5 and 42.1  $\Omega$  respectively, and the reflection coefficient will be 0.1778. Since the difference between the loaded line impedances is larger in the second case, the amount of phase shift will also be larger. However, the main drawback of this situation is the increase in the reflection coefficient.

### **CHAPTER III**

# DMTL PHASE SHIFTER DESIGN, MODELING AND STRUCTURAL IMPROVEMENT

The implementation of DMTL employs the idea of periodically loading a high-impedance coplanar waveguide (CPW) with reactive loading elements. DMTL's are generally used as phase shifters, which are of great importance in many microwave applications. This thesis mainly studies the performance improvement of DMTL phase shifters. In this chapter, beside performance improvement techniques, an innovative DMTL unit section modeling method is introduced. Section 3.1 will give the details of the modeling studies, Section 3.2 will present the optimum DMTL phase shifter design, and Section 3.3 will present the analysis of open-ended stub embedded DMTL phase shifters.

### 3.1. DISTRIBUTED MEMS TRANSMISSION LINE MODELING

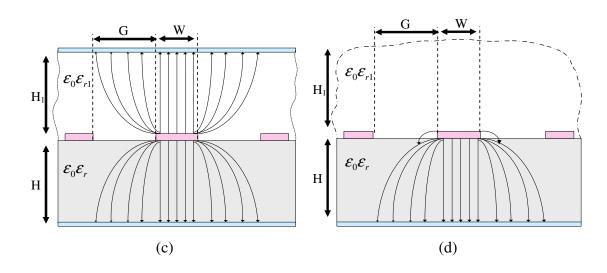

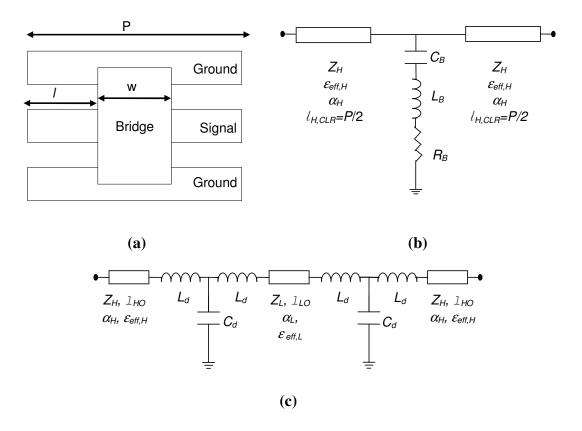

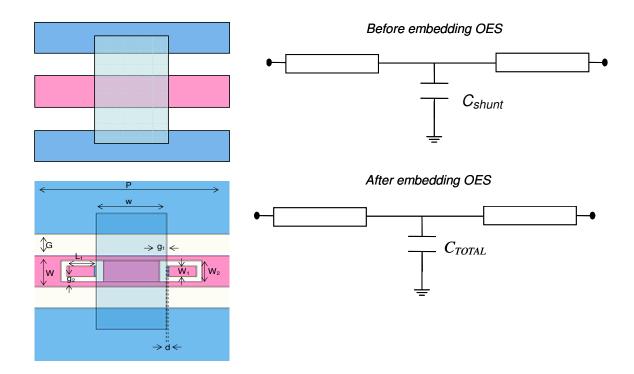

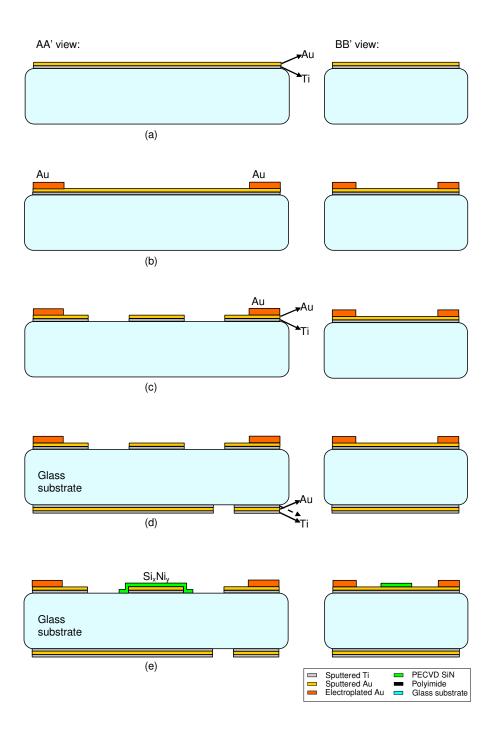

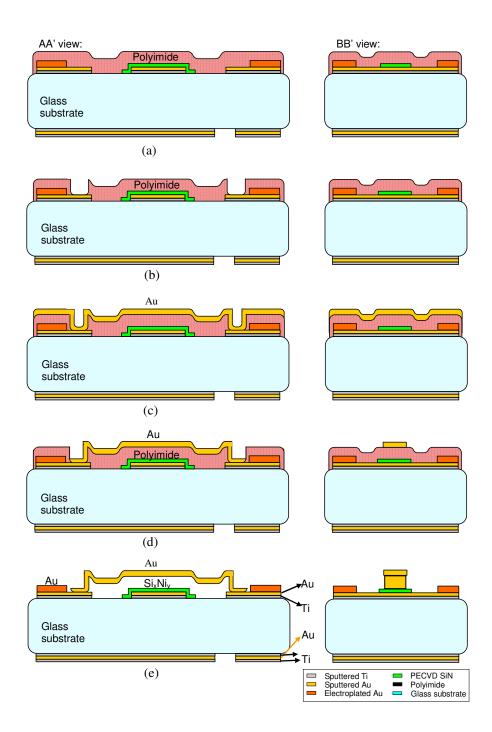

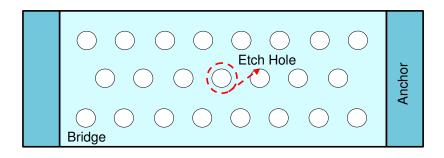

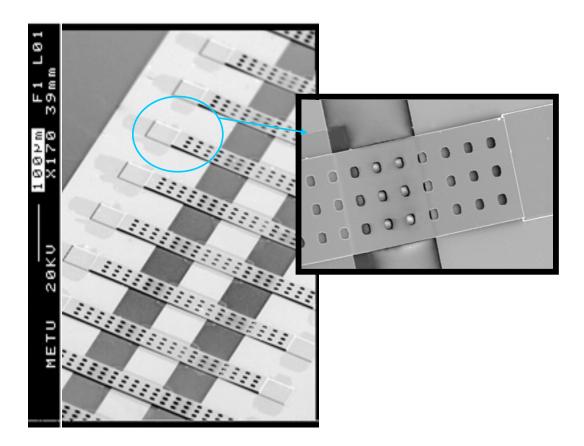

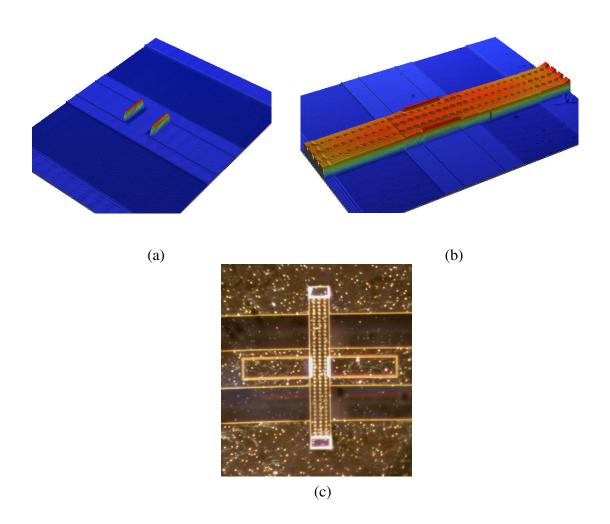

Accurate modeling of DMTL is beneficial in order to reduce the computational time and efforts. The most common and applicable model for unit DMTL is the fundamental *CLR* model where the suspended bridge structure is simply represented as a shunt capacitance to ground, which loads the high impedance transmission line [45] as Figure 3.1 shows and CHAPTER II explains (b). The major claim of the *CLR* model is its ability to represent all the DMTL unit sections, without a limitation on the dimensions of the structures. However, the *CLR* model is discussed to be capable of modeling up to a bridge width of 50  $\mu$ m and a new modeling approach has been proposed in order to span all the bridge widths [29]. This approach models the DMTL unit section as two high impedance transmission lines and a low impedance transmission line in between, where the discontinuities are represented as capacitors and inductors as shown in Figure 3.1 (c). Although this approach works well, there is a main drawback that analytical expressions for capacitor and inductor values can not be obtained, limiting the practical usage of the model. In other words, the approach is well-suited for analyzing previously simulated or measured structure; however, it can not give an idea about the response of the DMTL structure by just using the proposed circuit model without performing any simulations or measurements. Therefore there is still a requirement for a new approach which is capable of not only analyzing a DMTL but also synthesizing it.

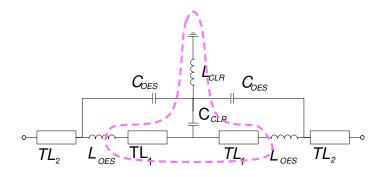

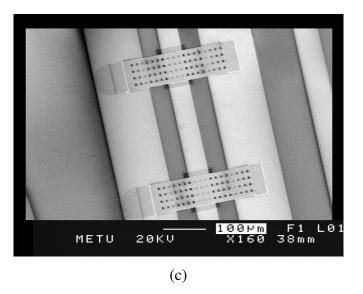

This chapter introduces a new model (HICAPLO model) with analytical expression to completely model and synthesize a DMTL structure. As an improvement to the previously presented modeling approach, the discontinuity inductances are eliminated, which can only be evaluated numerically in the previous approach. The removal of the inductances is compensated by a systematic modification of the length of the high- and low-impedance transmission lines in the circuit model. The remaining parameter is the value of the discontinuity capacitance. This capacitance is calculated by a parallel plate capacitance formulation including fringes.

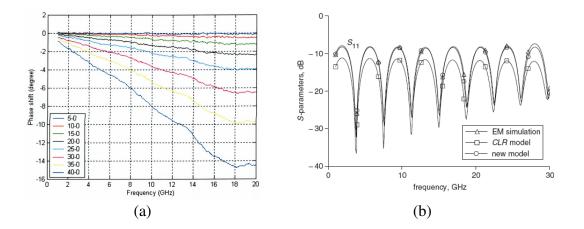

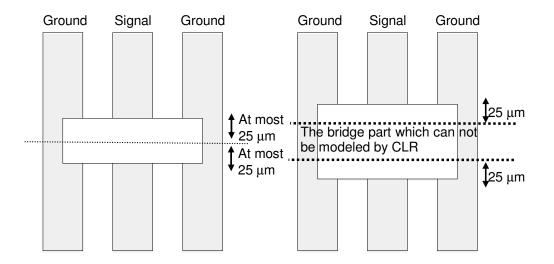

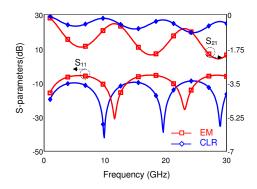

On the other hand, the reduction of the number of components the degree of freedom of the model. While the scope of the *CLR* model is up to 50  $\mu$ m bridge width, the model presented in this work deals with DMTLs having bridge width larger than 50  $\mu$ m. Although, the proposed HICAPLO model shows best operational performance for bridge widths between 50  $\mu$ m and 100  $\mu$ m, it is shown that for bridge widths larger than 200  $\mu$ m, the proposed model still works better than the *CLR* model. To give an idea about the performance of the *CLR* model for bridge widths larger than 50  $\mu$ m, in Figure 3.3, the S-parameters obtained after the EM simulations and *CLR* modeling of a DMTL structure with bridge width 230  $\mu$ m and signal line width 225  $\mu$ m is presented.

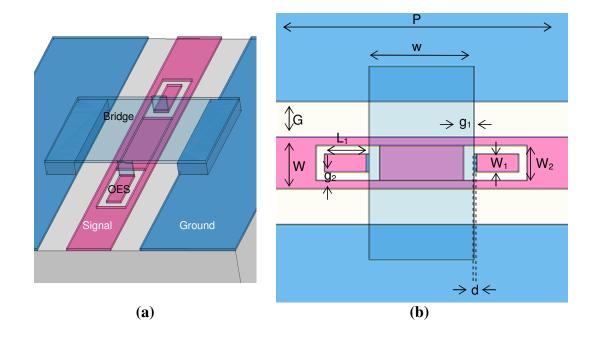

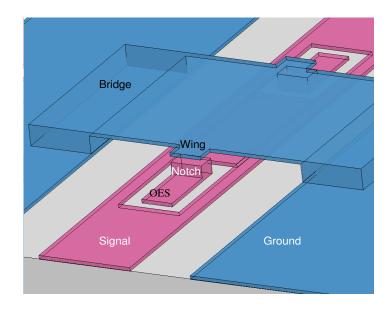

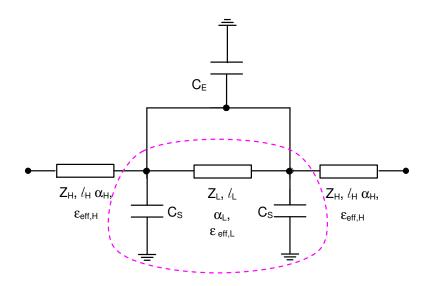

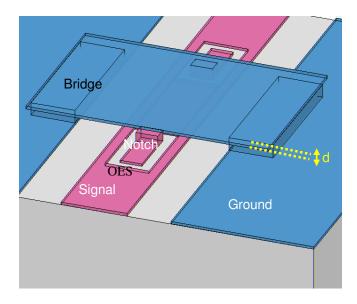

Figure 3.1 (a) Top view of one of the DMTL unit sections, where  $w > 50\mu m$ . (b) Lumped-element CLR model of the unit section of DMTL [7].(c) Low-impedance transmission line represented MEMS bridge model of the unit section of DMTL [29]

## 3.1.1. Theoretical Explanation the Proposed HICAPLO Model and Extraction of the Model Parameters

In the *CLR* model, the DMTL unit section is modeled by two short sections of highimpedance transmission lines and a lumped CLR model of the bridge [45] as Figure 3.1 (a) and (b) shows. The transmission line sections are of length P/2=(w/2) + l,

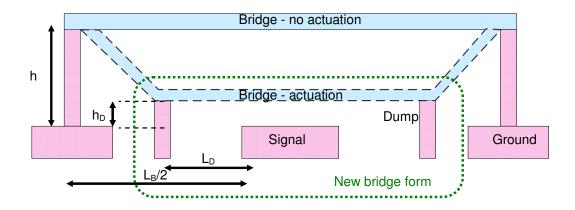

where l is the distance from the reference plane to the edge of the MEMS bridge. The *CLR* model is discussed to be valid up to a bridge width of about 50  $\mu$ m [29]. This means that the transmission line sections can be at most  $(50/2) + l = 25 + l \mu m$ long for the CLR circuit model to be valid (Figure 3.2). Therefore, for a structure having a bridge width, w, equal to 50  $\mu$ m, the bridge and the unloaded part of the structure can be modeled by two high-impedance transmission lines of length  $25+l \mu m$  and the lumped CLR model of a 50  $\mu m$  long bridge. Next, a structure having a bridge width w larger than 50 µm should be examined. Here,, 50 µm long part of the bridge (25µm from left and 25 µm from right) and the unloaded part of the structure can be modeled by two high-impedance transmission lines of length 25+lµm and the shunt capacitance of a 50 µm long bridge. To model the remaining (w-50) µm long loaded part, a low-impedance transmission line is employed in between the high impedance lines. The lumped capacitance representing the 50 µm portion of the bridge is divided into two parts each of which models 25 µm wide bridges. These parts are distributed around the low impedance line. Therefore, the improved model appear to consist of high- and low-impedance transmission lines, and shunt capacitances in between as shown in Figure 3.4.

Figure 3.2 Two unit DMTL structures; one with bridge width smaller than 50  $\mu$ m and the other with bridge width larger then 50  $\mu$ m.

Figure 3.3 (a) S-parameter comparison of HFSS EM simulation and the *CLR* model of a DMTL structure with bridge width 230 and signal line width 225  $\mu$ m.

Figure 3.4. The proposed circuit model for the unit DMTL section, where the MEMS bridges are represented by using both low-impedance transmission lines and the *CLR* model.

### 3.1.1.1. High-impedance and Low-impedance Transmission Line Parameters

The high-impedance line parameters (characteristic impedance  $Z_{H}$ , effective permittivity  $\varepsilon_{eff,H}$ , line loss  $\alpha_{H}$ ) are calculated using the CPW formulation in (2.1)-(2.4). For the calculation of the low-impedance line parameters ( $Z_L$ ,  $\varepsilon_{eff,L}$ ) representing the (w-50) µm long (where w is the width of the bridge) MEMS bridge, micro-strip line (MS) formulations (2.5)-(2.7) are used. As discussed in CHAPTER II, if the top cover is far away from the bottom plate, CPW with a top cover can be modeled using micro-strip line formulations as a limiting case. For the situation in DMTL case, the bridges can be thought as top covers and again micro strip line assumptions can be followed. However, for this case,  $\varepsilon_r$  will be 1 in equation (2.5) since top cover will be closer to the CPW transmission line compared to the bottom plate.